RCC(reset clock controller)复位和时钟控制器

RCC通过对晶振时钟进行分频倍频后,提供时钟给总线和外设工作使用;

所有的外设在使用前都需要先确保该外设的时钟被使能,这样每个时钟源都可以单独开关来优化功耗;

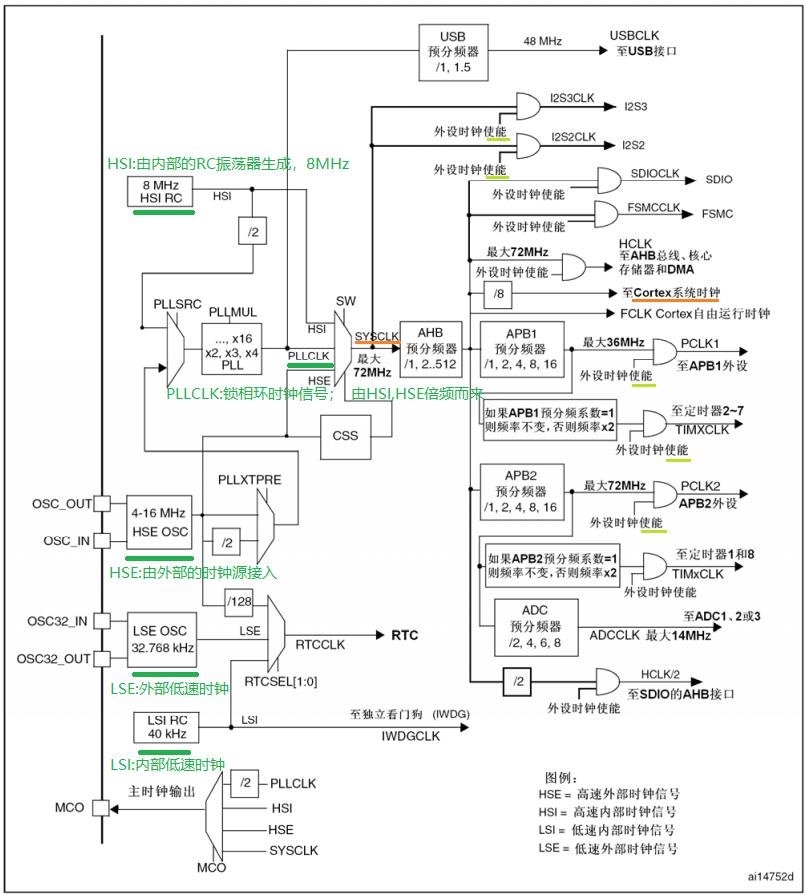

为了方便理解和查询RCC的功能,参考手册将RCC的功能描绘成了时钟树;

以下主要是stm32h7和stm32f1的时钟树的大致说明;

1 stm32f1的时钟树

1.1 时钟树对RCC控制器的功能进行了树形描述,时钟来源主要有4个,分别是HSI, HSE, LSI, LSE;图中分别用绿色横线标注出;橙色为系统时钟;

以系统时钟sysclk举例可知,sysclk时钟可以通过HSI,HSE或PLLCLK生成,其中PLLCK由HSI或HSE分频倍频而来;

1.2 AHB预分频后的时钟APB1,APB2为外设时钟,具体连接的外设如下所示;

2 stm32h7的时钟树

2.1 时钟树

时钟树是对RCC功能的树形总结,RCC一共有6个晶振来源如图绿色所示,所谓时钟输入频率;

以系统时钟sys_clk举例,晶振时钟通过PLLSRC选择后,首先被DIVM1分频,然后倍频DIVN1,然后再分频DIVP1,输出pll1_p_ck作为系统时钟选择器的输入;

IWDG1独立看门狗时钟由32KHz的LSI内部晶振提供时钟;RTC的时钟通常由32.768KHz的LSE外部晶振提供;

2.2 PLL锁相环

RCC一共3个PLL锁相环,PLL1生成系统时钟和部分外设时钟,PLL2生成外设时钟;主要知道如何配置分频倍频参数,然后输出3路pll分频时钟就差不多了;

从晶振出来的时钟频率经过PLLSRC选择后,再输入DIVMx分频,然后在PLL锁相环内倍频DIVNx,再分频DIVPx;输出3个pllx_x_ck;

其中pll1_p_ck为2.1时钟树中标出的黄色部分,可以作为系统时钟sys_ck的输入频率;通常取值如下:

取值PLLSRC选择25MHz的HSE,DIVM1预分频器配置5分频,DIVN1环分频器配置为倍频160倍;DIVP1后分频器2分频;pll1_p_ck为400MHz;

2.3 系统时钟生成单元SCGU

系统时钟生成单元的作用是什么呢?概括而言就是将系统时钟sys_ck经过分频倍频后,输出时钟给外设使用;

sys_ck为400MHz时,通常取值为D1CPRE(1)1分频,然后HPRE(1)2分频,D1PPRE(1)2分频,得到部分AHB3外设时钟为100MHz;

3 小结

对于芯片而言,能正常工作的前提就是时钟的稳定,所以时钟配置十分重要也较为常见;

通过分析时钟树的逻辑,可以对需要配置的外设或时钟总线的配置原理有一个大概的方向;

对原理有所了解之后再分析网络上的参考代码,比较容易理解人家为什么这么写,然后悟出自己应该怎么修改;

如果对时钟树不理解,就直接分析总线的分频配置代码就容易一团雾水不知所云;

嵌入式底层编程就是这样子把,编程基本使用原厂的库,主要是配置各种参数,需要了解各种外设和总线的配置;逻辑编程反倒没那么重要;

当然啦,我只是说底层编程逻辑不重要,并不是说编程逻辑不重要;