以下内容均以Xilinx的Nexys3作为开发板

1. UART简介

UART(即Universal Asynchronous Receiver Transmitter 通用异步收发器)是广泛使用的串行数据传输协议。UART允许在串行链路上进行全双工的通信。

串行外设用到RS232-C异步串行接口,一般采用专用的集成电路即UART实现。如8250、8251、NS16450等芯片都是常见的UART器件,这类芯片已经相当复杂,有的含有许多辅助的模块(如FIFO),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

以上内容摘自某位网友的热心博文。

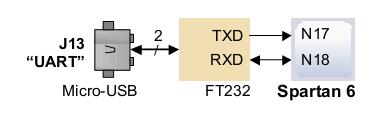

就我个人而言,UART就是一个异步串行接口,见过最多的就是RS232。而我们的开发板则是一个Mircro USB来模拟这样一个接口,电路图如下:

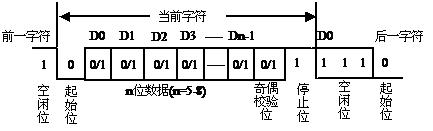

根据manual的介绍,我们可以通过指令来通过这个接口首发数据。Mircroblaze提供了这一接口的控制器,官网上也有着一接口的VHDL语言Demo。所以原理内容本人就不再赘述,主要还是注意串行异步通信协议,如下图所示。

道理很简单,但是这个Demo笔者却研究了很久时间,因为我一直使用Verilog语言,VHDL语言和Verilog区别还是挺大的,为了方便其他使用Verilog研究本Demo,笔者现将Xilinx网站上的GPIO_UART Demo改写为Verilog。

该Demo采用单工方式,开发板最为发送器,PC最为接收器。同时,该Demo还兼具了按键消抖,7段数码管显示等模块,笔者也进行了改写,但此处不做详细介绍。

由于该源代码注解较为详细,现仅将功能介绍:其实由switch控制led显示,同时switch[0]作为系统复位端。五个按键的中间按键也可作为复位端。程序烧录后,启动系统,系统将自动向PC发送27个16位字符串;当按其他按键时,开发板也将向PC发送24个16位字符串。字符串内容相同,但数据不同。其中笔者认为该程序按键消抖部分不是很好,但是本人并未修改,毕竟只是改写人家的源代码。Xilinx官网的大部分都是VHDL程序,看起来真的是很费力,希望对感兴趣的同学有帮助吧。

2.程序源代码介绍

其中,笔者使用IPcore生成rom,按键发送和初始发送的数据内容相同,但长度不同,作为测试依据。源码打包在最后面。

3.实验截图

(1)状态机截图

图1 顶层文件状态机

图2 子层状态机

(2)测试截图

验证工具为网上下载的小工具——串口调试器。打开该工具前需要保证开发板已经与PC相连,否则无法找到串口COM3。测试前,别忘记将选择串口选为COM3,波特率9600,数据位8,校验位无,停止位1,单击打开串口即可测试。如图。

4.附件

(1)源代码