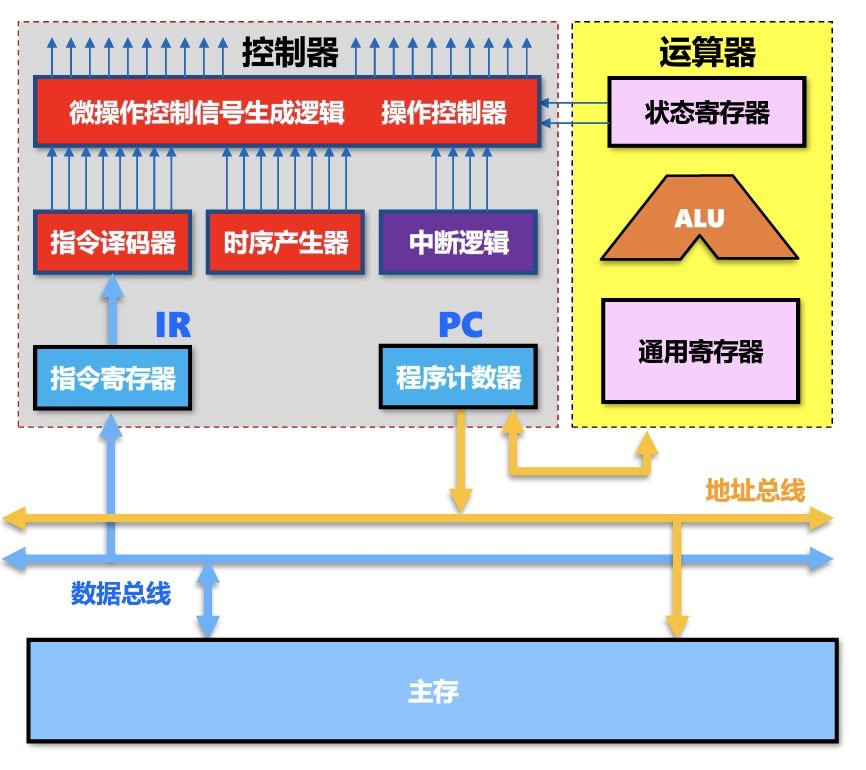

CPU的组成与功能

数据通路

- 概念:执行部件间传送信息的路径,分共享通路(总线)和专用通路

- 抽象模型:时钟驱动下,A --> 组合逻辑 --> B

- D触发器定时模型:

- 时钟触发前要稳定一段时间:建立时间(Setup Time)

- 时钟触发后要稳定一段时间:保持时间(Hold Time)

- 时钟触发到输出稳定的时间:触发器延迟(Clk_to_Q)

- 与时钟周期的关系:

- 时钟周期 > Clk_to_Q + 关键路径时延 + Setup Time

- Clk_to_Q + 最短路径时延 > Hold Time

指令周期

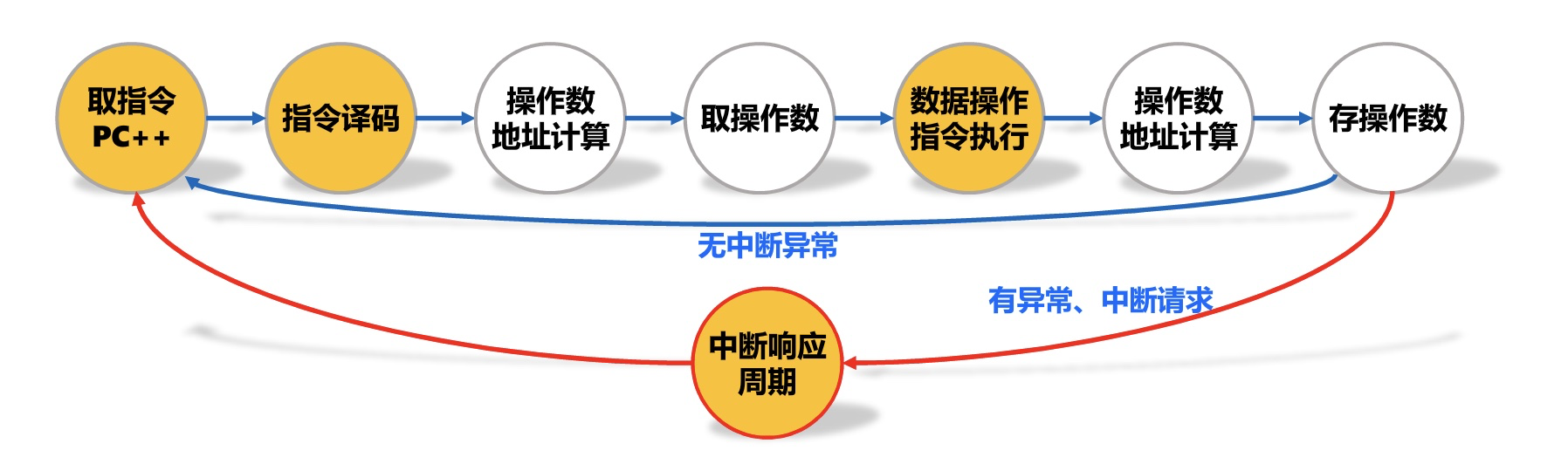

指令执行的一般流程

- 基本概念

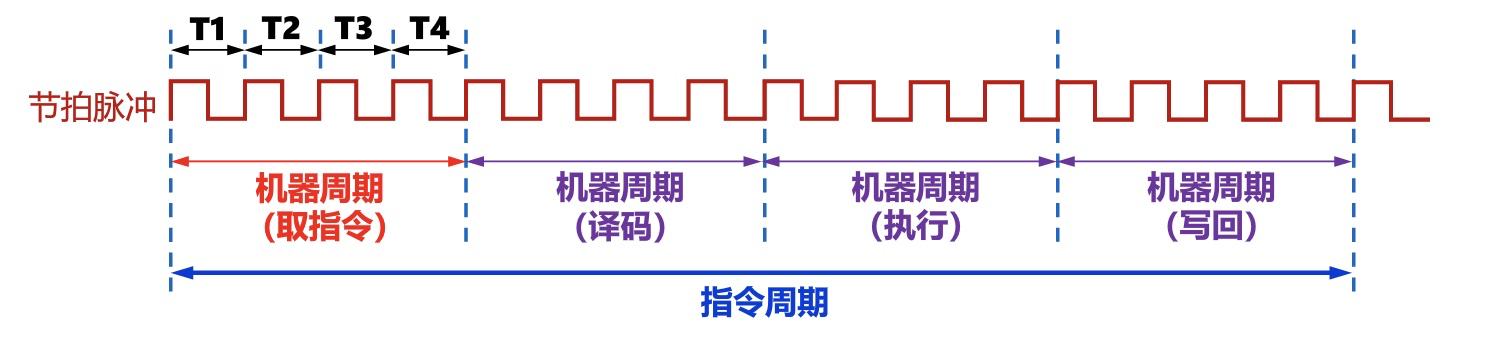

- 时钟周期 = 节拍脉冲 = 震荡周期

- 机器周期 = CPU 周期 = 从主存读取一条指令的最短时间

- 指令周期 = 从主存读指令并执行指令的时间

指令时间控制:

机器周期数 节拍数 同步方式 实践 定长指令周期 不变 不变 按机器周期 mips 单周期 变长指令周期 变 变 按时钟周期 mips 多周期

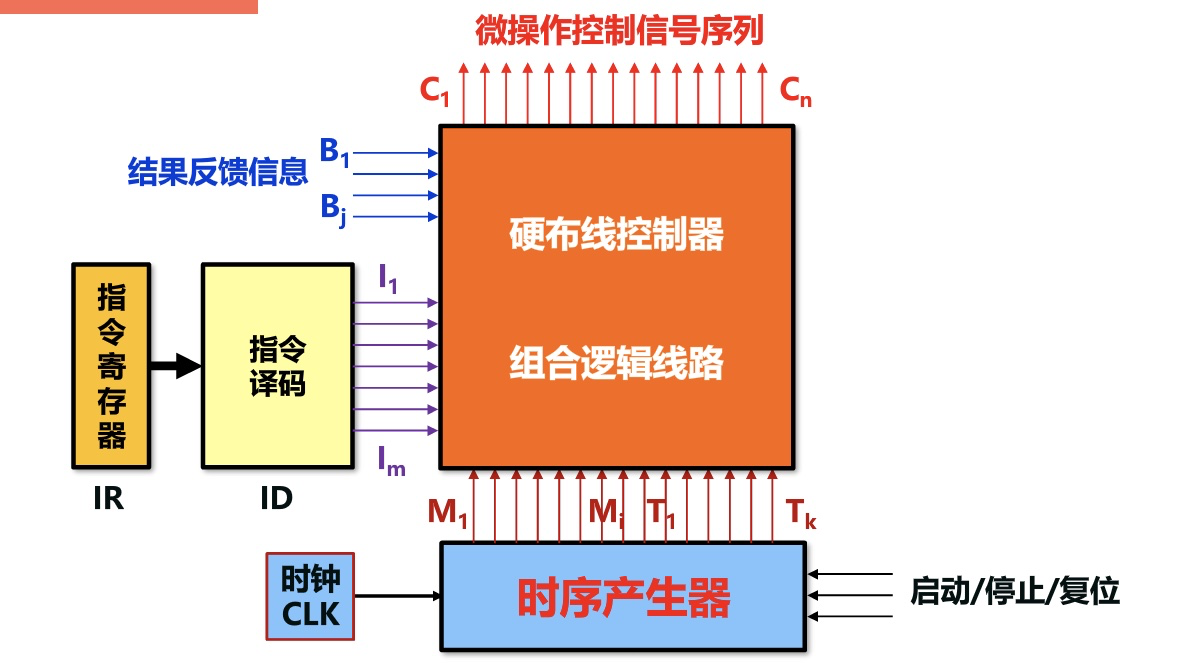

CPU设计

略,详情请参见《自制CPU系列》