SPI是串行外设接口(Serial Peripheral Interface)的缩写。是 Motorola 公司推出的一 种同步串行接口技

术,是一种高速的,全双工,同步的通信总线。SPI接口没有指定的流控制,没有应答机制确认是否接收到数

据。通常有以下4条通讯线。 同I2C接口相比,SPI器件支持更高的时钟频率。

时钟(SPI CLK, SCLK)

片选(CS)

主机输出、从机输入(MOSI)

主机输入、从机输出(MISO)

MOSI和MISO是数据线。MOSI将数据从主机发送到从机,MISO将数据从从机发送到主机。

数据传输

主从设备之间通过SPI进行通讯,主机必须发送时钟信号,并通过使能CS信号选择从机,而且两者之

间时钟SCLK要特性要匹配。SPI中的特性指的就是时钟的极性Polarity和相位Phase。

最常见的有以下写法:

(1) CKPOL (Clock Polarity) = CPOL = POL = Polarity = (时钟)极性

(2) CKPHA (Clock Phase) = CPHA = PHA = Phase = (时钟)相位

SCK、SCLK、CLK指的是时钟脉冲, Edge指的是时钟脉冲的边沿,即时钟电平变化的时刻,即上升

沿(risingedge) 或者下降沿(falling edge)。

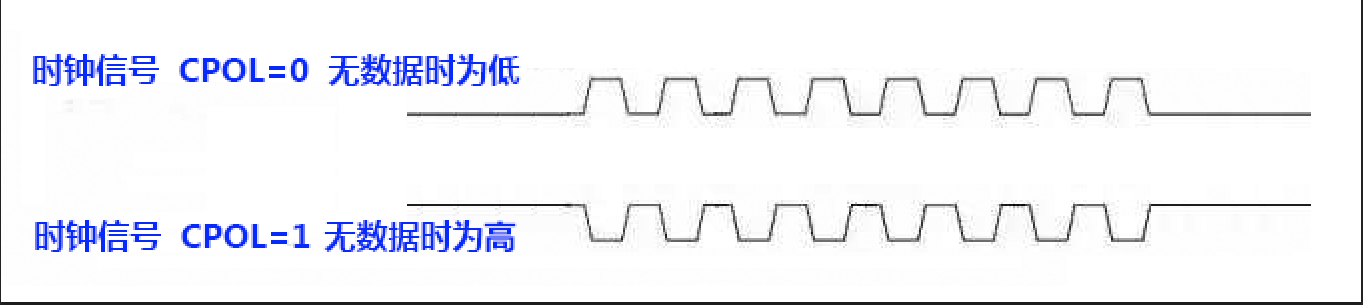

CPOL设置

CPOL可以软件设置为0或1,什么意思尼?我们知道当要有数据传输时才有CLK时钟脉冲输出,内么

没有CLK时钟输出时,MCU的CLK脚是个神马状态尼?这个是可以软件设定的:

设 CPOL=0 效果是没有CLK时钟输出时MCU的CLK脚为低电平

设 CPOL=1 效果是没有CLK时钟输出时MCU的CLK脚为高电平

如下图:

CPHA设置

数据相位CPHA说的是时钟的有效的时刻。在时钟的神马时刻去读写数据是有效的。我们知道一个脉冲

有2个边沿和中间保持区,那么数据采样是在第几个边沿(edge)是有效的就用到CPHA设置。于是乎就龟腚:

设 CPHA=0 表示第1个边沿采集、下个沿移出数据。

设 CPHA=1 表示第2个边沿采集、下个沿移出数据。

结合上面CPOL的设置来说。

当CPOL=0: 起始电平为低,那么第1沿个肯定是上升沿,然后保持高、接着第2个沿是下降沿、然后保持低,

再接着第3个沿又是上升沿,然后周而复始。

这样对于CPHA=0,采集用的第1沿是上升沿、移出数据用的第2沿是下降沿,龟腚为SPI的模式0

CPHA=1,采集用的第2沿是下降沿、移出数据用的第3沿是上升沿,龟腚为SPI的模式1

可以看出SPI的模式0比模式1早一个相位(脉冲)。

当CPOL=1: 起始电平为高,那么第1沿个肯定是下降沿,然后保持低、接着第2个沿是上升沿、然后保持高,

再接着第3个沿又是下降沿,然后周而复始。

这样对于CPHA=0,采集用的第1沿是下降沿、移出数据用的第2沿是上升沿,龟腚为SPI的模式2

CPHA=1,采集用的第2沿是上升沿、移出数据用的第3沿是下降沿,龟腚为SPI的模式3

可以看出SPI的模式2比模式3早一个相位(脉冲)。

来个图说明下:

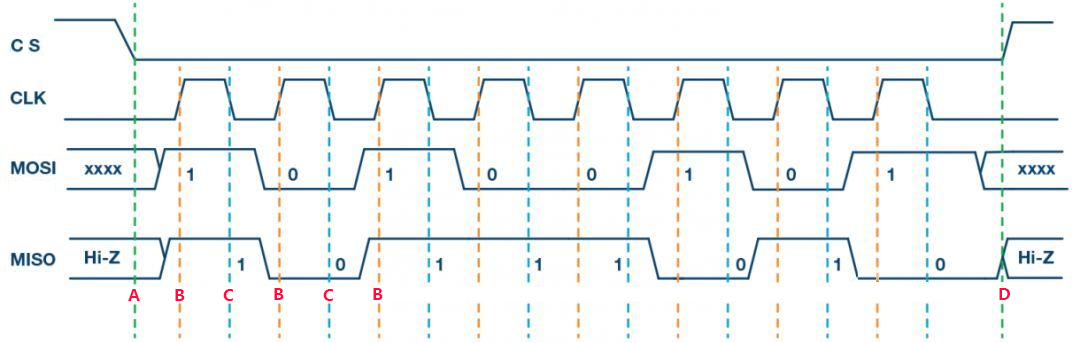

再举个例子:

以SPI模式0为例看下图,数据显示在MOSI和MISO线上。传输的开始和结束用绿色虚线表示,采样

边沿用橙色虚线表示,移位边沿用蓝色虚线表示。

可以看出模式0 CPOL = 0,CPHA = 0:CLK空闲状态为 低电平,数据在B处上升沿采样,并在C处下降

沿移出。注意上图的采样和移出,说的是:

主机MCU在MISO线发出数据,从机设备在MISO线采样和移出数据

主机MCU在MOSI线采样和移出数据,从机设备在MOSI线发出数据

所谓采样、移出并不是说删除数据,而应理解为读取可以看到在A、B处的MOSI、MISO数据都是处于持续

稳定的一个状态。SPI模式1、SPI模式2、SPI模式3的时序图以此类推。

划重点:无论设置SPI模式0、1、2、3的哪一种,主从设备必须设为同一种模式。

对于从设备也是MCU自然可以软件设置SPI模式,但对于像W25Q128FV这种内部没有处理器,脚位又少的

简单外设又怎么来设置SPI模式尼?

是这样滴,W25Q128FV通过芯片内部逻辑可以自动识别SPI模式0、3,模式1、2是不支持滴。

逻辑的判断条件是:

在/CS上升沿和下降沿时刻,CLK是低电平,判断为模式0;

在/CS上升沿和下降沿时刻,CLK是高电平,判断为模式3;

这样我们在MCU设置好SPI模式0或3后,就可以直接和W25Q128FV进行通讯了。