OCV,On_Chip_Variation

PVT,Process,Voltage,Temperature。

PVT三者相互组合就形成了如下的Senario。对应的解释如下。

WC:worst case slow,低电压,高温度,慢工艺 -> 一般情况下delay最大,setup 差。

WCL:worst case low-temperature,低电压,低温度,慢工艺 -> 温度反转效应时delay最大,setup差。

LT:即low-temperature,也叫bc(best case fast),高电压,低温度,快工艺 -> 一般情况下delay最小,hold差。

ML:max-leakage,高电压,高温度,快工艺 -> 温度反转效应下delay最小,hold差。

TC:typical,也叫tt,普通电压,普通温度,标准工艺 -> 各种typical。

BC:Best case。高电压,快工艺,常温0℃ or 25℃。

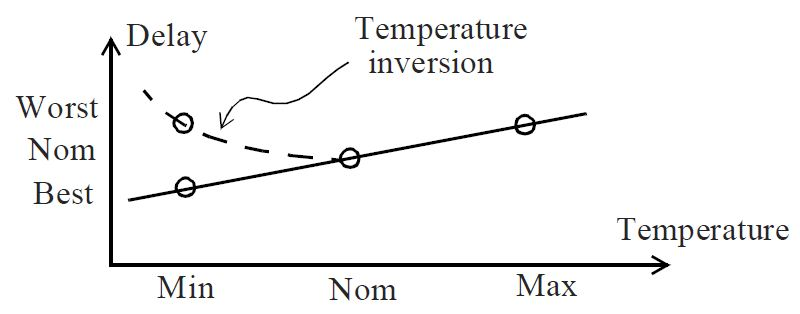

温度反转效应

简单来说,工艺在90nm以上的时候,随着温度的升高,delay增大,所以worst corner是PVTmax,但是65nm以下,随着温度的降低,delay增大,worst corner可能是PVTmax,也可能是PVTmin,这就是温度反转效应(Temperature Inversion Effect)。下面简单描述下低温对delay是如何影响的。

对Transistors的影响:低温时,迁移率增大(导致快switching趋势),但是Vt增大(导致慢switching趋势),最后结果取决于迁移率和Vt谁起更重要作用。

对寄生参数的影响:低温时,wire电阻更低。

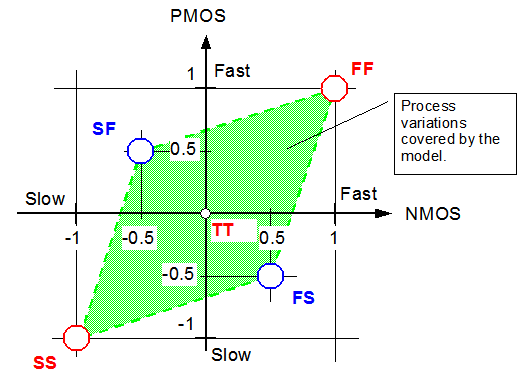

Mos管的参数,因为制造工艺的原因(温度,湿度,在晶元的不同位置),会有一个偏差的范围(部分参数如参杂浓度离正常值偏差达到3或者6个σ)(电容电阻也是一样)。在数字电路设计中(模电不用),这些参数的影响要被考虑在内。我们想一块晶圆的产量尽可能高,那么就要求我们的设计对于不同参数的晶体管有一定的健壮性,也就是说对Mos管参数的容限要尽可能大。而Process Corner就是晶元的参数范围, 由Foundry提供。

为了测试设计的健壮性,Foundry会提供Corner Lots给设计师,它们就是一系列经过预处理的Wafer,这些Wafer都是预置了不同的偏差。通俗的话来说,正常生产用的Wafer性能会有一个范围,为了保证设计在这些范围内还能正常工作,Foundry提供了一些极端的Wafer,如果在这些极端的Wafer上做的设计都能正常工作,那么正常Wafer也就比较稳了。

所谓不同的Corner代表了不同的偏差类型,一般用两位字母标识,第一个是Noms,第二个是Pmos。每一位有两种情况,F和S,代表翻转速度/延迟(准确来说是电子在电场力作用下通过金属和半导体的速率,Electron Mobility,载流子迁移率)。

- FF

- SF

- SS

- FS

- TT(Typical Typical)严格来说不算Corner

TT、FF、SS被叫做Even Corner,FS和SF被叫做Skewed Corners,这个比较重要,因为两边速度相差很远,那么两个翻转沿的Slew也会相差很大。

同样,工艺库里也有不同的Cell,大致可以分为HVT,SVT/RVT,LVT。根据不同的阈值电压(通常将传输特性曲线中输出电压随输入电压改变而急剧变化转折区的中点对应的输入电压称为阈值电压)来区分。H高,L低,S中等(standard/Regular)。L的速度快,但是功耗高(电压低了怎么功耗还高了?电压低对于动态功耗当然是个好事,但是这个单元的漏电也很高,和频率是对数关系,也就是说,漏电每增加10倍,最高频率才增加log10%。(此处存疑)截止电流小), HS同理。在不同的区域合理使用不同Cell才能达到预期的设计效果。

Performance!Usage!Power_Consumption!