本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。

适用于板卡型号:

PGL22G/PGL12G

1. 实验简介

本实验练习使用ADC,实验中使用的ADC模块型号为AN9238,最大采样率65Mhz,精度为12位。实验中把AN9238的2路输入以波形方式在HDMI上显示出来,我们可以用更加直观的方式观察波形,是一个数字示波器雏形。

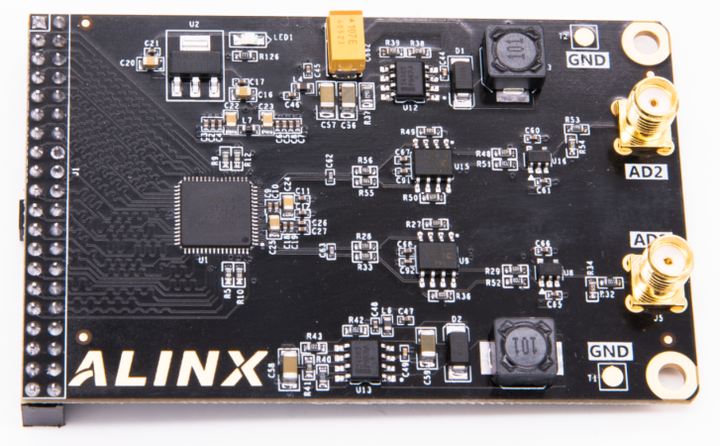

AN9238双路65M采样12位ADC模块

AN9238双路65M采样12位ADC模块 实验预期结果

实验预期结果

2. 实验原理

黑金高速AD模块AN9238为2路65MSPS, 12位的模拟信号转数字信号模块。模块的AD转换采用了ADI公司的AD9238芯片, AD9238芯片支持2路AD输入转换,所以1片AD9238芯片一共支持2路的AD输入转换。模拟信号输入支持单端模拟信号输入,输入电压范围为-5V~+5V,接口为SMA插座。

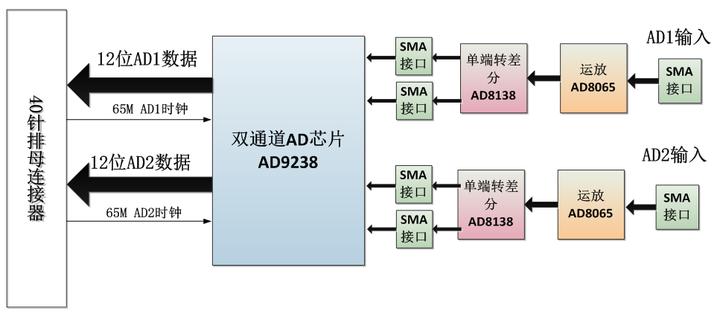

AN9238模块的原理设计框图如下:

关于AD9238的电路具体参考设计请参考AD9238的芯片手册。

2.1 单端输入及运放电路

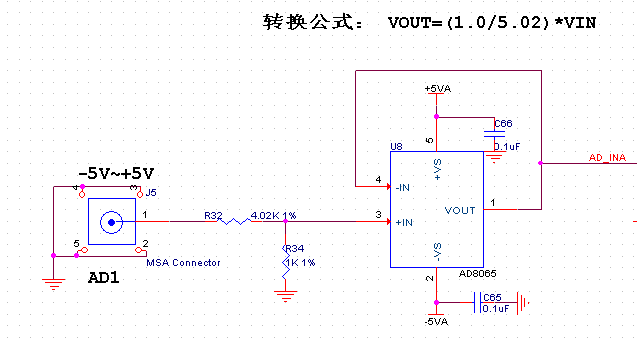

单端输入AD1和AD2通过J5或者J6两个SMA头输入,单端输入的电压为-5V~+5V。

板上通过运放AD8065芯片和分压电阻把-5V~+5V输入的电压缩小成-1V~+1V。如果用户想输入更宽范围的电压输入只要修改前端的分压电阻的阻值。

下表为模拟输入信号和AD8065运放输出后的电压对照表:

| AD模拟输入值 | AD8065运放输出 |

| -5V | -1V |

| 0V | 0V |

| +5V | +1V |

2.2 单端转差分及AD转换

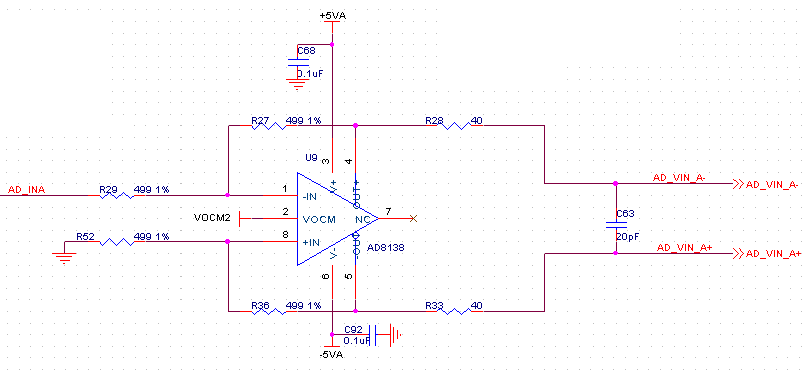

-1V~+1V的输入电压通过AD8138芯片转换成差分信号(VIN+ − VIN−), 差分信号的共模电平由AD的CML管脚决定。

下表为模拟输入信号到AD8138差分输出后的电压对照表:

| AD模拟输入值 | AD8065运放输出 | AD8138差分输出(VIN+−VIN−) |

| -5V | -1V | -1V |

| 0V | 0V | 0V |

| +5V | +1V | +1V |

2.3 AD9238转换

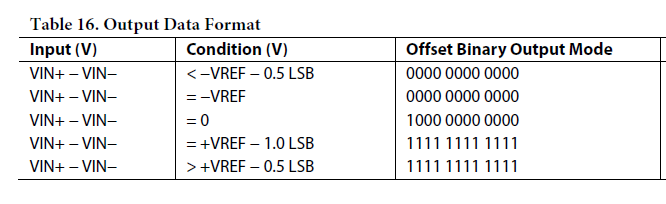

默认AD是配置成offset binary的,AD转换的值如下图所示:

在模块电路设计中,AD9238的VREF的值为1V,这样最终的模拟信号输入和AD转换的数据如下:

| AD模拟输入值 | AD8055运放输出 | AD8138差分输出(VIN+−VIN−) | AD9238数字输出 |

| -5V | -1V | -1V | 000000000000 |

| 0V | 0V | 0V | 100000000000 |

| +5V | +1V | +1V | 11111111111 |

从表中我们可以看出,-5V输入的时候,AD9238转换的数字值最小,+5V输入的时候,AD9238转换的数字值最大。

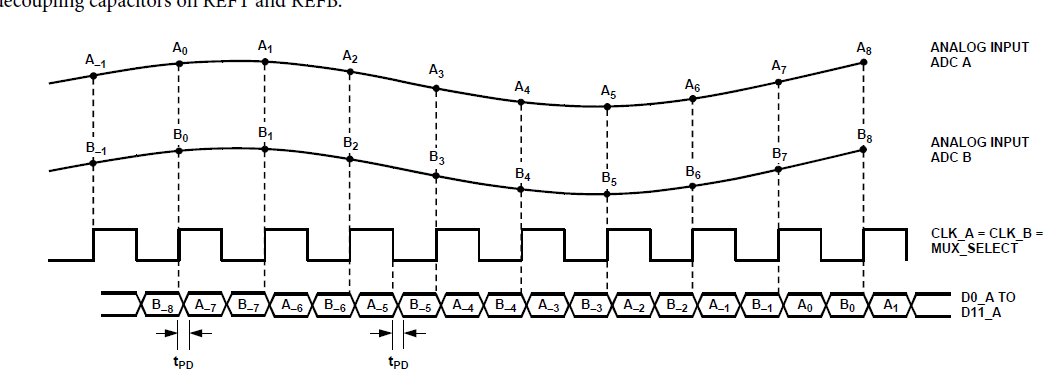

2.4 AN9238数字输出时序

AD9238双通道AD的数字输出为+3.3V的CMOS输出模式,2路通道(A和B)独立的数据和时钟。AD数据在时钟的上降沿转换数据,FPGA端可用AD时钟的采样AD数据。

3. 程序设计

本实验显示部分是基于前面的已有的实验,在彩条上叠加网格线和波形。

timing_gen_xy模块完成视频图像的坐标生成,x坐标,从左到右增大,y坐标从上到下增大。

| 信号名称 | 方向 | 宽度(bit) | 说明 |

| clk | in | 1 | 系统时钟 |

| rst_n | in | 1 | 异步复位,低电平复位 |

| i_hs | in | 1 | 视频行同步输入 |

| i_vs | in | 1 | 视频场同步输入 |

| i_de | in | 1 | 视频数据有效输入 |

| i_data | in | 24 | 视频数据输入 |

| o_hs | out | 1 | 视频行同步输出 |

| o_vs | out | 1 | 视频场同步输出 |

| o_de | out | 1 | 视频数据有效输出 |

| o_data | out | 24 | 视频数据输出 |

| x | out | 12 | 坐标x输出 |

| y | out | 12 | 坐标y输出 |

timing_gen_xy模块端口

grid_display模块主要完成视频的网格线叠加,本实验将彩条视频输入,然后叠加一个网格后输出,提供给后面的波形显示模块使用。

| 信号名称 | 方向 | 宽度(bit) | 说明 |

| pclk | in | 1 | 像素时钟 |

| rst_n | in | 1 | 异步复位,低电平复位 |

| i_hs | in | 1 | 视频行同步输入 |

| i_vs | in | 1 | 视频场同步输入 |

| i_de | in | 1 | 视频数据有效输入 |

| i_data | in | 24 | 视频数据输入 |

| o_hs | out | 1 | 带网格视频行同步输出 |

| o_vs | out | 1 | 带网格视频场同步输出 |

| o_de | out | 1 | 带网格视频数据有效输出 |

| o_data | out | 24 | 带网格视频数据输出 |

grid_display模块端口

wav_display显示模块主要是完成波形数据的叠加显示,模块内含有一个双口ram,写端口是由ADC采集模块写入,读端口是显示模块。

| 信号名称 | 方向 | 宽度(bit) | 说明 |

| pclk | in | 1 | 像素时钟 |

| rst_n | in | 1 | 异步复位,低电平复位 |

| wave_color | in | 24 | 波形颜色,rgb |

| adc_clk | in | 1 | adc模块时钟 |

| adc_buf_wr | in | 1 | adc数据写使能 |

| adc_buf_addr | in | 12 | adc数据写地址 |

| adc_buf_data | in | 8 | adc数据,无符号数 |

| i_hs | in | 1 | 视频行同步输入 |

| i_vs | in | 1 | 视频场同步输入 |

| i_de | in | 1 | 视频数据有效输入 |

| i_data | in | 24 | 视频数据输入 |

| o_hs | out | 1 | 带网格视频行同步输出 |

| o_vs | out | 1 | 带网格视频场同步输出 |

| o_de | out | 1 | 带网格视频数据有效输出 |

| o_data | out | 24 | 带网格视频数据输出 |

wav_display模块端口

ad9226_sample模块主要完成ad9226输入数据顺序调整,因为ad9226输入的数据MSB在最低位。再把有符号数转换为无符号数,最后位宽转换到8bit。

| 信号名称 | 方向 | 宽度(bit) | 说明 |

| adc_clk | in | 1 | adc系统时钟 |

| rst | in | 1 | 异步复位,高复位 |

| adc_data | in | 12 | ADC数据输入,MSB在最低位,需要倒序 |

| adc_buf_wr | out | 1 | ADC数据写使能 |

| adc_buf_addr | out | 12 | ADC数据写地址 |

| adc_buf_data | out | 8 | 无符号8位ADC数据 |

ad9226_sample模块端口

4. 实验现象

1)将AN9238模块插入开发板的扩展口J8,注意1脚对齐,不要插错、插偏,不能带电操作。

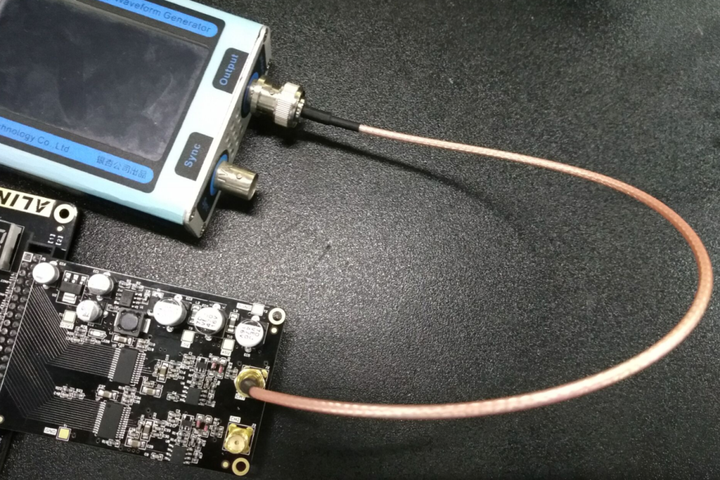

2)连接AN9238的输入到信号发生器的输出,这里使用的是专用屏蔽线,如果使用其他线可能会有较大干扰。

AN9238连接信号源示意图

AN9238连接信号源示意图

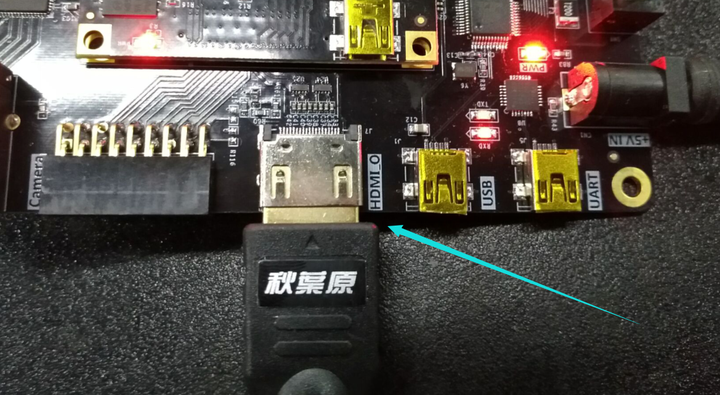

3)连接HDMI显示器,注意:连接的是显示器,不是笔记本电脑HDMI接口

HDMI接口连接示意图

HDMI接口连接示意图

4)下载程序,调节信号发生的频率和幅度,AN9238输入范围-5V-5V,为了便于观察波形数据,建议信号输入频率200Khz到1Mhz。观察显示器输出,红色波形为AD1输入、蓝色为AD2输入、黄色网格最上面横线代表5V,最下面横线代表-5V,中间横线代表0V,每个竖线间隔是10个采样点。