原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处(http://www.alinx.com)。

适用于板卡型号:

PGL22G/PGL12G

1. 文档简介

很多初学者看到板上只有一个50Mhz时钟输入的时候都产生疑惑,时钟怎么才50Mhz?如果要工作在100Mhz、150Mhz怎么办?在很多FPGA芯片内部都集成了PLL,其他厂商可能不叫PLL,但是也有类似的功能模块,通过PLL可以倍频分频,产生其他很多时钟。本实验通过调用PLL ip core来学习PLL的使用方法。

2. 实验环境

- Windows 10 64位

- View RTL Schematic(Pango Design Suite 2020.3)

- 示波器

- 开发板

3. 实验原理

PLL(phase-locked loop),即锁相环。是FPGA中的重要资源。由于一个复杂的FPGA系统往往需要多个不同频率,相位的时钟信号。所以,一个FPGA芯片中PLL的数量是衡量FPGA芯片能力的重要指标。FPGA的设计中,时钟系统的FPGA高速的设计极其重要,一个低抖动, 低延迟的系统时钟会增加FPGA设计的成功率。

本实验将通过使用PLL, 输出一个方波到开发板上的扩展口J8的PIN3脚,来给大家演示使用PLL的方法。

- 数字锁相环(PLL)

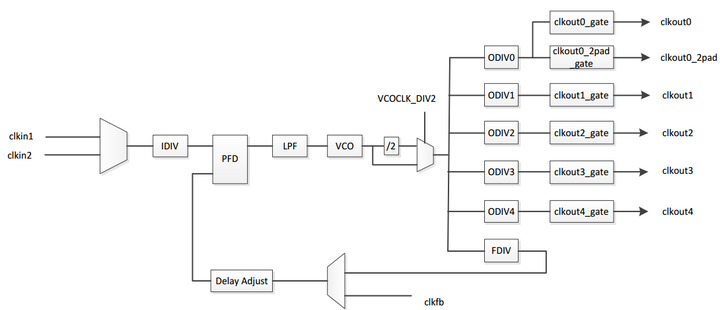

PLL内部的功能框图如下图所示:Logos PLL 主要由鉴频鉴相器(PFD,Phase Frequency Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator) 等组成。通过不同的参数配置,可实现信号的调频、调相、同步、频率综合等功能。 LogosPLL 的电路框图如下图所示:

想了解更多的时钟配置, 建议大家看看官方提供的文档" Logos 系列产品 PLL IP用户指南 "。

4. 建立工程

本实验中为大家演示如果调用PLL IP核来产生不同频率的时钟, 并把其中的一个时钟输出到FPGA外部IO上, 开发板J8的PIN3脚。

下面为程序设计的详细步骤。

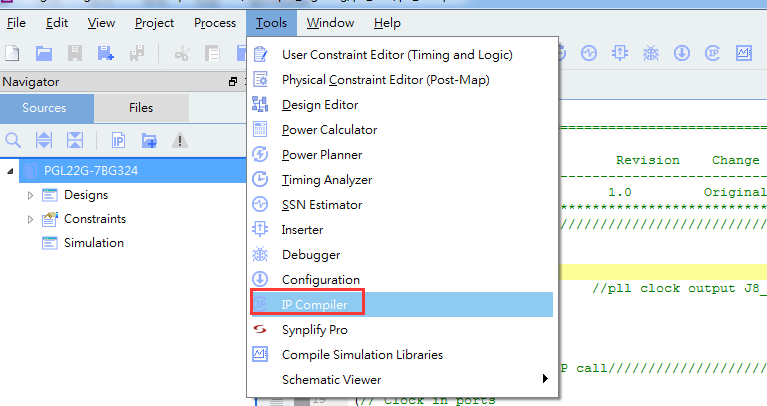

1. 新建一个pll_test的工程,点击Tool菜单下的IP Compiler。

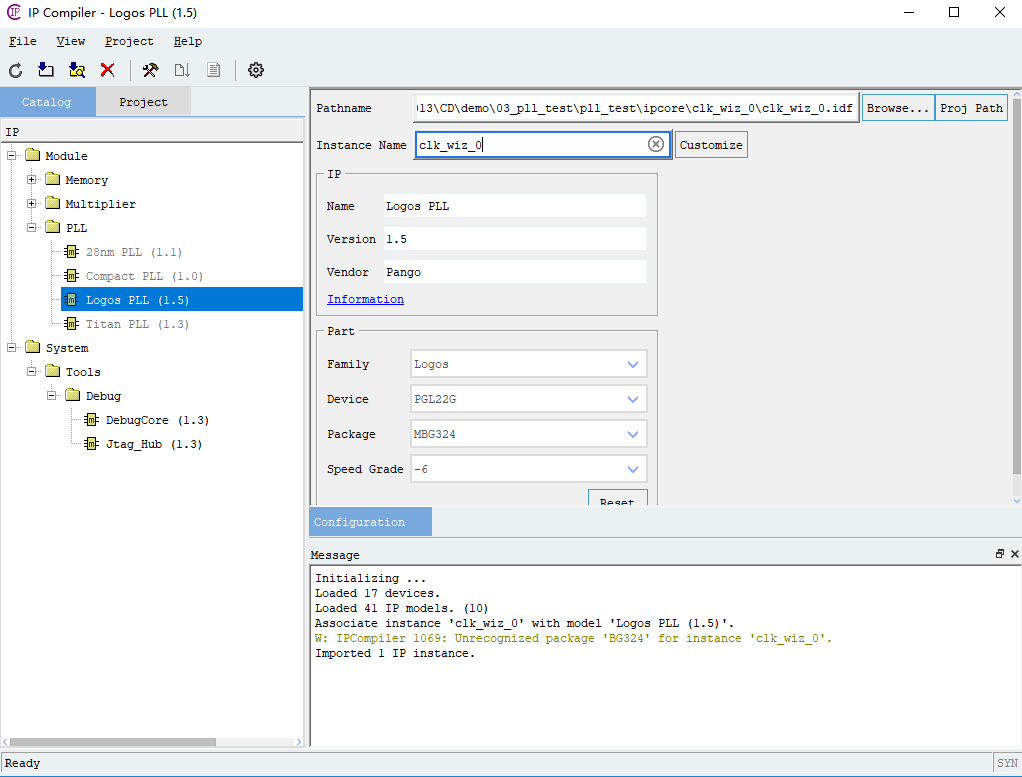

2. 再在弹出的界面里选择PLL下的Logos PLL,再对PLL取名clk_wiz_0,然后单击Customize。

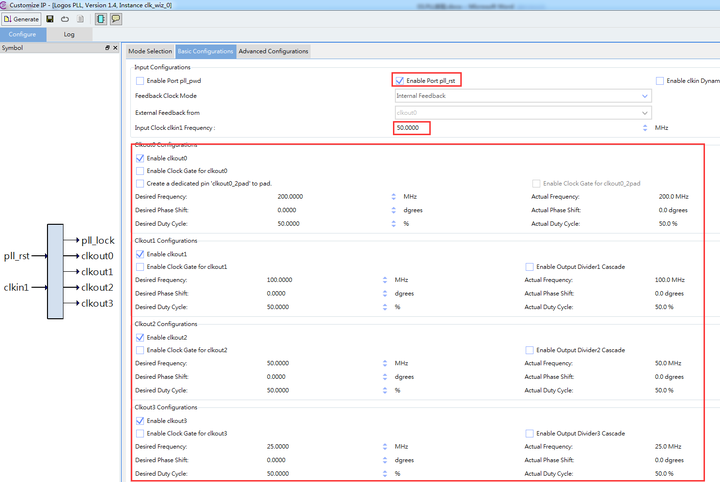

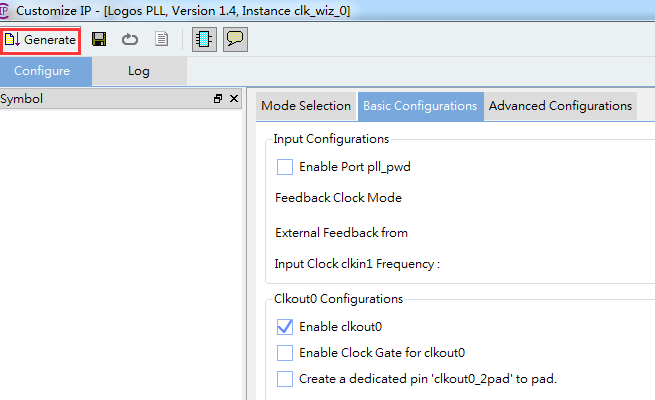

3. 在Basic Configurations界面里, 勾选复位管脚使能"Enable Port pll_rst",输入的时钟频率为50Mhz。输出选择clk_out0~clk_out3四个时钟的输出,频率分别为200Mhz, 100Mhz, 50Mhz, 25Mhz。这里还可以设置时钟输出的相位,我们不做设置,保留默认相位, 点击 OK完成,

5. 然后点击Generate按钮生成PLL IP的设计文件。

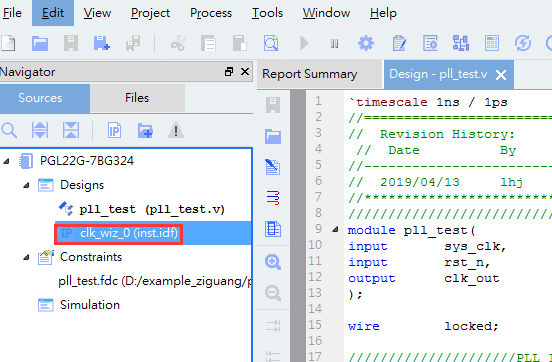

6. 这时一个 clk_wiz_0 IP会自动添加到我们的pll_test项目中, 用户可以双击它来修改这个IP的配置。

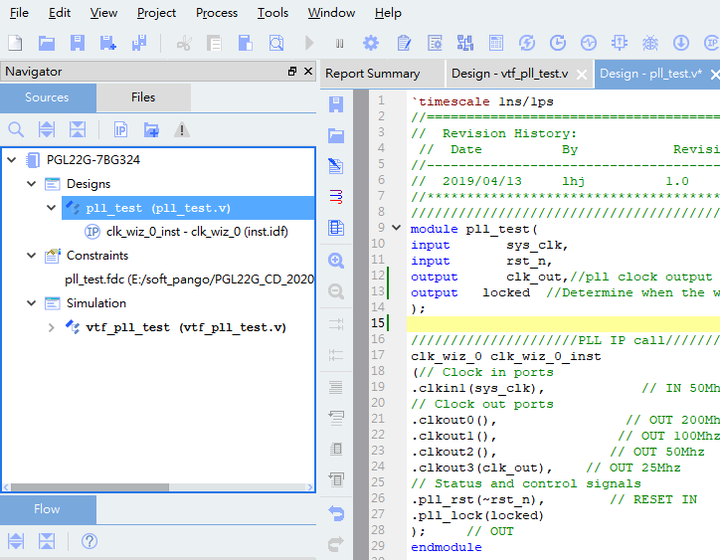

7. 我们再来编写一个顶层设计文件来实例化这个PLL IP, 编写pll_test.v代码如下。

`timescale1ns/1ps

//================================================================================

// Revision History:

// Date By Revision Change Description

//--------------------------------------------------------------------------------

// 2019/04/13 lhj 1.0 Original

//*******************************************************************************/

//////////////////////////////////////////////////////////////////////////////////

module pll_test(

input sys_clk,

input rst_n,

output clk_out,//pll clock output J8_Pin3

outputlocked

);

/////////////////////PLL IP call////////////////////////////

clk_wiz_0 clk_wiz_0_inst

(// Clock in ports

.clkin1(sys_clk),// IN 50Mhz

// Clock out ports

.clkout0(),// OUT 200Mhz

.clkout1(),// OUT 100Mhz

.clkout2(),// OUT 50Mhz

.clkout3(clk_out ),// OUT 25Mhz

// Status and control signals

.pll_rst(~rst_n),// RESET IN

.pll_lock(locked)

);// OUT

endmodule

程序中先用实例化clk_wiz_0, 把单端50Mhz时钟信号输入sys_clk到clk_wiz_0的clkin1,把clk_out3的输出赋给clk_out。

8. 保存工程后,pll_test自动成为了top文件,clk_wiz_0成为Pll_test文件的子模块。

9. 再为工程进行管脚约束,这里不做介绍,见教程《LED流水灯实验及仿真》中的内容。

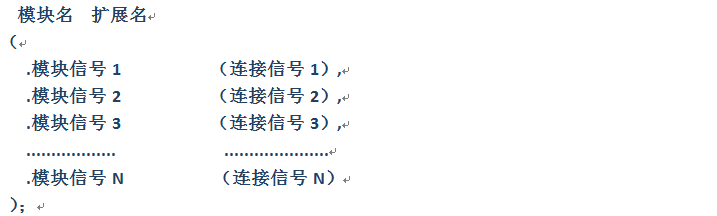

注意:例化的目的是在上一级模块中调用例化的模块完成代码功能,在Verilog里例化信号的格式如下:模块名必须和要例化的模块名一致,包括信号名也必须一致,模块与模块之间的连接信号不能相互冲突,否则会产生编译错误。

5. Modelsim 仿真PLL输出波形

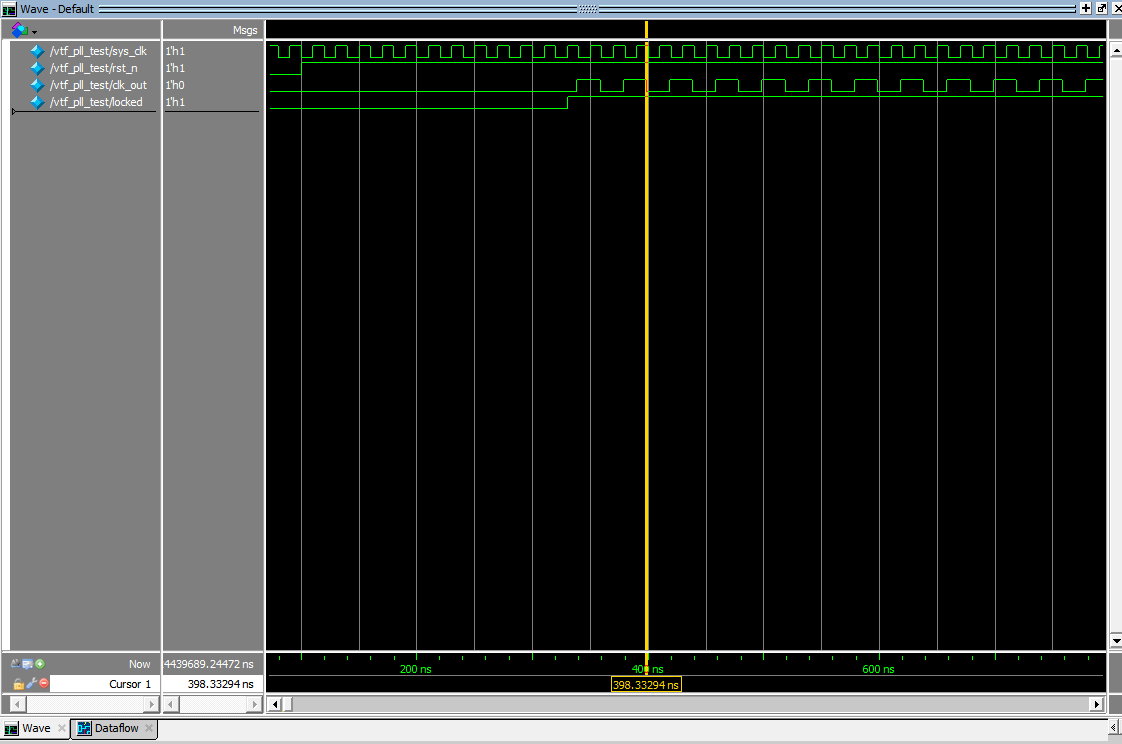

创建仿真文件vtf_pll_test.v文件,鼠标右键点击仿真文件,点击“run Behavior Simulation”会打开Modelsim软件进行波形仿真。仿真文件和仿真波形如图所示:

波形图中 sys_clk为50MHz的系统时钟,rst_n为复位信号,clk_out为PLL输出的25MHz,locked为波形稳定输出锁定。

6. 测量PLL输出波形

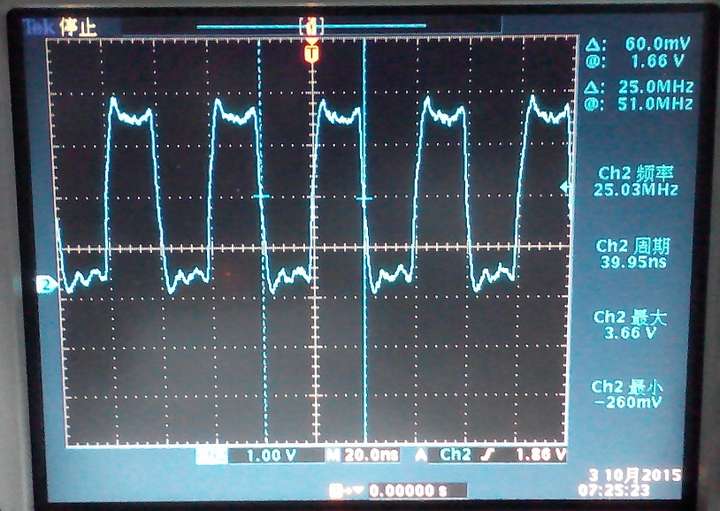

编译工程并生成pll_test.sbit文件,再把sbit文件下载到FPGA中,接下去我们就可以用示波器来测量输出时钟波形了。

用示波器探头的地线连接到开发板上的地(开发板J8的PIN1脚),信号端连接开发板J8的PIN3脚(测量的时候需要注意,避免示波器表头碰到其它管脚而导致电源和地短路)。

这时我们可以在示波器里看到25Mhz的时钟波形,波形的幅度为3.3V, 占空比为1:1,波形显示如下图所示:

如果您想输出其它频率的波形,可以修改时钟的输出为clk_wiz_0的clkout0或clkout1或clkout2。也可以修改clk_wiz_0的clkout3为您想要的频率,这里也需要注意一下,因为时钟的输出是通过PLL对输入时钟信号的倍频和分频系数来得到的,所以并不是所有的时钟频率都可以用PLL能够精确产生的,不过PLL也会自动为您计算实际输出接近的时钟频率。