从并行到串行:

PCI Express(又称PCIe)是一种高性能、高带宽串行通讯互连标准,取代了基于总线的通信架构,如:PCI、PCI Extended (PCI-X) 以及加速图形端口(AGP)。

PCI-e的主要性能:

-

-

更低的生产成本

-

更高系统吞吐量

-

更好可扩展性和灵活性

-

上述传统基于总线的互连几乎根本无法达到PCI-e所拥有的优秀性能。

PCI Express标准的制定是着眼未来的,它还在继续发展为系统提供更高的吞吐量。第一代PCIe约定的吞吐量是2.5千兆位/秒(Gbps),第二代则达到5.0Gbps,而最近发布的PCIe3.0标准则能支持8.0Gbps的速率。在PCIe标准继续利用最新的技术以提供不断增加的吞吐量的同时,利用分层协议、通过使驱动程序保持与现有PCI应用的软件兼容性将简化从PCI到PCIe的过渡。 虽然最初定位在电脑扩展卡和图形卡应用,但目前,PCIe已在更广泛的领域得到应用,包括:网络、通信、存储、工业和消费类电子产品等。

这里对PCI-e的详细协议不做介绍,只从整体上介绍PCI-e的概述、PCI-e的优势以及FPGA实现PCI-e的优势。

PCIe的优势以其复杂性为代价。PCIe是基于分组的串行连接协议,估计比PCI并行总线复杂10倍以上。这种复杂性部分源于在千兆赫速率所要求的并行到串行的数据转换以及转向基于分组的实现。

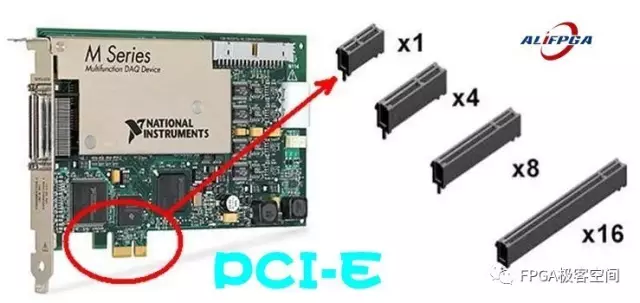

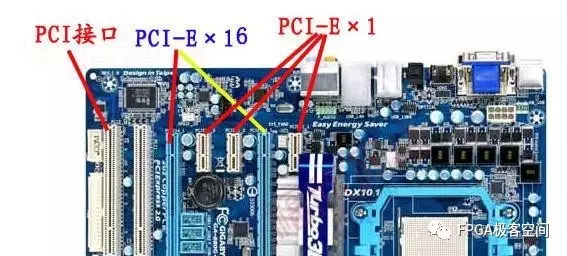

PCI与PCI-e接口

单从接口上就可以看出PCI与PCI-e的区别。一个是并行总线,一个是高速串行总线。

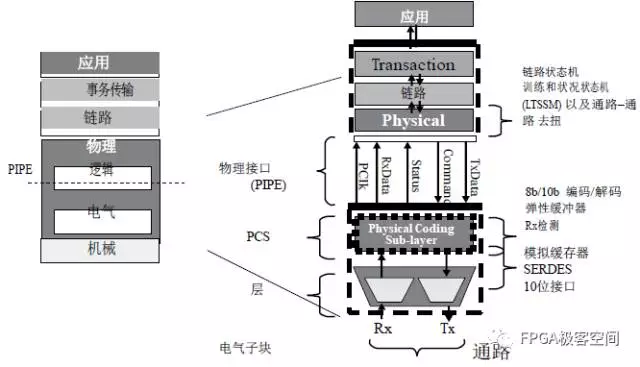

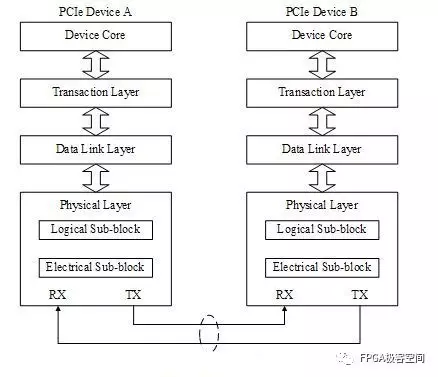

通常将PCI-e总线分为3层:

PCI-e协议层

通常将机械层和物理层合并为物理层,紧接着第二层为数据链路层,第三层为事务传输层,应用层不算在内。

物理层中的机械层:

机械层定义了诸如对连接器、卡外形尺寸、卡检测和热插拔等要求的机械环境。

物理层中的电气和逻辑层:

-

-

物理层下的电气子层实现包括收发器、模拟缓冲器、串行/解串行器(SerDes)在内的模拟器件以及10位接口。

-

物理编码子层(PCS)把每8位数据字节编码/解码为10位代码。这种编码特性不仅能检查有效字符,而且也限制了被发送的“0”和“1”数量上的差异,从而同时在发射器和接收器侧保持了DC均衡,进而大大提高了电磁兼容性(EMC)和电气信号性能。

-

具体协议不在赘述,请查阅相关协议文档。

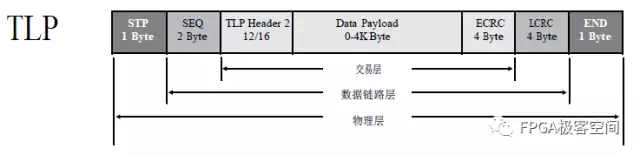

PCIe数据包:

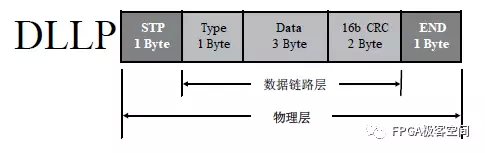

在探讨下一个协议层特点之前,了解数据是如何在PCIe网络上传输的很重要。 PCI Express采用数据包在各系统间以及数字接口的各层和PCIe设备间传输数据。应用层发起事务传输,事务传输层把应用请求转换为一个PCIe事务包。数据链路层为该数据包增加一个序列号和链路CRC(LCRC)。数据链路层还确保该双向事务接收正确。最后,物理层在PCIe链路上传输该事务。

事务传输层

数据链路层

数据链路层:

数据链路层作为处理层和物理层的中间层,为处理层TLP在链路中传递提供可靠机制。数据链路层主要负责TLP的可靠传输。

数据链路层完成的主要任务是:

-

数据交换。接收发送方处理层的TLP包,并送到物理层。另外从物理层接收TLP包并送到接收端的处理层。

-

出错检测和裁决。LCRC和序列号(TLP Sequence Number)的生成;存储发送端的TLP用于再试重发;为TLP和DLLP做数据完成性检测(crc校验);DLLP的ack和nack响应;错误指示;链接确认超时重试机制。

-

初始化和电源管理。跟踪链路状态并传送链路活动、链路复位、链路失去连连等状态给处理层;

-

生成DLLP。用于链路管理功能包括TLP确认、电源管理、流程控制信息(VC通道初始化)交流。在链接两端的数据链路层点对点传输。

-

数据链路层跟踪链路连接的状态,并和处理层和物理层交流链路状态,通过物理层来完成对链路的管理。链路层中包含状态机DLCMSM(Data Link Control and Management State Machine)来完成这些任务。

PCI-e结构中的数据链路层

数据链路层在不可靠(有损耗)的物理链路上提供了可靠的数据传输服务。它是通过验证收到的TLP及使用接收到数据的正确认并在接收失败时重新传送数据来做到这点的。当TLP被发送时,它们被分配给序列号,并采用一个CRC码且把该码发送至物理层以用于串行链路上的传输。接收时,检查CRC和序列号。CRC内的错误或出序的序列号显示发生了传输错误,信号通过给出负确认(NAK)予以响应。接到NAK后,发送器重新传送数据包,该数据包被存储在专为此目的设置的“重传”缓存器内。若CRC序列号检查成功,接收器发出正确认(ACK)。对给定TLP来说,仅当收到ACK时,才对重传缓冲区进行数据刷新。使用此协议,数据链路层可以保证TLP的正确发送。

具体协议不在赘述,请查阅相关协议文档。

事务传输层:

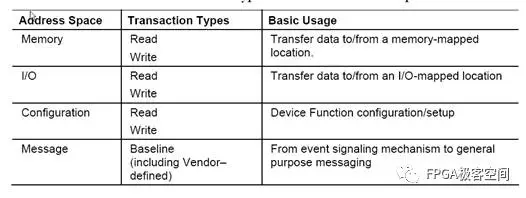

事务传输层(transaction Layer specification)是请求和响应信息形成的基础。包括四种地址空间,三种处理类型,下图可以看出在transaction Layer 中形成的包的基本概括。

地址空间

事务传输层创制出站及接收入站事务传输层数据包(TLP)。TLP包括一个报头、一个可选数据配载以及一个可选的端到端CRC(ECRC)。TLP既可以是请求也可以是对请求(完成)的响应,它永远是4个字节(1个DWORD)的倍数。报头指定事务类型、优先级、地址,路由规则及其他数据包特征。发送事务传输层构建数据包报头、伺机添加ECRC并门控数据包的传输(直到有足够的远程流量控制额度可用)。接收事务传输层检查TLP格式和报头。

具体协议不在赘述,请查阅相关协议文档。

PCI-e基本功能和属性:

-

-

吞吐量:流量控制额度

-

QoS:传输类别和虚拟通道

-

RAS:数据完整性

-

RAS: 排序/PCI规则

-

主动电源管理

-

先进的出错管理

-

中断

-

设计复杂性:

-

-

数据速率提高带来的困难。高速链路设计要求设计者具有很强的高速模拟设计功能。当数据速率达到1Gbps以上时,I/O缓冲器的设计需要进行重大改变,同时高速率时处理数据所需的数字逻辑也不一样,编码方案及补偿逻辑使其物理层与低速物理层极大不同。

-

高数据率产生时钟问题。高速数据率必然产生时序裕量紧张,这就需要高度的时钟稳定性来保障。时钟数据恢复(CDR)电路显得极为重要。

-

高数据率产生制板问题。Gbps以上的数据率使得PCB制板难度增大,电路布局布线技术难度增大,必须采用机械制板,显然成本会大大增加。

-

FPGA在PCI-E应用中的优势:

FPGA中嵌入了吉比特收发器等硬件IP。采用吉比特收发模块,可以在一片FPGA中实现高速串行协议,包括PCI-e、千兆以太网等。

使用FPGA设计PCI-e总线,省去PCI-e专用接口芯片,降低硬件成本,提高硬件集成度。利用FPGA的可编程特性,大大提高设计的灵活性、适应性和可扩展性。

Altera的PCIe硬核IP包含处理层,链路层和物理层所要求的全部功能,以及大多数的可选功能。只需在IPCompiler中经过简单的参数设置即可生成全功能的IP模块,如果是作为端点设备,可以使用Avalon-ST接口或Avalon—MM接口适配器,将应用层映射为处理层的TLP。Avalon—ST适配层将应用层的Avalon—ST接口映射到PCIe处理层的TLPs。

版权所有权归卿萃科技,转载请注明出处。

作者:卿萃科技ALIFPGA

原文地址:卿萃科技FPGA极客空间 微信公众号

扫描二维码关注卿萃科技FPGA极客空间