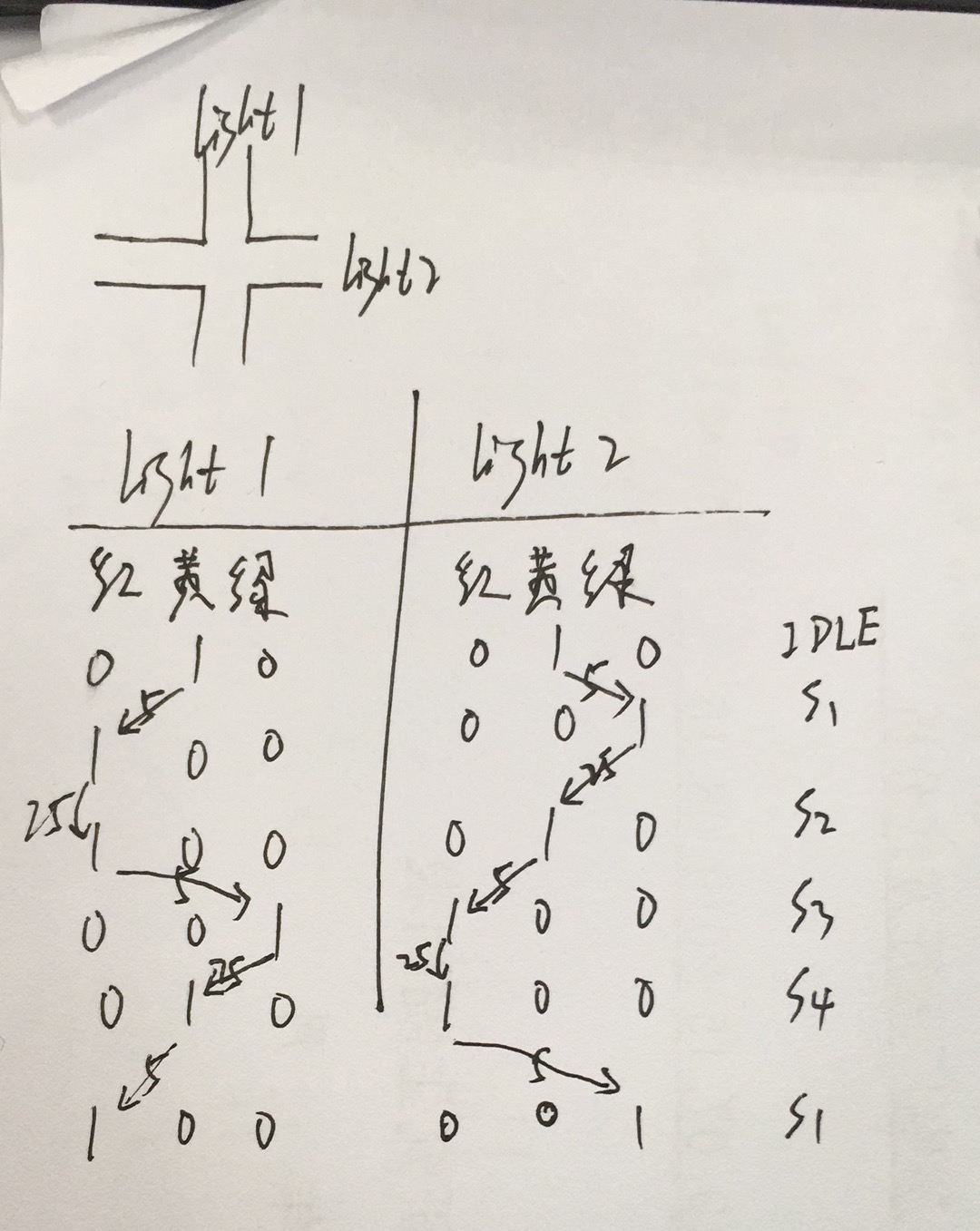

绿灯25秒,黄灯5秒,红灯30s

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: 10:14 2020/6/5 // Design Name: // Module Name: // Function : // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module traffic( clk, rst_n, light1, light2 ); input clk; input rst_n; output reg [2:0]light1; output reg [2:0]light2; /* parameter cnt5s=249_999_999,cnt25s=1_249_999_999; */ parameter cnt5s=249,cnt25s=1_249;//仿真用 localparam IDLE=5'b00001, S1=5'b00010, S2=5'b00100, S3=5'b01000, S4=5'b10000; reg [4:0]current_state,next_state; reg [31:0]cnt; reg en_cnt; //使能和计数 always@(posedge clk or negedge rst_n) if(!rst_n) cnt<=32'd0; else if(en_cnt==1'b1) cnt<=cnt+32'd1; else cnt<=32'd0; //状态切换 always@(posedge clk or negedge rst_n) if(!rst_n) current_state<=IDLE; else current_state<=next_state; //次态生成 always@(*) if(!rst_n)begin en_cnt=0; next_state=IDLE; end else begin case(current_state) IDLE:begin en_cnt=1; if(cnt==cnt5s)begin next_state=S1; en_cnt=0; end else next_state=IDLE; end S1:begin en_cnt=1; if(cnt==cnt25s)begin next_state=S2; en_cnt=0; end else next_state=S1; end S2:begin en_cnt=1; if(cnt==cnt5s)begin next_state=S3; en_cnt=0; end else next_state=S2; end S3:begin en_cnt=1; if(cnt==cnt25s)begin next_state=S4; en_cnt=0; end else next_state=S3; end S4:begin en_cnt=1; if(cnt==cnt5s)begin next_state=S1; en_cnt=0; end else next_state=S4; end default:begin en_cnt=0; next_state=IDLE; end endcase end // always@(posedge clk or negedge rst_n) if(!rst_n)begin light1<=3'b010; light2<=3'b010; end else begin case(current_state) IDLE:begin light1<=3'b010; light2<=3'b010; end S1:begin light1<=3'b100; light2<=3'b001; end S2:begin light1<=3'b100; light2<=3'b010; end S3:begin light1<=3'b001; light2<=3'b100; end S4:begin light1<=3'b010; light2<=3'b100; end default:begin light1<=3'b010; light2<=3'b010; end endcase end endmodule

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: // Design Name: // Module Name: // Function : // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module traffic_tb(); reg clk; reg rst_n; wire [2:0]light1; wire [2:0]light2; traffic traffic( .clk(clk), .rst_n(rst_n), .light1(light1), .light2(light2) ); initial clk=0; always #10 clk=~clk; initial begin rst_n=0; #201; rst_n=1; end endmodule