问题: 输入一个8bit数,输出其中1的个数。如果只能使用1bit全加器,最少需要几个?

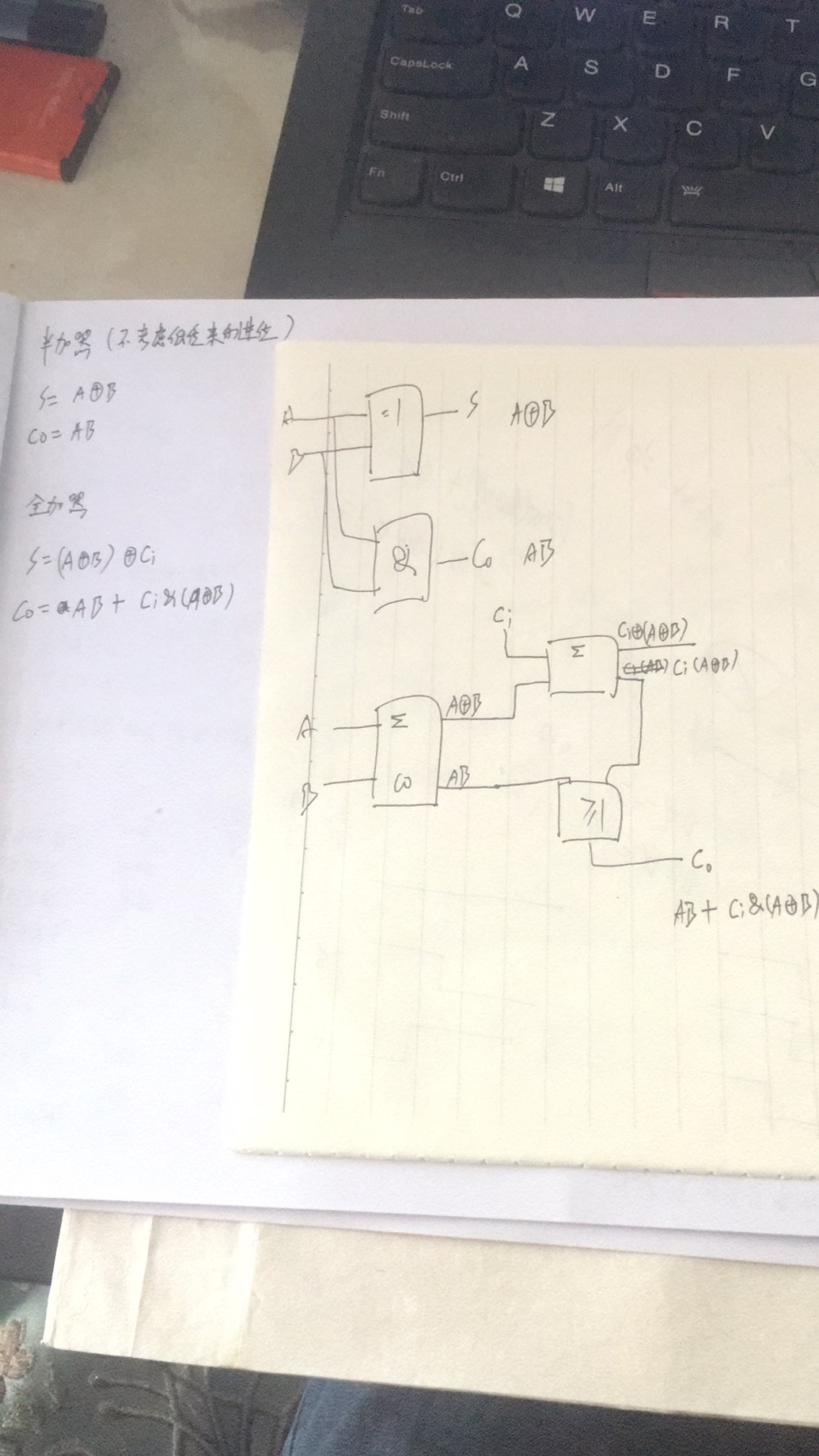

先来了解一下全加器和半加器:

http://m.elecfans.com/article/716153.html

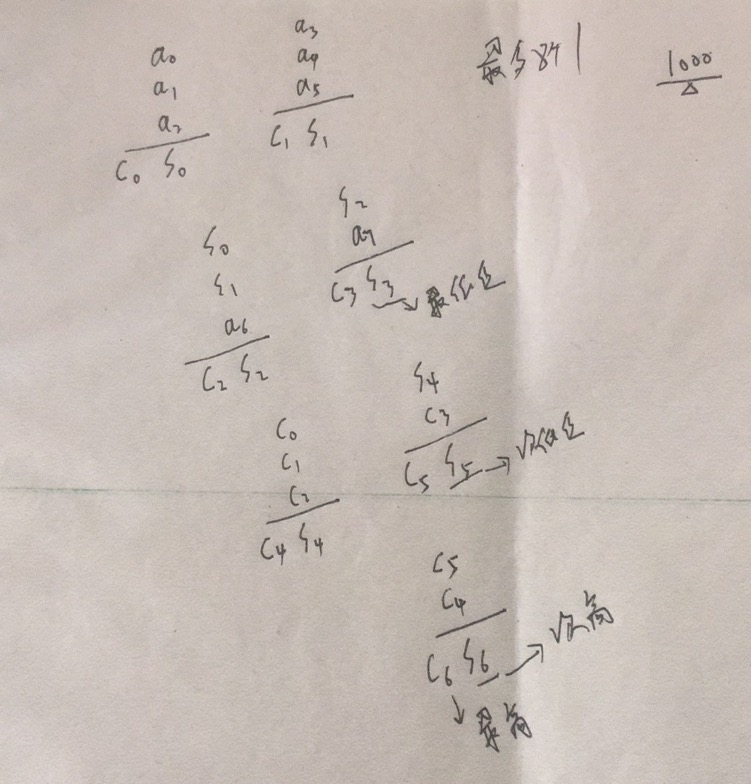

所以解题思路如下:

https://forum.allaboutcircuits.com/threads/count-number-of-logic-1s-in-7-bit-number.49821/

module f_add(a, b, ci, s, co ); input a; input b; input ci; output s; output co; assign {co,s}=a+b+ci; // assign s=(a^b)^ci; // assign co=(a&&b)||(ci&&(a^b)); endmodule

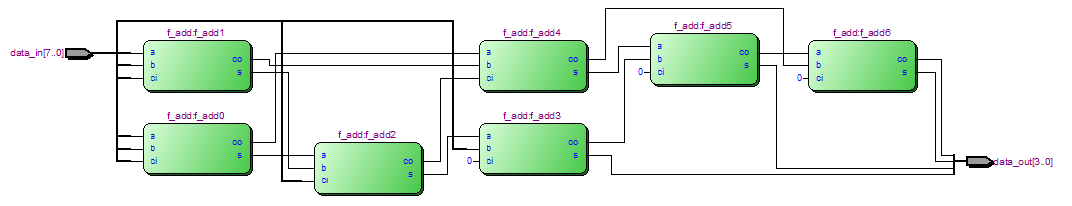

module count_1_add( data_in, data_out ); input [7:0]data_in; output [3:0]data_out;//最多只需要四位就可表示8,即输入的8位二进制全是1的情况 wire s0,s1,s2,s3,s4,s5,s6; wire c0,c1,c2,c3,c4,c5,c6; f_add f_add0( .a(data_in[0]), .b(data_in[1]), .ci(data_in[2]), .s(s0), .co(c0) ); f_add f_add1( .a(data_in[3]), .b(data_in[4]), .ci(data_in[5]), .s(s1), .co(c1) ); f_add f_add2( .a(s0), .b(s1), .ci(data_in[6]), .s(s2), .co(c2) ); f_add f_add3( .a(s2), .b(data_in[7]), .ci(1'b0), .s(s3), .co(c3) ); f_add f_add4( .a(c0), .b(c1), .ci(c2), .s(s4), .co(c4) ); f_add f_add5( .a(s4), .b(c3), .ci(1'b0), .s(s5), .co(c5) ); f_add f_add6( .a(c5), .b(c4), .ci(1'b0), .s(s6), .co(c6) ); assign data_out={c6,s6,s5,s3}; endmodule

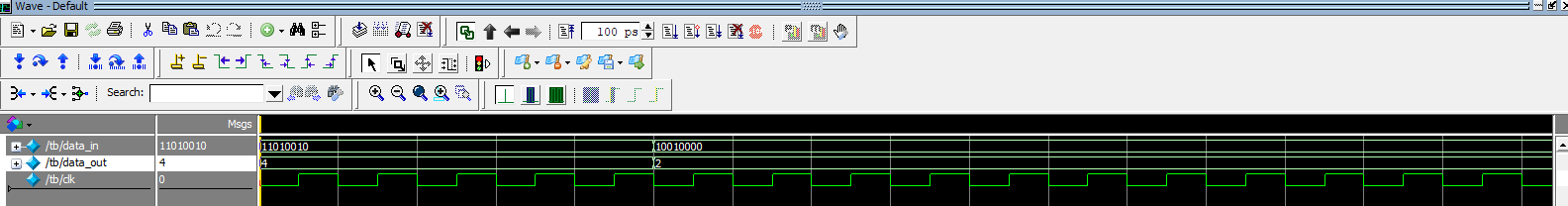

`timescale 1ns/1ns module tb; reg [7:0]data_in; wire [3:0]data_out; reg clk; count_1_add count_1_add( .data_in(data_in), .data_out(data_out) ); initial clk=0; always #1 clk=~clk; initial begin data_in=8'b1101_0010; #10; data_in=8'b1001_0000; end endmodule

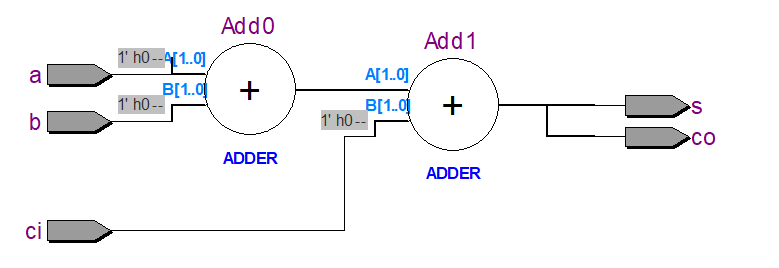

可以看到用了七个全加器,点开其中一个,可以看到一个全加器由两个半加器和一个或门组成。