1. 概述--何为有限状态机FSM?

有限状态机-Finite State Machine,简写为FSM,是表示有限个状态及在这些状态之间的转移和动作等行为的数学模型,在计算机领域有着广泛的应用。通常FSM包含几个要素:状态的管理、状态的监控、状态的触发、状态触发后引发的动作。

以下为wiki上有关FSM的介绍,链接地址为Finite State Machine-WiKi 。

A finite-state machine (FSM) or finite-state automaton (plural: automata), or simply a state machine, is a mathematical model of computation used to design both computer programs and sequential logic circuits. It is conceived as an abstract machine that can be in one of a finite number of states. The machine is in only one state at a time; the state it is in at any given time is called the current state. It can change from one state to another when initiated by a triggering event or condition; this is called a transition. A particular FSM is defined by a list of its states, and the triggering condition for each transition.

2. FSM有哪些形式?

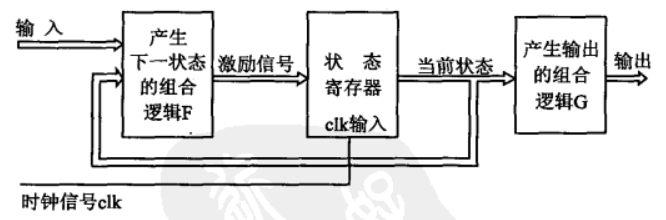

对于FPGA硬件电路,不管状态机是何种,我们假定F是当前状态和输入信号的函数。状态机的输出是由输出组合逻辑G提供的,G也是当前状态和输入信号的函数。那么对于状态机的逻辑,可以表达如下:

下一个状态 = F(当前状态,输入信号);

输出信号 = G(当前状态,输入信号);

在状态机中,我们依据状态机输出与输入的关系将状态机分为了两个模型,分别是Mealy状态机和Moore状态机。下面对这两个部分进行详解。

3. Mealy状态机

Mealy状态机为状态机时序逻辑输出不但取决于状态,还取决于输入的一类状态机。此时,其状态机输出表达式为"输出信号 = G(当前状态,输入信号);"这种。

时钟同步的Mealy状态机结构如图1所示,从图中可以看出其输出逻辑G的输出由输入和当前状态一同决定。

图1 时钟同步的Mealy状态机结构

4. Moore状态机

与Mealy状态机相对应,Moore状态机的时序逻辑输出只取决于当前状态的这一类状态机。此时,其输出表达式为"输出信号 = G(当前状态,输入信号);"这种。

时钟同步的Moore状态机结构如图2所示,从图中可以看出其输出逻辑G的输出仅由当前状态决定。

图2 时钟同步的Moore状态机结构

5. Mealy vs Moore 状态机

a) Mealy机比Moore机“响应”速度快。

Mealy机的输出与当前状态和输入有关,而Moore机输出仅与当前状态有关。Mealy机的输入立即反应在当前周期;Moore机的输入影响下一状态,通过下一状态影响输出。为此Mealy机比Moore机输出序列超前一个周期,即“响应速度”较快。Mealy机的输出在当前周期,具有较长的路径(组合逻辑);Moore机的输出具有一个周期的延时,容易利用时钟同步,Moore机具有较好的时序。

b) Mealy机状态少,Moore机结构简单。

由于Moore机的输出只有当前的状态有关,一个状态对应一个输出,Moore机具有更多的状态。Mealy和Moore机之间可以相互转化,对于每个Mealy机,都有一个等价的Moore机,Moore机状态的上限为所对应的Mealy机状态的数量和输出数量的乘积。

c) 状态机的状态通过触发器的数量来反应,Mealy机具有较少的状态,为此具有较少的触发器。

此部分参考:两种类型状态机。