LDO(低压差线性稳压器),FPGA需要3.3V、2.5V和1.2V,可选用凌力尔特LINEAR:LT1083/84/85,低压差正压可调稳压器。

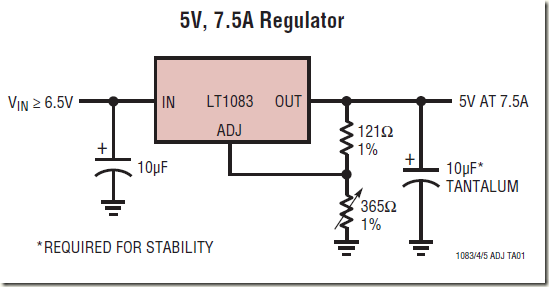

应用电路如图所示:

输入端加10UF电解电容,输出端加10UF胆电容。

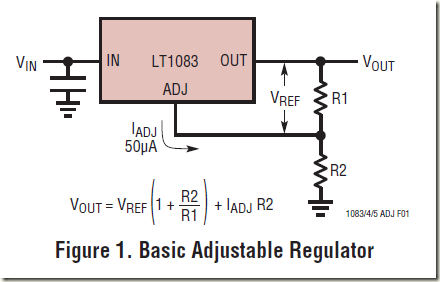

基本可调稳压器电路图如上图所示,通过改变R1、R2阻值输出需要的电压值,由于Iadj很小,计算时可以忽略不计。故等式变为:

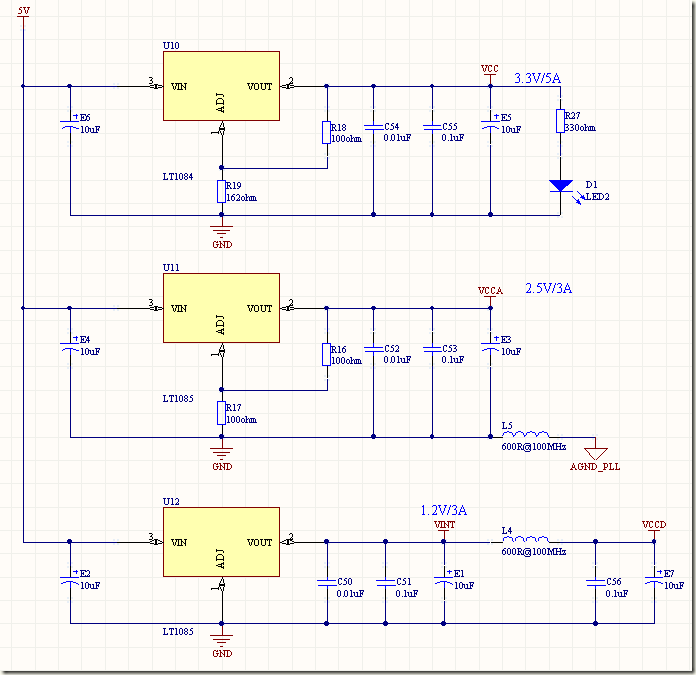

电路板电源设计如下图所示:

3.3V:R1=100Ω,R2=162Ω

2.5V:R1=R2=100Ω

1.2V:ADJ直接接地,1.25V≈1.2V

疑问:1.输出端接了0.1uf和0.01uf去耦电容? 2.磁珠使用和VCCD、VCCA,模拟数字地和电源? 3.R1、R2是否必须是1%精度?