(1)单口RAM

1.无读使能rden信号的ModelSim功能仿真:

在不使用读使能rden信号的情况下,单口RAM仿真结果表明:

1.写使能wren为高时,写数据操作有效;

2.写使能wren为低时,读数据操作有效;

3.写有效(高)时,输出端q输出为刚写入的数据;

4.一般选择输出寄存一拍。

2.有读使能rden信号的ModelSim功能仿真:

在使用读使能rden信号的情况下,单口RAM仿真结果表明:

1.读使能rdren为高时,读数据操作有效;

2.写有效(高)时,读使能信号为低,则输出为上次读使能信号有效时的数据;

3.写有效(高)时,读也有效(高)时,输出端q输出为刚写入的数据。

另外,由于地址和数据在时钟上升沿改变,因而此刻有效值仍为改变前的值。在下一上升沿,改变后的值有效。再下一个上升沿,输出端q数据读出。所以,由时序结果好像是经过“两拍”后输出数据。这源于数据是边沿有效而不是中央有效(时序约束中也有涉及),同理SignalTap II中抓取的数据也会有这个情况。对于边沿有效,在时钟上升沿,信号的有效值为改变前的结果。

(2)双口RAM

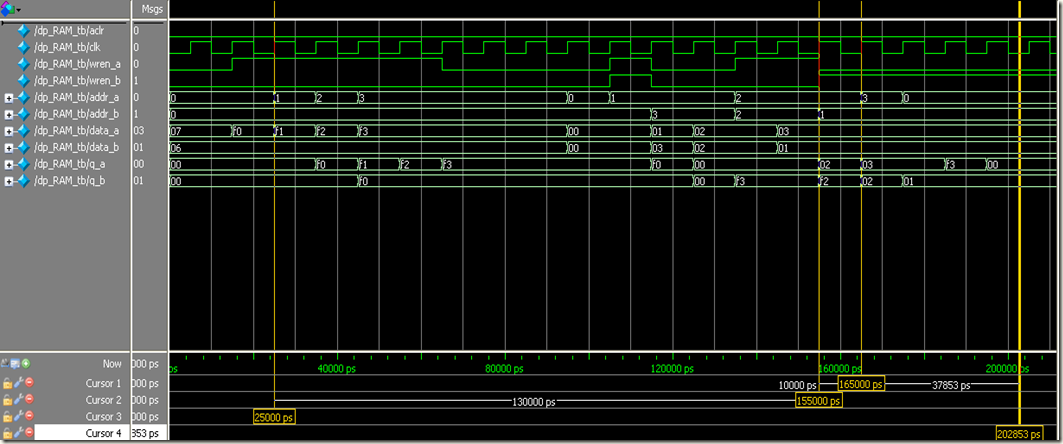

双口RAM的仿真选用了真双口RAM,有两组PORT(A、B),初始内部数据为0。

仿真结果如下:

testbench中利用非阻塞赋值,在仿真时刻完成右值的更新,在仿真结束时刻完成左值的赋值。所以和单口RAM仿真中提到的一样,信号在第一个时钟沿改变数值,在第二个时钟沿有效,在第三个时钟沿输出数据(由于输出寄存一拍),这和实际情况也一致。

说明下图中几个标尺的解释:

1.在25000ps时刻,地址0写入数据f0h,在下一个时钟沿q_a端输出f0h,后面同理。

2.在155000ps时刻,A端口对地址2进行写操作,而B端口对地址2进行读操作,出现了Mixed Port Read-During_Write情况,在配置IP核时,我们选择了读端口输出Old memory contents appear,故此时B端口读出地址2原先的值f2h。同理,在165000ps时刻,B端口读出地址2原先的值02h。

另外对于下面的设置,有点不理解,不知和上面有何区别。