前言

找工作的标准----自己熟悉擅长的和前景很好的(IC设计,图像算法,FPGA开发,人工智能)

首先展示下师兄offer:希望能够作为参考薪资和福利待遇

第一部分:工作的单位

岗位:数字IC设计,FPGA开发,数字图像处理

公司:国企和私企

第二部分:重点推荐公司

大公司:华为,阿里,腾讯,字节跳动,网易,美团。

国企:中信集团(金融方面),中国建筑,中国国际金融股份有限公司,招商银行(无硬件或图像算法岗)国家开发银行,中国航空工业集团,航天集团,科工集团,中共四川省组织部,中国建设银行,中国兵器工业集团,中国电子科技集团(专业对口)

其他的中型公司:翱捷科技(上海)有限公司,深圳市汇顶科技(十分看本科学校,得211和985才行),紫光展锐(二面等被捞),芯原(投一下),珠海全志科技,芯动科技(未开始)

8.7号,最近面了一个中型公司,中科忆海微(中科院电子所建立的一个公司)

由于论文投了将近两个月,一直没消息,自己学习FPGA的高速接口,DDR3,千兆以太网,PCIE等高速接口,并且做了DDR3+千兆以太网+HDMI联合实现视频传输的项目,还有基于RIFFA框架的PCIE视频传输。但感觉收获颇少,还有动力不足。所以就开始了换一种方式去学习,想去实习。记下这篇找实习的经验,一方面是为了记录成功找到实习的宝贵经历。另一方面是,为以后自己找工作带来巨大的帮助。

实习offer

哈哈,很幸运在知名国产FPGA品牌公司实习,offer展示一波;

秋招offer

上面是自己收到的部分offer,经过十月初投递,一个月的面试,陆续收到成都华微,奥比中光,紫光展锐,中科芯和易冲半导体,紫光同创等offer。后面综合对比了岗位和薪资及工作地,选择了成都一家中型公司,暂时躺平了。今年很庆幸IC工资奇高,接近算法工资,很多都拿到成都30万年薪,希望IC能继续火下去,让这风口多几年。

第三部分:成都地区的IC设计公司

海思、中兴、展锐、芯原、华微科技、华大恒芯、紫光同创、新华三、瓴盛、联发科、烽火、安路科技、卓胜微、国科微、翱捷科技、海光、威发半导体、汇顶科技、雄立科技、启英伦泰、全志、锐成芯微

很多公司---待我投一波2021.10.15日

一 找实习途径

1.boss招聘手机app

刚开始啥都不懂,直接问师兄,他回我消息说,一个boss直聘app就够了。然后,我下载后,和里面的BOSS先聊工作有兴趣再投简历,在里面有几个boss对我的简历感兴趣,如电信,从事单片机的公司,还有其他的IC设计公司如深圳国微电子有限公司,广州智慧城市发展研究院。我面试了其中一家,后面和面试官聊天过程中,知道他们公司的核心是做单片机开发,主要是器件的原理图设计和C语言开发等,和我学的不一样,我就婉拒。中国电信没有FPGA和IC设计相应岗位,我没有区参见面试。

2.实习就业QQ群

我加了一个FPGA的数字IC校招群,里面有很多相关的企业进行校园招聘。我就登录每一家公司的官网和关注微信公众号,点击校园招聘,查看是否招实习生,和地点合适就会投简历。当然咯,很多公司都是没在广州,虽然他们要实习生,但我希望能够在广州实习。其中,还是重点关注了,华为,海康威视,大疆等三家巨头。希望自己以后有机会和实习去投这三家和有面试机会,当然字节跳动的薪资高的离谱,但都是算法和软件岗位,与我的情况不符合。

3.老师推荐

我直接告诉老师,想去实习,问他有啥推荐到,推荐了两家深圳的公司,收到其中一家的面试,我直接定了到深圳的动车去了。面试我的是两位主管,那次面试印象很深刻,具体细节后面再讲。

4.应届生求职网

这是一个很全很实用的网站,有着大量的实习和招聘信息。网址是:http://www.yingjiesheng.com/

我就利用这个网站,找到自己很感兴趣的公司。小马智行和高云半导体。

二 实习准备

建议看摸鱼范式(微信公众号)-----秋招指南

https://mp.weixin.qq.com/s/xWlW1gJpJUEFsHIDy44h8Q

1.简历

首先,一份简历必不可少的。一般包含个人信息,求职意向,教育背景,专业技能,实习,项目经验(核心),获奖证书,个人总结及规划。当然咯,有深度又新颖的项目是最让面试官感兴趣和喜欢的。

- 项目的简要概述,包括项目是做什么的,采用什么方法,用到了哪些协议

- 讲清楚自己所负责的内容,不是自己做的,一定不要写

例如我写的图像边沿检测和录音机回放与录音,面试官一致反映太简单,太多人做过。

2.自我介绍

就是从大学到现在,你做了啥。我就是从所学课程,所做的FPGA项目,还有科研方向,参加的活动和经历,对未来规划等。

3.对项目的巩固

自己简历上的项目,重点是串口IP, RGB家电显示模组,DDR3+千兆以太网+HDMI视频显示;先是总体框架的解读,再是对每个模块的了解,最后是模块间的通信。所以,建议搭建把自己在面试中所遇到的所有问题,无论自己回没回答上来,都记录下来。不仅仅是问题,还要包括自己的回答,面试官的解释,不会尝试问一下面试官。大公司看重:成绩(专业排名,学校),成果(期刊论文,专利),比赛(ACM,蓝桥杯等),四六级成绩。小公司看重,技术细节。

4.找面经的方法

A:直接百度(知乎,牛客,看准网,博客等)

B: 直接在秋招群里问,如摸鱼范式,FPGA/IC秋招

C:问师兄或面过的XD

D:微信公众号:数字ICer,达尔闻说,摸鱼范式,FPGA探索者,数字IC打工人

扩展:找笔试题

1. 一曲挽歌

https://www.cnblogs.com/yiquwange/category/1967896.html

2.Thomas

上面一个大佬的知乎网民,有很详细的面经总结,链接如下:

https://zhuanlan.zhihu.com/p/149435387

三 找实习的面试细节

这是我最近一个月的时间,做的一个项目,利用DDR3和千兆以太网及HDMI进行视频传输。基本上图像边沿检测项目很尴尬,会直接略过。对于高速接口的视频传输,面试官一般比较感兴趣,觉得有分量。

面试的宝藏:

面试必备: 一是项目的总体介绍(数据的流向,实现的功能,具体的需求及条件);二是项目的主要模块(如你负责的模块那些,你是怎么设计,用到那些知识和协议及总线,代码的输入输出信号,输入是怎么驱动输出的,有状态机嘛,每个状态各实现那些功能)。三是IC基础和Verilog基础(三段式状态机,跨时钟域处理,异步FIFO,时序分析的建立与保持时间)

深圳市创凯智能股份有限公司---------面试公司1

关键是有深度的新颖的项目细节。(如千早以太网联合DDR3加HDMI接口的视频传输,边沿检测,他说太简单,很多人做过。 )首先是让自己总体介绍一下项目,在针对项目的主要模块分别询问细节。如项目的主要模块,千兆以太网,DDR3,HDMI接口。

千兆以太网:协议是UDP 和RGMII协议(介绍怎么设计),自己设计那些逻辑。还有16-128,128—16的模块转换的数据,输入和输出功能分别是,数据格式。然后问了FIFO的原理,FIFO仅用在跨时钟浴的处理还能用在那种场合,FIFO怎么设计,fifo的功能。

DDR3模块: DDR3的总线是AXI4还是SPI,( 对这些总线的认识)问我使用的开发版型号,有哪些资源,都利用这些资源做过逻辑设计嘛,DDR3有几个,内存多大。还有就是做过SOC控制和GPU嘛,以及其他图像处理的项目嘛。

HDMI:HDMI怎么驱动,是用IP核例化还是自己设计的逻辑,HDMI的数据输出位宽。做过图像的编码解码项目嘛。对于传输的视频,分辨率为多大,所需要的带宽是多少。还有我的千兆以太网的速率和带宽是多少。

PCIE我又了解多少。

最后:从大学到现在,我有没有一直在专研的东西。未来的规划。(重要)

总给下,刚开始通过boss招聘,先去面试了广州一家做单片机的小公司,不感兴趣面完就走了。后面是找尤老师推荐,去了上面推荐的创凯智能面试,由于他们想要的是直接工作,我是来实习,就没谈妥;之后收到了自己投递的广东高云半导体科技股份有限公司的面试,我很开心,由于在广州读研,那多方便,直接住学校,有事很方便回学校处理。去了高云,两个面试官,问了三十多分钟,面完就回学校了,之后下午收到济南HR的电话,说面试官觉得我的表现不错,邀请我去实习,谈了薪资和入职所带证件和材料,之后就是发录用通知的offer(盖着公司公章),要求一天内回复,我爽快签了后,通过全能扫描王发送邮件给HR;隔了一天,又通知我带上学历证书和学位证书,还有身份证,学生证,中行卡去办理入职仪式。

期待着实习生活的开启。

四 校招---找工作

中科亿海微(后面8月16日得到offer,即毕业后可以去他们的成都分公司)---------面试公司2

面试过程:刚开始是介绍他们的公司,然后是正式开始面试,即我先自己介绍完简历上的项目,然后面试官针对具体细节提问,前后总计40多分钟!

SPI的通信原理比较简单,它以主从方式工作,通常有一个主设备和一个或多个从设备。一般其有 4 根线,片选线(CS)、同步时钟线(SCLK)、输入数据线(MOSI)和输出数据线(MISO)。对于RGB家电模组显示项目,SPI的操作模式,相位,极性固定配置为CPOL=0,CPHA=0,SCK上升沿采样数据;

对应SPI总线:本次项目要求的传输方式是半双工,所以MISO替代成DCX信号线,用于发送信号区分命令信息与数据信息。DCX线为低电平,发送为命令信息,高电平则数据。

一是RGB家电显示模组SPI的速率?

SPI传输速率支持1-100MHz。采集SPI输入时钟10M,峰值传输下,完成一次传输需要多少有效比特,数据传输速率--每秒传输二进制信息的位数,单位为位/秒,记作bps或b/s。

二是SPI是单端口还是双向单口?

双向端口,同时也是一个同步时序电路

三是后面课程所用的开发型号及平台----

- Xilinx的A7的XC7A75TFGG-484-2.

- XILINX的spartan-6,开发工具ISE14.7

- DDR3 控制器带宽的计算???

400 是控制器PHY 的时钟,2 是DDR 双沿采样,16 是16bit,bus 的位宽。

400*2*16=12.8Gbps 带宽,若是考虑实际情况,12.8G*0.8=

视频传输带宽:1024*768*60*16=视频分辨率*帧率*数据比特位数(bps)

四 关于DDR3的相关问题

- DDR3调用了几个app端口,DDR3控制器的个数

调用了一个APP的CMD端口,一个APP的写端口,一个APP的读端口。一个控制器。

2.PHY时钟与用户端的时钟与比例

如4;1,则PHY时钟400M,则用户端时钟就为100M

对于千兆网==HDMI显示有质量检测,如误码率等

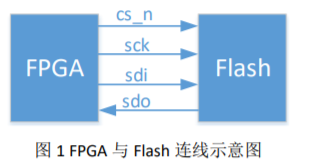

五 flash的问题

对于flash模块,一是flash的型号M25P16。

二是FLASH的寻址方式,地址位宽是多少

回答是24位。

千兆网—CRC-32校验,若HDMI要检验误码率,写一个HDMI的接收端检验误码

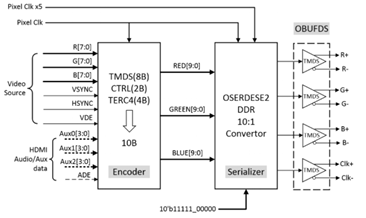

六 HDMI相关问题

HDMI1.4协议

HDMI—高清多媒体接口。

TMDS数据,TMDS时钟,HDMI输出使能。TMDS 差分传输技术使用两个引脚(如图中的“数据 2+”和“数据 2-”)来传输一路信号,利用这两个引脚间的电压差的正负极性和大小来决定传输数据的数值(0 或 1)。

HDMI 程序设计

编码和并串转换

在编码阶段,编码器将视频源中的像素数据、HDMI 的音频/附加数据、行同步和场同步信号分别编码成 10 位的字符流,

并串转换

将编码输出的10B转换成串行数据流,并将其从三个差分输出通道发送出去。

如上图的框图,还应添加一个VGA时序作为框图的输入,为HDMI的设计框图,包含编码和并转串模块。

这样可以,把VGA时序,编码模块,并转串模块三个封装成一个HDMI显示模块,直接调用即可。

视频输入分辨率及大小=1024*768@60HZ。

HDMI的视频像素时钟CLK1X = 65

CLK5X为上面像素时钟的5倍325Mhz

紫光展锐---------面试公司3

第一次用内推码投递,之后笔试。笔试一周后823一面,8月30二面,吃完饭再来详细改:

第一次面试25分钟:

首先是自我介绍;之后是然我自己讲解所作的项目,其次重点问了DDR3 和千兆以太网,之后是让我提问;我主要是问了紫光的招聘流程--他的回答,按照HR走;第二个是让面试官介绍一下紫光;

面试官问了我很多:

问题1:师范大学不是直接去学校当老师嘛?还需要自己找嘛

我的回答是,师范大学除了免费师范生,其他专业,包括师范专业都是需要自己找工作;师范大学除了师范专业,还包括工科,理科,文科等,而且华师的物理学,光学等学科是国家重点,师资和教学设备很强大;

问题2:本科是直接考上研究生还是保研?考上成绩多少

答:直接考研的,排名第四

问题3:本科成绩和研究生成绩咋样?

答:本科前50%,研究生前30%,本科和研究生都获得过二等奖学金和三等奖学金

问题四;科研情况?

投递一篇红外图像细节增强论文,处于返修中

紫光二面

相对于上次面试,更加具体和深入,总共时间25分钟,先自我介绍,再开始项目细节还有游戏环节

问题1:我做的USB2.0协议的开发平台是啥?

高云的软件和高云的开发板,以及通过USB2.0协议手册自己写四种传输的仿真文件,比如从机设备地址配置,steup包的建立,标志请求,配置描述符,通过modelsim仿真波形和金斯特逻辑分析仪LA5016等抓取数据线的数据,看是否和上位机一样,还有就是开发板调试,通过串口助手和开发板是否能够成回环测试接收发送数据;

问题2: 我做的项目是基于那一层级?物理层,RTL层(应用层),算法,系统级(如流片)?

答:还有问道项目都是高云嘛,我做的除了高云实习项目,还有自学的视频传输(DDR3+千兆以太网+HDMI视频传输),自学主要是基于Xilinx和alterl的开发平台和工具,没有用过芯片的开发平台和工具

基本上都是关于调用Xilinx的IP核,并未有自己从头搭建电路,进行电路设计,也没有用到算法层面,目前只做了localdimming算法的预估和调研,即用matlab仿真出效果

然后详细讲了串口IP设计,主要是根据原先的串口IP,设计出时钟任意,波特率能够达到4M的IP,方法是,通过更改波特率采样,如16倍过采样改为8倍,把发送和接收的逻辑都改成符合8倍采样;调试方法,modelsim仿真,在线逻辑分析仪,开发板验证,金斯特虚拟仪器LA5016等抓取串口数据接收线和发送线的数据,如发送的是0X6C,看是否正确;还有就是localdimming项目,这个涉及图像算法处理,还有达到,自己研究方向的红外图像细节增强就是算法实现,基于matlab设计和验证的。

问题3 所做的串口IP是怎么控制进度的?

一是通过对小数的处理,如小数可以扩大10之后计算;二是通过对生成采样时钟控制,通过锁相环生成8倍过采样时钟,而不是RTL代码

问题四 有学过以下的IC设计知识嘛?

Linux, Gvim, Git, Repo, VCS, Cadence,Makefile, Verdi,...

TCL/shell/Python

答:主要是关于FPGA开发,所学的为Xilinx的开发工具和平台,没有涉及到以上的知识

问题5 就是做两个小游戏

游戏1 两个人说一个数字,范围为1-10的整数,所加之后小于10,那么各自得到说的金额,否则啥都没

我就说了6,问我咋想,回答是我想冒险进取点,得到更多,而且对方说小于5的概率接近50%,值得一试,面试官的回答是5,故大家都未能获得

游戏2 扩展到10个人,游戏规则是十个人各说一个数(在1-10间),所加之和平均值乘上0.6,让我猜测是多少?

回答是4,我的理由是,因为每个人选10,结果最大为6,同时每个人不可能这么疯狂都选最大的,可能会有人选小于10,综合一下我就选4.他的解释,这道题考察你是理工思维还是感性思维,因为这道题牵涉到数学计算,你得想每个人都输入10最大值为6,再结合每个人不可能选10,若是每个人都选5那么结果为3,可能会有人选大于5,那结果就在3-到6间。主要是数学思维,取极限的问题。

之后就是我有啥想问的?

问题1 紫光的主要产品是啥?

答:主要是做通讯芯片,即3G-5G的手机芯片

问题2 紫光对新人的培训?

分成两个部分,一是通用的培训如公司规则和作息,着装和保密等;二是部门培训,着重人才培养;部门培训,就是公司有文档,包含需求来源,函数设计,仿真,流片,问题等8个方面,再结合公司客户的项目,自己实践做,通过三年后,这样的培训就能够流片,也能选出公司的优秀人才;

问题3 在紫光的发展路线?

分成两条,技术路线和管理路线,如初级工程师,高级工程师,资深工程师等,管理就是部门经理,部门总监,公司副总裁等

总结下,紫光是我所向往的,若是有机会能进去,后面公司的完整培训结合自己努力进取,应该能有很好的发展。当然还收到了海康的面试,下次记得投一下长虹.

海康 威视------面试公司4

面试题3道:

问题1 请举例说明你是如何完成非常紧急且复杂的任务?你具体做了什么?如何推动进程达成结果?

答:5分钟视频录制

问题2 请回忆你用新的方法或者独特的方案来解决常规问题的一次经历。你当时具体是怎么做?你的方案独特在哪?结果怎么样?

答:5分钟视频录制

问题3 详细说你是怎么决定你的职业规划和选择的。你进行了那些思考?参考了那些信息?具体做了什么事情?

答:5分钟视频录制

珠海全志科技---------面试公司5

先提前准备下,搜了面经

技术面

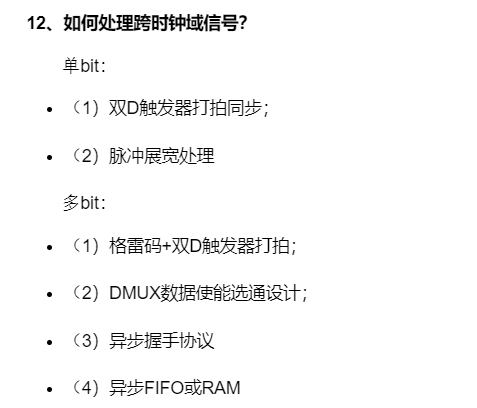

1、A时钟域为100MHZ,B时钟域为10MHZ,异步FIFO中,因为是慢时钟域采集快时钟域的指针,B采集到的格雷码变化也是多位存在问题么

(1)格雷码

比较空满时,需要读写地址进行判断,二者属于跨时钟域,需要进行打拍的同步处理,避免亚稳态,采用格雷码,因为格雷码相邻只有一位变化,这样同步多位时更不容易产生问题。

格雷码公式:gray = (binary>>1) ^ binary;

会导致写满和读空的标志相同,无法确定【读写地址相同】时到底是写满还是读空,因此可以设置一个写指针 wr_addr_ptr 和 读指针 rd_addr_ptr,其位宽比读写地址多1位,整个指针的长度是地址的 2 倍。假设前半段为 A,后半段为 B。

详解看

https://www.cnblogs.com/xianyufpga/p/13513025.html

2、快到慢传输脉冲

这就是跨时钟域问题,首先区分为单bit还是多bit跨时钟问题(由于是脉冲信号pulse,故单bit)。第二个区分:快-》慢,还是慢--》快。问题:由快到慢,当发送时钟频率高于接收时钟频率,而跨时钟域的信号脉冲宽度等于发送端时钟的一个时钟周期,接收时钟有可能漏采或采集到亚稳态。

详解:方法,脉冲展宽法和握手信号法。脉冲展宽法,将脉冲信号转换为沿信号再转换为脉冲信号实现从单bit从快时钟到慢时钟的转换。

情况1:单bit从慢时钟--->快时钟,打两拍。

情况2:单bit从快到慢时钟,将脉冲信号转换为沿信号(增加一个信号src_state,让第一个脉冲信号为src_state的上升沿,第二个为下降沿。依次交替)-->脉冲信号(脉冲同步)

达尔闻说----求职系列91

单比特跨时钟域问题详解(大疆FPGA逻辑岗A卷)

3、a, ,b, c, d, 求出第2大和第3大之和--- min(max(a,b), max(c,d)) + max(min(a,b), min(c,d))

4、对全志的看法,有收到其他offer么

我自己面试全志的经历:

1. 重点询问我做的RGB家电显示项目,如我做了那些模块?

答:做了LCD显示控制模块和SPI接收数据模块

2. LCD显示模块的行控制信号和场控制信号是怎么生成?

回答首先根据VESA标准的时序参数,如行同步信号表示一行像素数据的开始,通过行计数器cnt_h计数到一行的总像素数799, 场同步信号表示每一帧的起始点,即所有行像素扫描完,垂直计数器cnt_v表示每扫描完一行加1.接着是有效信号dvalid,首先得区分屏幕(800*525)大小大于显示有效区域(640*480),在有效区域内,在像素时钟驱动下拉高。最后就是将行/场控制信号和有效区域的信号拉高和像素数据(RGB565)输出,驱动LCD显示。LCD屏接口有三种,一是TTL接口,二是LVDS接口,三是TMDS接口;本次使用就是TTL接口,有数据信号,时钟信号,行/场控制信号。

3. LCD的驱动时钟多少?数据位宽及格式

LCD驱动时钟为12.5M,数据位宽16比特(565),视频传输带宽 = 视频分辨率*帧率*像素数据位宽;即480*272*25*16=52Mhz. SPI时钟速率10M

4. LCD的VGA时序,若是给的像素时钟不满足这个时序?

那就会无法产生标准时序,不能显示图像,仿真的控制信号和有效信号都不能产生

5. 三个基础题

(1)wire [4:0] a [3:0];表示什么意思

memory类型数据,表示数据位宽为5比特深度为4的寄存器/4个位宽为5的数组

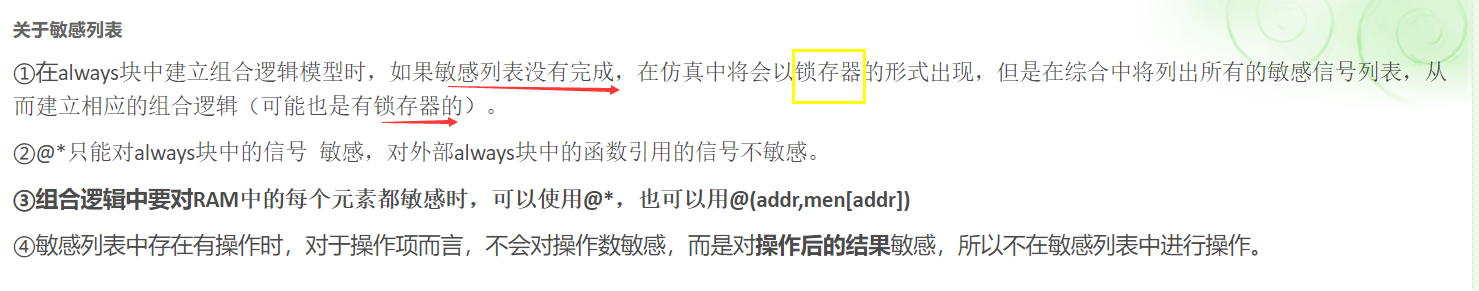

(2 )在组合逻辑中,有四个输入信号,作为敏感列表 ,若只给其中的两个信号赋值,其余两个没操作会咋样?

在仿真中会出现锁存器,在综合后会出现四个信号的敏感列表,还是可能会出现锁存器

(3)跨时钟域处理的方法:

扩展一下消除亚稳态:

HR面:

1、是考研还是保研,为什么会保研失败

2、遇到的比较大的挫折,是怎么解决的

3、最有成就感的一件事

4、对工作地点如何看,如何选择公司,家人会不想你离家太远么

5、坚持下来的一件事

6、最近看的三本书

7、别人对你的哪个评价让你感到难过,恶评

8、参加竞赛的过程中如何分工,有没有在一个问题上有过争吵,如何解决团队合作的分歧的

9、为什么本科阶段没有拿过奖

10、有没有一件事没有在该完成的时间点之后完成

芯动科技-------面试公司6

补充:脚本题,五分频,两个加法器兵乓。

后面又问了相量子大佬,他回答:

奇数分频,建立保持时间计算,三段状态机,时钟无毛刺切换,跨时钟域这些好好看看

问问尤老师,看看咸鱼FPGA博客,再自己查查资料。

海光面试--------面试公司6

面试时间-----30分钟

先是自我介绍,后面是自己介绍一个项目,之后他就问了CPU方面的基础问题。

1.在跨时钟域处理中,FIFO深度为32,读写地址位宽多少,怎么判断写满标志,读满标志?

读写地址位宽 = (log232)+1=6bit, 最高1bit用来区分读写快慢的问题,最高位为空满标志信号,对于异步FIFO的跨时钟域处理,要设立读写地址指针来判断写满标志和读满标志

(2)读空判断

默认是先写后读,读追上了写,就是读空了。因此读空标志为【读写地址相同】。读空指的是写指针和读指针指向同一个地址的时刻。

写满判断

默认是先写后读,

因此可以设置一个写指针 wr_addr_ptr 和 读指针 rd_addr_ptr,其位宽比读写地址多1位,整个指针的长度是地址的 2 倍。

写比读块,并且快了一倍,之间的距离正好是一个fifo的深度这时候就是写满,并且读地址和写地址最高位不等,低位全部相等。提炼一下就是:“读写的最高位不同,其余位相同”时,处于写满状态。举例如下:读写指针的关系就好比A,B两个田径运动员在一环形跑道上赛跑一样,当B运动员领先A并整整超前一圈时,A,B两人的地点相同,此种情况对应于读写指针指向了同一地址,但写指针超前整整一圈,FIFO被写满。

11.19号--芯原 -----面试公司7

之前在11月初,找了拿到芯原offer的本校同学内推,直接发给了HR,过了两周才收到HR打电话问offer情况和邀约面试,由于芯原大家印象不错,我也准备去,然后就面试了。笔试是和之前网上差不多,有考芯原的企业文化还有service。笔试参考:(41条消息) 芯原数字IC笔试题(每年题型类似)_gemengxia的博客-CSDN博客_芯动科技笔试题

还是有20%的新题,考了综合,功耗报告,还有单比特脉冲的展宽等,最后的任选一题,基本也是新的,有FPGA和SOC等。

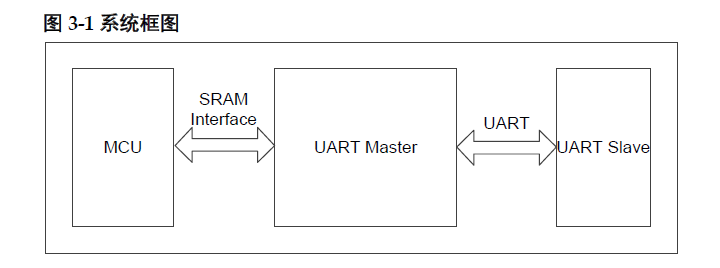

面试: 首先自我介绍,后面重点问了做的串口IP设计,一个是功能,原理和所负责的模块。还问了时钟频率任意啥意思。串口IP的架构,即用SDRAM接口接收主机(MCU或PC)的命令或数据,通过串口IP这个桥梁,发送到串口,最后下发给从机(如FPGA)。

串口IP的作用?

UART Master IP 起到一个“桥梁”的作用。主控制器将指令或数据通过同步SRAM 接口传送给UART Master IP,然后UART Master IP 通过UART

下发给UART Slave

问了SRAM的功能?

UART Master IP 可通过同步SRAM 接口接收主控制器的指令或数据,也可以返回数据给主控制器。

SPI是同步还是异步?

SPI---------同步通信(有同步时钟);串行通信;全双工;主从通信(某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机)。(我当时头铁答了异步)

所谓的时钟频率任意指什么?

时钟频率任意指,不同的波特率就有不同参考时钟。他们关系为一一对应,符合公式:参考时钟频率 = 采样倍数(8/16/32)*波特率*分频系数(最小为2).参考时钟范围为0-64M,一般波特率越大所需的时钟频率越大。

采样时钟咋产生?

通过设计一个baudset模块来产生,通过输入的参考时钟确定分频系数产生对应的计数器,利用计数器分频产生采样时钟,作为接受端和发送端的进行一比特数据位采样时的时钟。

误码率检测?

奇偶校验。Verilog代码,增加一个奇校验位/偶校验位,和数据位异或(利用偶数个1异或结果为0,奇数个1则为1),最后判断发送端和接受端的误码率标志位是否一致,就能确定数据传输的错误。

第二部分问了USB

一问了USB协议的大致内容

二问了USB的三种速度模式

三问了utmi接口

第三部分为RGB家电显示模组

1.所做的模块

2.SPI的传输速率范围1-100M,为啥最多100M

3.SPI为同步传输,详细介绍时钟翻转和极限等

https://www.cnblogs.com/xianyufpga/p/11341809.html

4.问了DDR3和千兆以太网的设计过程

5.在做的过程遇到的问题

6.四六级过没过

问题还是蛮多的也很综合