CPU的缓存

存在三级:

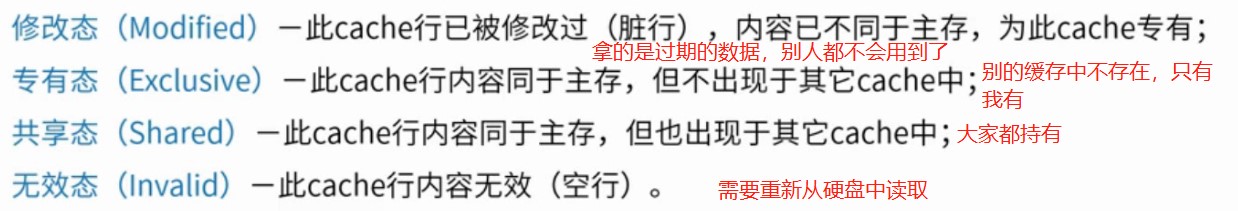

注意:没有CPU都有缓存自己的L1和L2,但是L3是多核共用的。 CPU读取数据:L1>L2>L3>内存>硬盘 多个缓存中的数据一致性问题: 多个缓存同时持有一个数据时,谁的修改会被承认呢,CPU厂商们讨论出一个协议,名叫MESI协议。 MESI 协议为缓存中数据添加了四种状态:

多处理器是:CPU对缓存中的数据改动后要通知给别的cpu。 CPU运行时指令重排 CPU会将指令排序后执行。(不会改变结果)由于L3缓存是共享的。为了达到不等待的目的,CPU会控制指令的执行顺序。为了提高并行效率。 内存屏障 CPU提供了两个内存屏障指令: 1:写内存屏障:对缓存的修改要强制的同步到主内存之后才能被别的CPU使用。 2:读内存屏障:强制让缓存去同步主内存中的数据。