TW9912视频转换芯片使用

TW9912是Intersil(后被瑞萨收购)生产的一款实现模拟视频信号转为数字视频信号的芯片,对于隔行或者逐行输入的视频信号该芯片均支持逐行输出bt.656形式的8bit(4:2:2)数字视频信号。

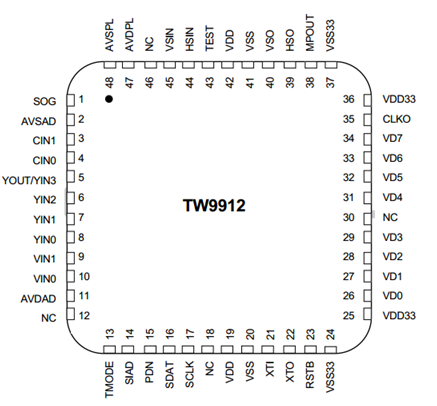

芯片封装图如下:

1、输入通道引脚YIN0~YIN3与CIN0~CIN1、VIN0~VIN1区别

对于PAL或者NTSC制式的视频信号通常有两种传输基带信号CVBS和S-video。

对于CVBS信号格式可选择YIN0~YIN3;

与rensa技术沟通确认,对于pal制式CVBS只能与YIN0~YIN3连接,对于pal制式S-video信号只能与Vin或Cin连接;

2、该芯片支持IIC总线接口对芯片寄存器进行配置。一般CPU/FPGA/ZYNQ作为IIC借口的host端。tw9912芯片作为IIC接口的从设备,注意:tw9912作为从设备时slave address定义:

注意:从设备地址定义为7bits数据,在IIC接口相应驱动函数中要将此地址右移一位才是真实的从地址。此项至关重要。

3、经过实际调试图像有显示,TW9912正确配置逐行输出bt.656数字视频的各寄存器数值如下:

{0xFF ,0x00}, //Page 00

{0x01 ,0x79}, //R, HLOCK、SLOCK 置位, FIELD偶数场被解码; VLOCK,DET50检测50HZ视频源

{0x02 ,0x40}, //FC27 输入时钟频率为27M IFSEL 复合视频信号解码 YSEL通道选择YIN0;

{0x03 ,0x20}, //输出控制寄存器1 LLC output模式;All output on;

{0x04 ,0x00}, //color killer默认

{0x05 ,0x12}, //zyp, 图像显示不在滚动。实际不反向配置是0x12

{0x06 ,0x03}, //模拟控制寄存器 0默认;Chroma ADC关闭, V channel ADC关闭;

{0x07 ,0x12}, //cropping 寄存器默认

{0x08 ,0x12}, //默认12

{0x09 ,0x20}, //vertical active寄存器

{0x0A ,0x0E}, //horizontal delay寄存器

{0x0B ,0xD0}, //horizontal active寄存器

{0x0C ,0xCC}, //控制寄存器 默认值

{0x0D ,0x15}, //cc/wss控制寄存器 默认值15

{0x10 ,0x00}, //brightness 控制寄存器 默认值0 数据不受影响

{0x11 ,0x64}, //contrast 控制寄存器 默认值64

{0x12 ,0x11}, //sharpness控制寄存器 默认值11

{0x13 ,0x80}, //默认值80

{0x14 ,0x80}, //默认值80

{0x15 ,0xDD},

{0x17 ,0x30}, //默认值30

{0x18 ,0xFF}, //图像无差别

{0x1A ,0x60}, //60与10没什么区别

{0x1B ,0x00},

{0x1C ,0x0F}, //07/0F图像与1F没什么区别

{0x1D ,0x7F}, //standard识别 默认值7F

{0x1E ,0x08}, //zyp, 默认

{0x1F ,0x00}, //保留

{0x20 ,0x50}, //clamping gain默认值

{0x21 ,0x42}, //individual agg gain默认值

{0x22 ,0xF0}, //agg gain默认值

{0x23 ,0xFF}, //zyp, 图像与D8看不出什么差别

{0x24 ,0xBC}, //clamp level默认值

{0x25 ,0xB8}, //sync amplitude默认值

{0x26 ,0x44}, //sync miss count register默认值

{0x27 ,0x38}, //clamp position寄存器默认值

{0x28 ,0x00}, //vertical控制1 默认值

{0x29 ,0x00}, //vertical控制2 默认值

{0x2A ,0x78}, //color killer level control默认值

{0x2B ,0x44}, //comb filter control默认值

{0x2C ,0x30}, //luma delay和hfilter control默认值

{0x2D ,0x16}, //16/18/1C/1E

{0x2E ,0xA5}, //默认值

{0x2F ,0x44}, //zyp,图像没什么变化

{0x33 ,0x05}, //15/25闪动/35间隔闪动/45/55闪/65闪/

{0x34 ,0x1C}, //zyp ,PAL ID

{0x35 ,0x00},

{0x36 ,0x03}, //zyp,默认03 偶补偿

{0x37 ,0x28}, //zyp,默认0x28

{0x38 ,0x30}, //zyp, deinterlacer sync 看图像显示凑得数值,未了解其真正含义,不同数值图像左右会有消音区域;

{0x40 ,0x00},

{0xC0 ,0x01}, //LLPLL input 控制寄存器01选择晶振时钟

{0xC2 ,0x01},

{0xC3 ,0x03},

{0xC4 ,0x5A},

{0xC5 ,0x00},

{0xC6 ,0x20},

{0xC7 ,0x04},

{0xC8 ,0x00},

{0xC9 ,0x06},

{0xCA ,0x06},

{0xCB ,0x30},

{0xCC ,0x03}, //zyp

{0xCD ,0x54},

{0xD0 ,0x00},

{0xD1 ,0xF0},

{0xD2 ,0xF0},

{0xD3 ,0xF0},

{0xD4 ,0x00},

{0xD5 ,0x00},

{0xD6 ,0x10},

{0xD7 ,0x70},

{0xD8 ,0x00},

{0xD9 ,0x04},

{0xDA ,0x80},

{0xDB ,0x80},

{0xDC ,0x20},

{0xE0 ,0x00},

{0xE1 ,0x45}, //zyp, 与0x49对比图像没什么差别

{0xE2 ,0xD9}, //ADC控制1 电气标准

{0xE3 ,0x00}, //??

{0xE4 ,0x00}, //??

{0xE5 ,0x00}, //??

{0xE6 ,0x00}, //ADC控制5

{0xE7 ,0x2A}, //ADC控制6

{0xE8 ,0x1F}, //zyp, 与0f显示没什么区别

{0xE9 ,0x67}, //zyp, 67/77显示图像来看颜色接近正确,有条纹。ila抓取hs、vs很乱;65/63/均无图像显示

//{SEQUENCE_END_656, 0x00}