FIFO (First Input First Output),中文名为先入先出存储器。顾名思义,FIFO 的数据进出方式为先入先出。FIFO 常用用在两个不同步的信号接口之间作为数据缓冲器。理想情况下 FIFO 的读写应该是两个时钟驱动的独立的信号。要实现这样的功能必须用到双口 RAM。但 FPGA 不同于 ASIC,双口 RAM 无法实现。所以这里的 FIFO是一个单端口的同步 FIFO,约定 FIFO 位宽为 8 bit,长度为 16。

Altera Cyclone IV FPGA 内部提供了双口 RAM 的 IP 核,具体实现方式应该是内嵌的硬核。调用 IP 核的方式不利于学习,也不利于程序的移植,本篇暂不做讨论。

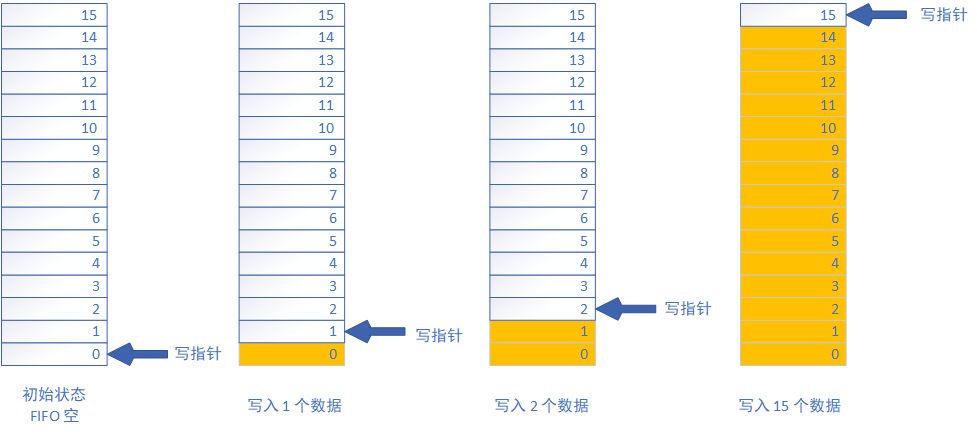

FIFO 的读写方式如下图所示:

可以看出几个需要注意的问题:

- 读写指针都是独立的。

- 读写指针都是循环的,满 16 归零。

- 当读写指针都在 0 位置的时候,要注意区分满和空这两种截然不同的状态。

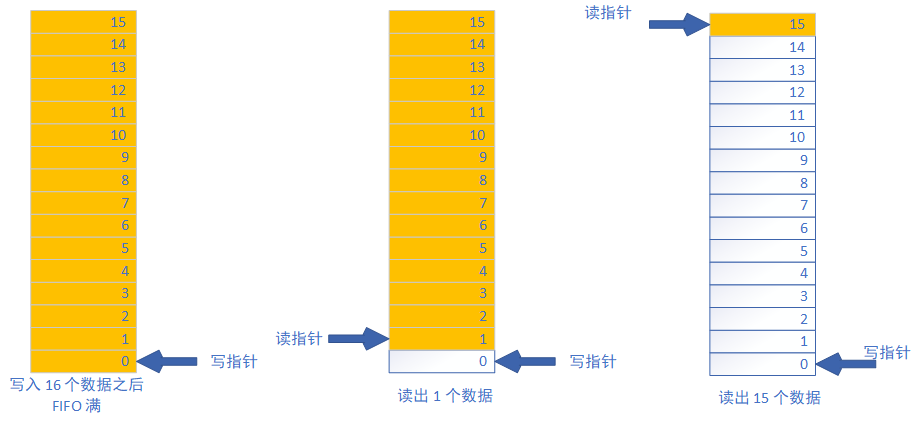

要实现 FIFO,首先要实现的是寄存器组。一个8 * 16 位的寄存器组。

代码如下:

这个逻辑比较简单,在时钟的上升沿存储数据到对应的端口,接下来编写测试代码来测试这个寄存器组:

测试激励代码截图((⊙﹏⊙) TestBench这个我写的不太好):

下面是仿真结果:

Quartus 在调用 Modelsim 的时候总是自作主张的添加信号到波形窗口,然而总是掉了那么几个,视频中删掉原来的信号信息,增加需要的信号到波形窗口,并重新仿真一次。

有了寄存器组,那么FIFO 就呼之欲出了。

下面是 FIFO 的代码:

这里使用波形仿真,仿真的结果如下:

好了,FIFO 部分到此结束,(●'◡'●)。