/==========翻译S3C2440存储控制器部分================/

5 存储控制器

概述

S3C2440内存控制器为外部存储访问提供内存控制信号。

S3C2440A有如下特征:

大端/小端(由软件选择)

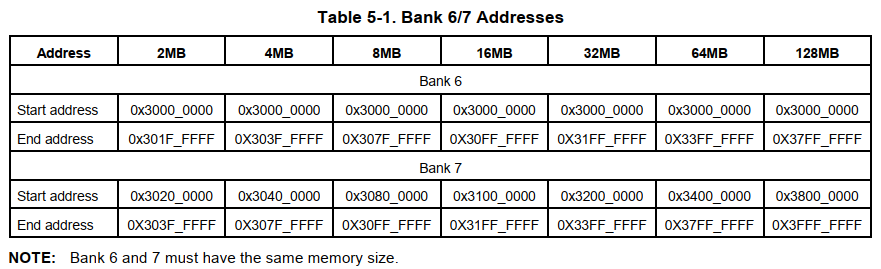

地址空间:每块由128MB存储空间,一共有8块达1GB。

除了空间0外,其他所有的空间都能通过编程控制访问大小。

总共有8个内存空间

其中有6个空间用来ROM,SRAM等。

其余两个空间用来ROM,SRAM,SDRAM等。

7个内存空间有固定的起始地址。

1个内存空间起始地址是可变的,并且内存大小是可编程的。

所有内存空间的访问周期都是可编程的。

外部等待以延长总线周期。

支持SDRAM的自动刷新和关机模式。

例如“nGCS1”,这是一个片选信号,

访问某块内存,相应的片选信号拉低,避免内存访问冲突。

功能描述

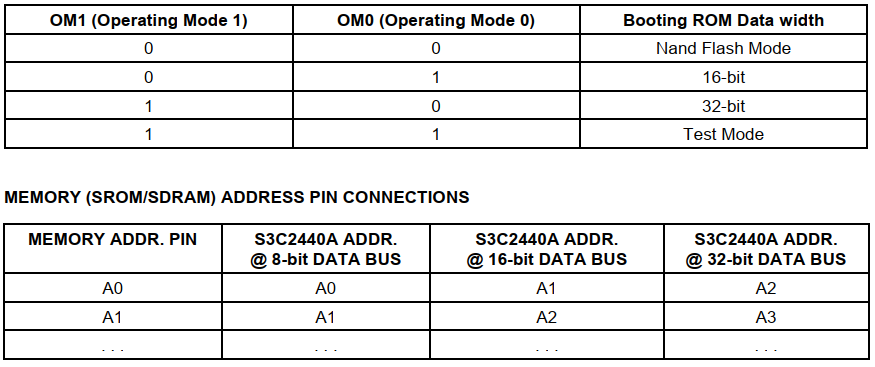

内存空间0总线宽度

内存空间0的数据总线宽度应配置为16位或32位。

因为内存空间0用来引导ROM,

在第一个ROM访问之前,bank0的总线宽度要被确定下来,

这些都取决于复位时逻辑电平OM[1:0]。

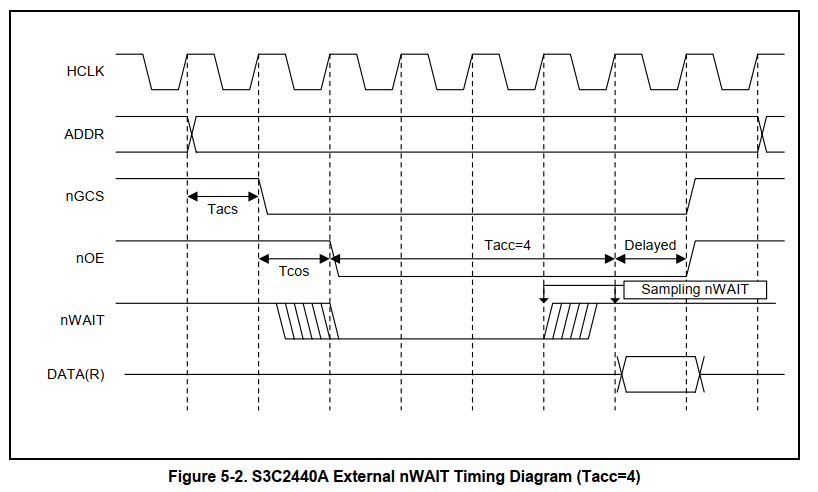

nWAIT引脚操作

如果使能每个内存空间的WAIT位,

nOE的持续时间应该被延长,

在内存空间是活动时,通过外部的nWAIT引脚。

nWAIT是从facc-1进行检查。

在采样nWAIT是高电平后,

在下一个时钟周期时,nOE会失效。

nWE信号与nOE信号有相同的关系。

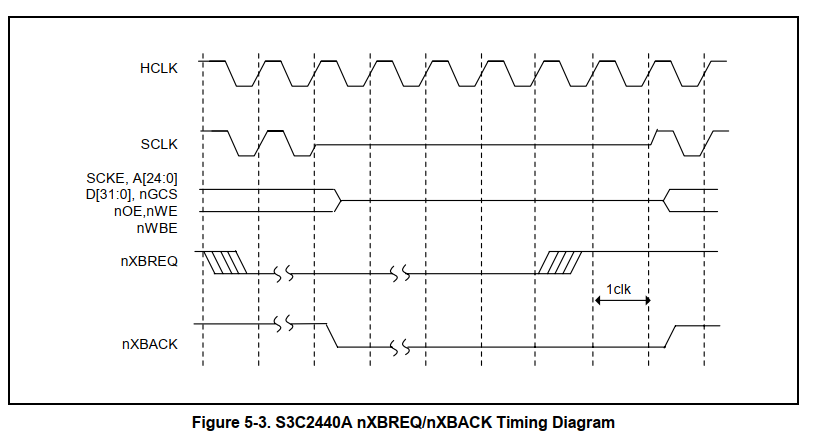

nXBREQ/nXBACK引脚操作

如果nXBREQ是断言的,

S3C2440A将通过降低nXBACK来响应。

如果nXBACK=L,

地址/数据总线与内存控制信号就会是一种高阻态,如表1-1所示。

在nXBREQ失效后,nXBACK也会失效。

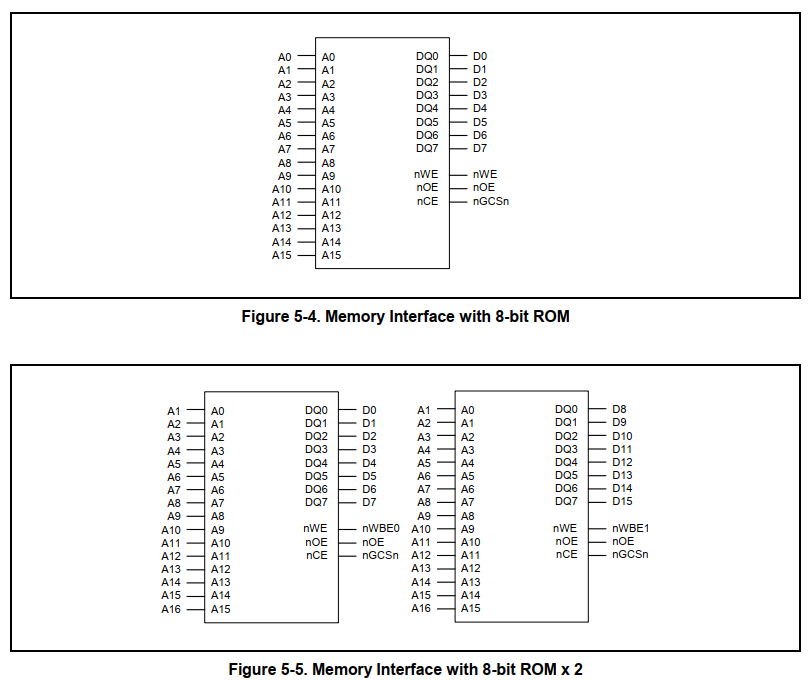

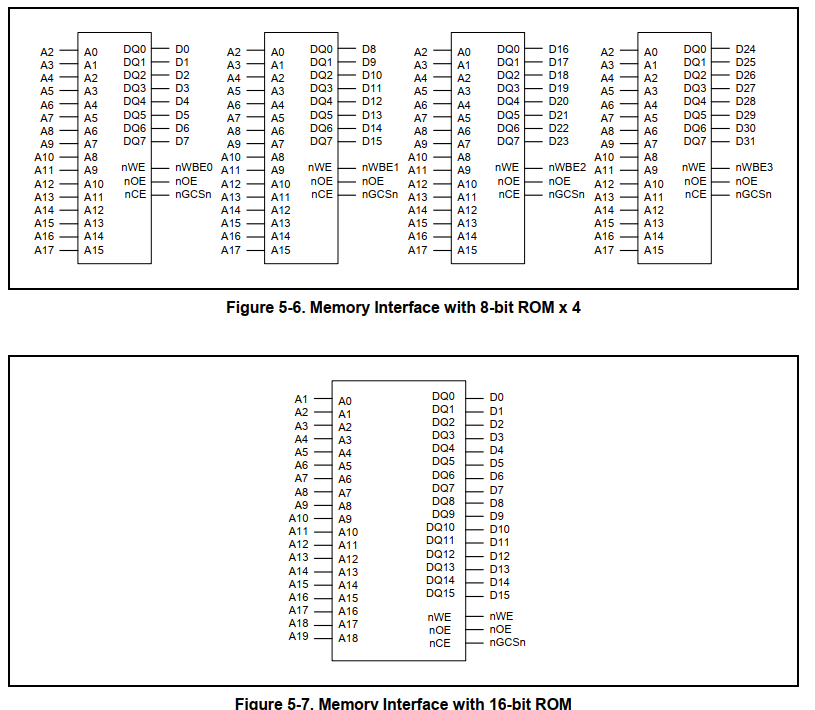

ROM内存接口实例

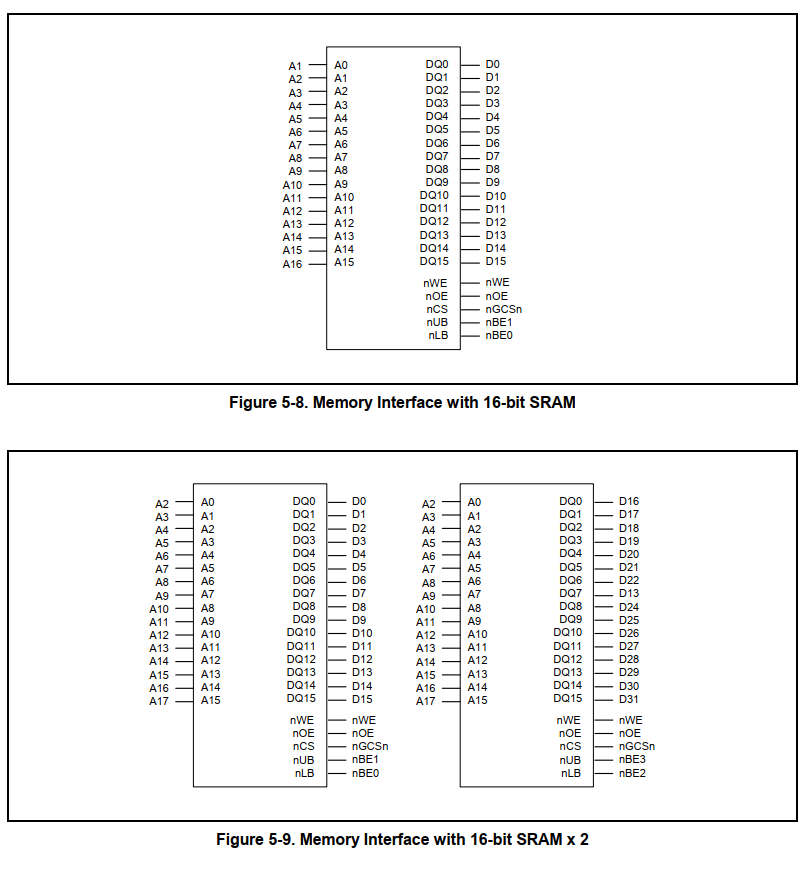

SRAM内存接口实例

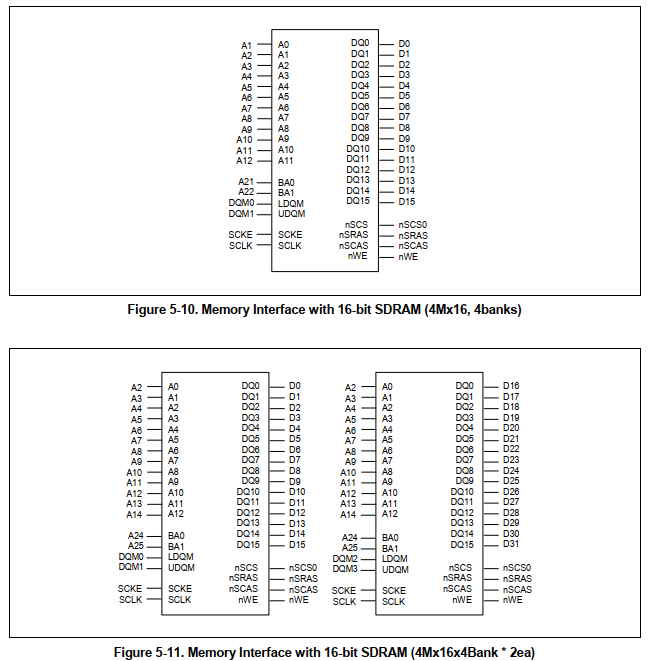

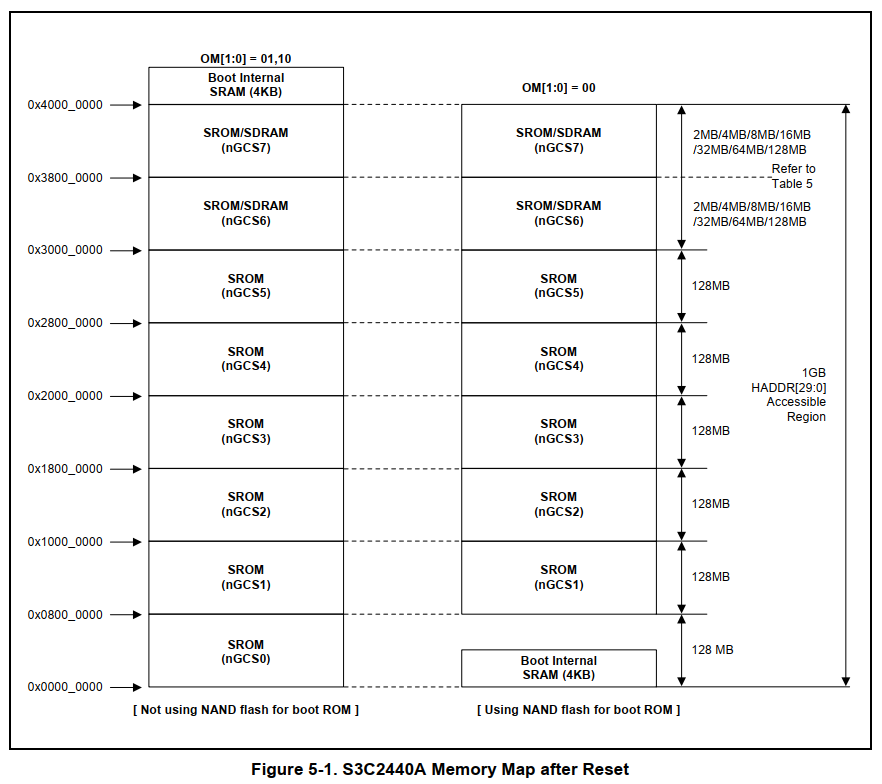

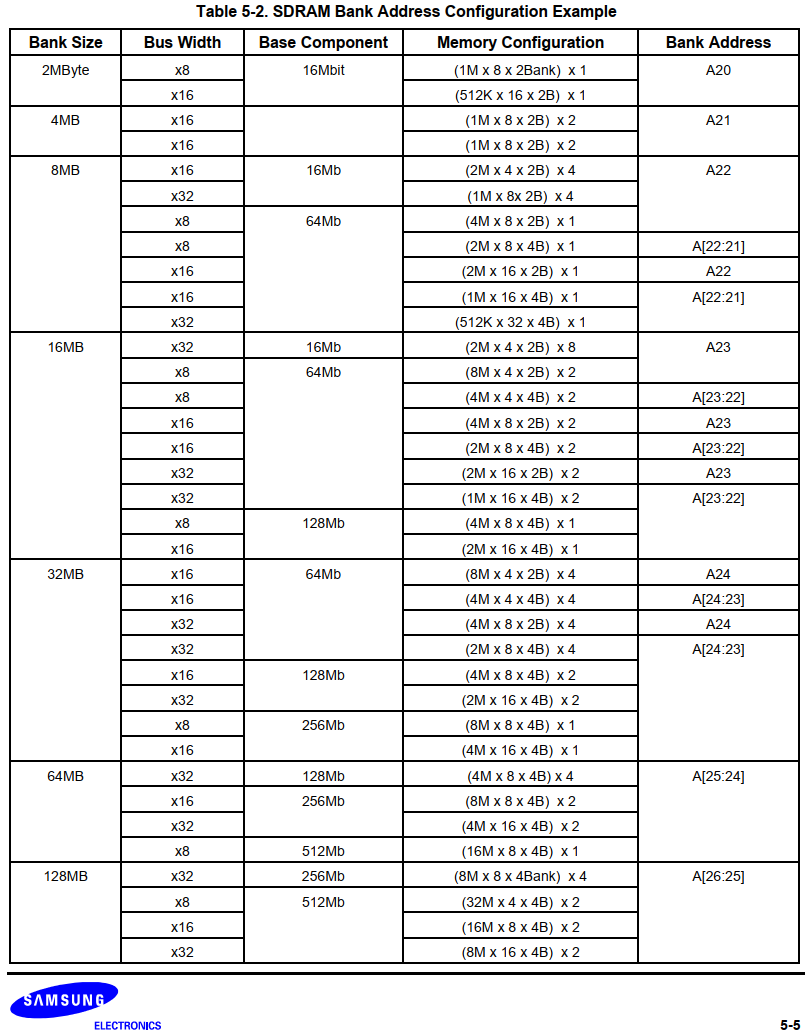

SDRAM内存接口实例