Synopsys逻辑工艺库(DC综合)

逻辑库包括仅与综合过程有关的信息且通过DC用于设计的综合和优化。

这一信息包括引脚到引脚的时序、面积、引脚类型和功耗以及其他DC需要的必须数据。

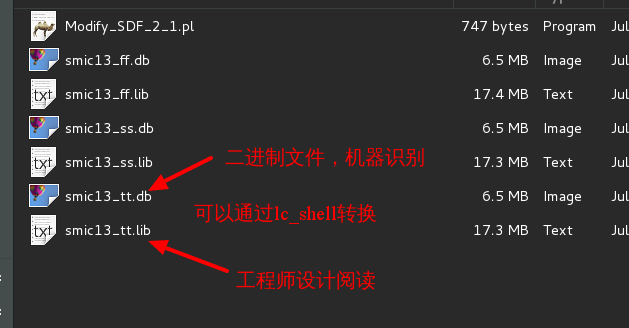

逻辑库是一个文本(通常扩展名".lib"),通过使用Library Compiler(LC)编译生成带有扩展名名".db"的二进制文件。

以SMIC的逻辑综合库为例:库文件下载地址

逻辑库基础

逻辑库包括一下信息:

- 库类

- 库级属性

- 环境描述

- 单元描述

库类

库类语句指定库名,接着是一左大括号。右大括号是库文件的最后项,大括号里的内容都是整个库类描述的一部分。

以下以smic13HT_ss.lib为例

library ( smic13HT_ss ) {

}

库级属性

库级属性是作用与整个库的语句,通常包括库特征,如工艺类型、日期、版本和用于整个库的默认值。

library ( smic13HT_ss ) {

delay_model : table_lookup ;

in_place_swap_mode : match_footprint ;

time_unit : "1ns" ;

voltage_unit : "1V" ;

current_unit : "1uA" ;

pulling_resistance_unit : "1kohm" ;

leakage_power_unit : "1nW" ;

capacitive_load_unit ( 1,pf ) ;

slew_upper_threshold_pct_rise : 90.00 ;

slew_lower_threshold_pct_rise : 10.00 ;

slew_upper_threshold_pct_fall : 90.00 ;

slew_lower_threshold_pct_fall : 10.00 ;

input_threshold_pct_rise : 50.00 ;

input_threshold_pct_fall : 50.00 ;

output_threshold_pct_rise : 50.00 ;

output_threshold_pct_fall : 50.00 ;

nom_process : 1 ;

nom_voltage : 1.08 ;

nom_temperature : 125 ;

revision : 0.1 ;

date : "Tue Oct 21 11:08:22 CST 2003" ;

comment : "Copyright 2003 by Verisilicon Microelectonics (Shanghai) Co., Ltd." ;

......

......

}

环境描述

库中定义的环境属性对于温度、电压和制造工艺的偏差建模,它包括比例因子(降低标称值)、时序范围模型和工作条件。此外,环境描述也包含DC用于估算连线延时的线载模型。

- 比例因子

比例因子或K因子是乘数,它提供基于工艺、电压和温度(简称为PVT)的偏差减少延时值的方法。

k_temp_hold_fall : -0.000117 ;

k_temp_hold_rise : 0.000224 ;

k_volt_hold_fall : -1.134170 ;

k_volt_hold_rise : -1.508669 ;

k_temp_setup_fall : -0.000117 ;

k_temp_setup_rise : 0.000224 ;

k_volt_setup_fall : -1.134170 ;

k_volt_setup_rise : -1.508669 ;

k_temp_cell_fall : -0.000117 ;

k_temp_cell_rise : 0.000224 ;

k_volt_cell_fall : -1.134170 ;

k_volt_cell_rise : -1.508669 ;

k_temp_fall_propagation : -0.000117 ;

k_temp_rise_propagation : 0.000224 ;

k_volt_fall_propagation : -1.134170 ;

k_volt_rise_propagation : -1.508669 ;

k_temp_fall_transition : -0.000117 ;

k_temp_rise_transition : 0.000224 ;

k_volt_fall_transition : -1.134170 ;

k_volt_rise_transition : -1.508669 ;

......

......

-

工作条件

库中定义的工作条件集指定了工艺、温度、电压和RC树模型,它们用于设计的综合与时序分析中。

operating_conditions ( WORST ) {

process : 1 ;

voltage : 1.08 ;

temperature : 125 ;

}

-

时序范围模型

timng_rang模型提供了额外的基于指定工作条件的计算信号到达时间的能力,Synopsys提供这一能力是为了适应优化设计的工作条件的波动。在时序分析中,DC使用时序范围来计算信号的到达时刻。

-

线载模型

wire_load(线载)类包含DC在设计的布图前阶段用来估计互连线延时的信息。通常工艺库包括一些适合不同逻辑大小的模型,这些模型定义capacitiance、resistance和area因子。另外,wire_load类也为所考虑的逻辑指定了slope和fanout_length。

wire_load ( "area_zero" ) {

resistance : 0.00034 ;

capacitance : 0.00022 ;

area : 0.00000 ;

slope : 19.0476 ;

fanout_length ( 1,0 ) ;

fanout_length ( 2,0.0 ) ;

fanout_length ( 3,0.0 ) ;

fanout_length ( 4,0.0 ) ;

fanout_length ( 5,0.0 ) ;

fanout_length ( 6,0.0 ) ;

fanout_length ( 7,0.0 ) ;

fanout_length ( 8,0.0 ) ;

fanout_length ( 9,0.0 ) ;

fanout_length ( 10,0.0 ) ;

fanout_length ( 11,0.0 ) ;

fanout_length ( 12,0.0 ) ;

fanout_length ( 13,0.0 ) ;

fanout_length ( 14,0.0 ) ;

fanout_length ( 15,0.0 ) ;

fanout_length ( 16,0.0 ) ;

fanout_length ( 17,0.0 ) ;

fanout_length ( 18,0.0 ) ;

fanout_length ( 19,0.0 ) ;

fanout_length ( 20,0.0 ) ;

}

单元描述

库中的每个单元都包含了描述功能、时序和其他与每个单元相关信息的多种属性

cell ( BUFCLKHD10XHT ) {

area : 19.668 ;

cell_leakage_power : 2.76391 ;

cell_footprint : bufclk ;

pin ( A ) {

direction : input ;

capacitance : 0.0107633 ;

}

参考资料

[1]. 高级ASIC芯片综合