若计数器的输入脉冲的频率为f,则输出的Q0、Q1、Q2和Q3端输出脉冲的频率依次为1/2f,1/4f,1/8f/1/16f。

Verilog 代码实现

预分频器代码 prescaler.v

module prescaler(

output scaler16_o,

output scaler8_o,

output scaler4_o,

output scaler2_o,

input clk,

input rstn,

input en_i

);

reg [3:0] cnt;

reg [3:0] cnt_next;

always@(posedge clk, negedge rstn)

begin

if(!rstn)

cnt <= 4'b0;

else

cnt <= cnt_next;

end

always@(*)

begin

if(en_i)

if(cnt == 4'b1111)

cnt_next = 4'b0;

else

cnt_next = cnt + 1'b1;

else

cnt_next = cnt;

end

assign scaler16_o = cnt[3];

assign scaler8_o = cnt[2];

assign scaler4_o = cnt[1];

assign scaler2_o = cnt[0];

endmodule

testbench prescaler_tb.v

module prescaler_tb;

reg clk;

reg rstn;

reg en_i;

wire scaler2_o;

wire scaler4_o;

wire scaler8_o;

wire scaler16_o;

initial

begin

clk = 0;

rstn = 1;

#30 rstn = 0;

#100 rstn = 1;

en_i = 1;

repeat(100) @(posedge clk);

$finish;

end

always #20 clk = ~clk;

initial begin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars();

end

prescaler u_prescaler(

.scaler16_o(scaler16_o),

.scaler8_o(scaler8_o),

.scaler4_o(scaler4_o),

.scaler2_o(scaler2_o),

.clk(clk),

.rstn(rstn),

.en_i(en_i)

);

endmodule

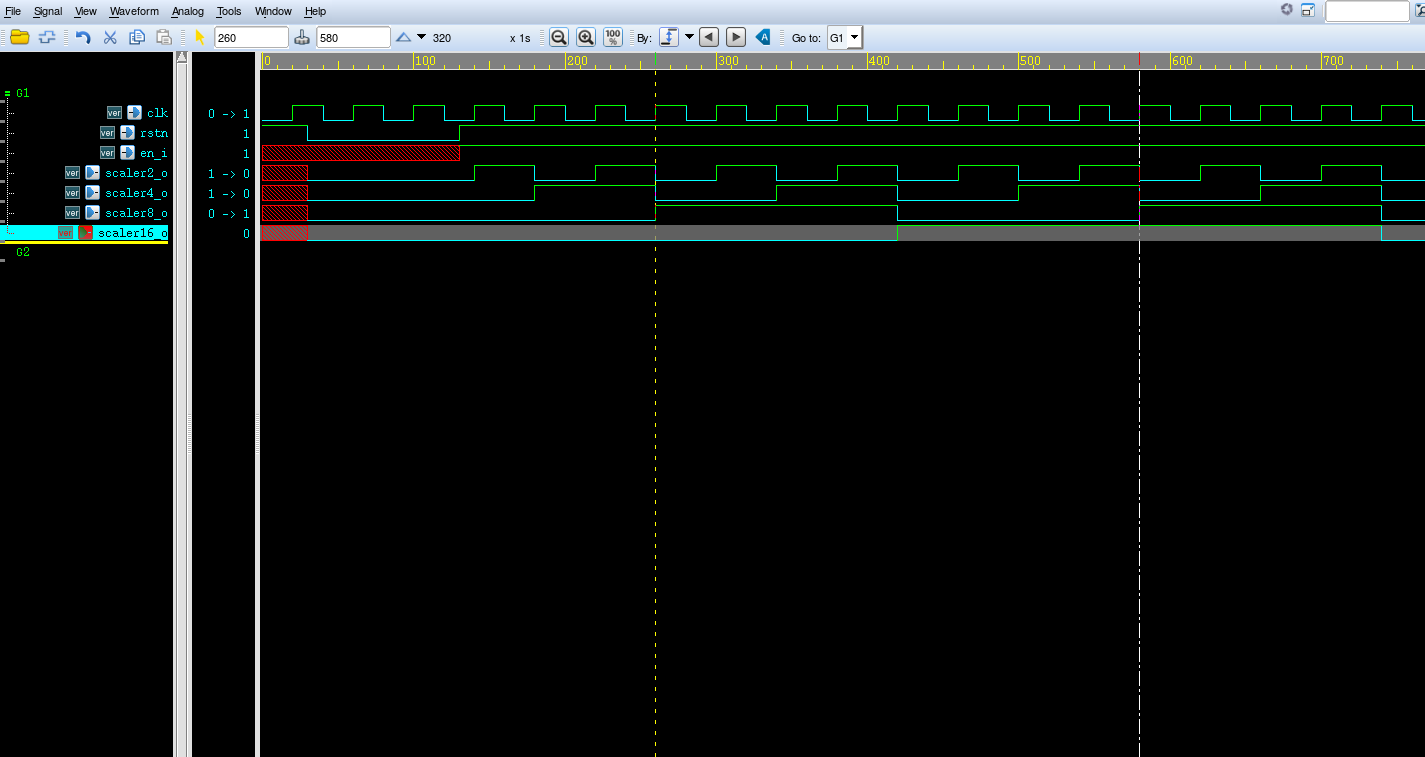

仿真结果

参考资料

[1] 数字电子技术基础(第五版) 阎石主编