来源:http://www.elecfans.com/baike/bandaoti/bandaotiqijian/20100323203306.html

数字PLL,什么是数字PLL

数字PLL

PLL的概念

我们所说的PLL,其实就是锁相环路,简称为锁相环。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

目前锁相环主要有模拟锁相环,数字锁相环以及有记忆能力(微机控制的)锁相环。

PLL的组成

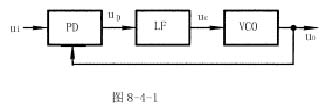

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。

锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成uD(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压uC(t),对振荡器输出信号的频率实施控制。

锁相环的工作原理

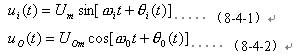

设外界输入的信号电压和压控振荡器输出的信号电压分别为:

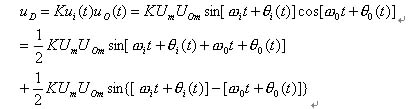

式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压uD为:

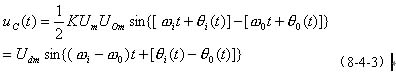

用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压uC(t)。即uC(t)为:

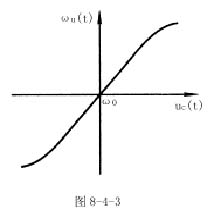

式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:

数字PLL的概念

所谓数字PLL,就是指应用于数字系统的PLL,也就是说数字PLL中的各个模块都是以数字器件来实现的,是一个数字的电路。

数字锁相环的优点是电路最简单有效,可采用没有压控的晶振,降低了成本,提高了晶振的稳定性。但缺点是和模拟锁相环一样,一旦失去基准频率,输出频率立刻跳回振荡器本身的频率;另外还有一个缺点,就是当进行频率调整的时候,输出频率会产生抖动,频差越大,抖动会越大于密,不利于某些场合的应用。

锁相环路已在模拟和数字通讯及无线电电子学的各个领域中得到广泛应用。随着大规模、超高速的数字集成电路的发展,为数字锁相环路的研究与应用提供了广阔空间。由于晶体振荡器和数字调整技术的加盟,可以在不降低振荡器的频率稳定度的情况下,加大频率的跟踪范围,从而提高整个环路工作的稳定性与可靠性。