什么是线与逻辑?需要和CMOS漏极开路门(Open Drain, OD)一起介绍。

通常CMOS门电路都有反相器作为输出缓冲电路,而在工程实践中,有时需要将两个门的输出端并联以实现“与”逻辑的功能称为“线与”逻辑,或者用于驱动大电流负载,或者实现逻辑电平变换。

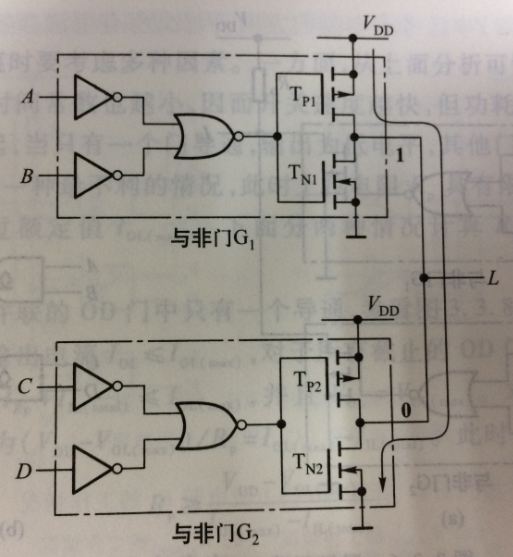

现在来考虑一种情况,如果将将两个CMOS与非门G1和G2的输出端连接在一起,如图1所示,并设G1的输出处于高电平,TN1截止,TP1导通;而G2的输出处于低电平,TN2导通,TP2截止,这样从G1的TP1端到G2的TN2端将形成一低阻通路,从而产生很大的电流,很有可能导致器件的损毁,并且无法确定输出是高电平还是低电平,这一问题就需要OD门来解决。

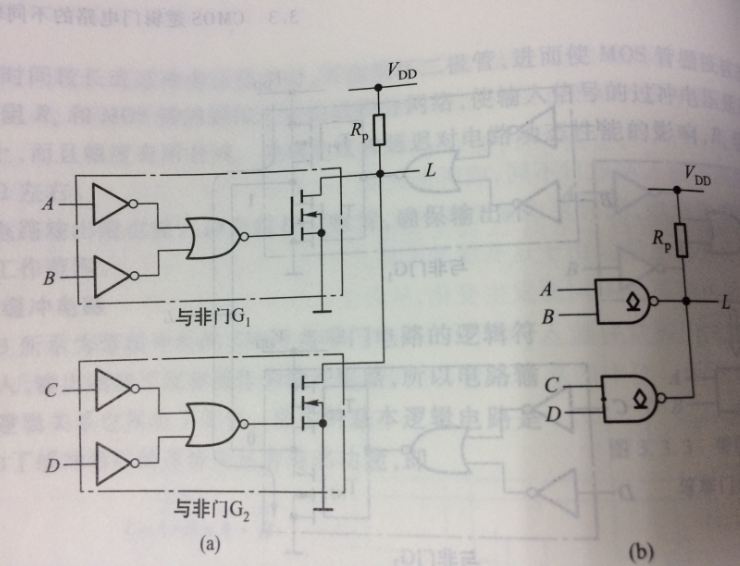

所谓漏极开路门是指CMOS门电路的输出只有NMOS管,并且它的漏极是开路的。使用OD门时必须在漏极和电源VDD之间外接一个上拉电阻(pull-up resister)RP。如图2所示为两个OD与非门实现线与,将两个门电路输出端接在一起,通过上拉电阻接电源。

当两个与非门的输出全为1时,输出为1;只要其中以输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)'(CD)'。

上拉电阻对OD门动态性能的影响:

当其他门电路作为OD门的负载时,OD门称为驱动门,其后所接的门电路称为负载门。由于驱动门的输出电容、负载门的输入电容以及接线电容的存在,上拉电阻势必影响OD门的开关速度,RP的值越小,负载电容的充电时间常数也越小,因而开关速度越快。但上拉电阻不能任意的减小,它必须保证OD门输出端的电流不能超过允许的最大值IOL(max)。对于74HC/74HCT系列CMOS电路,IOL(max)=4 mA,因此RP必须大于VDD/IOL(max)=5 V/4 mA = 1.25kΩ 。与普通CMOS电路相比,RP的值比PMOS管导通电阻大,因而,OD门从低电平到高电平的转换速度比普通CMOS门慢。

(摘自:《电子技术基础(数字部分)》第六版 康华光)