本文如果有错,欢迎留言更正;此外,转载请标明出处 http://www.cnblogs.com/IClearner/ ,作者:IC_learner

1、基本流程概述

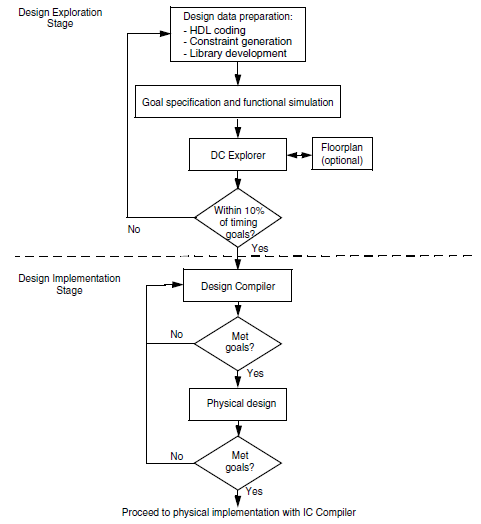

首先给三个图,一个图是高层次设计的流程图:

下面是我对这张图的理解:

① 设计之前,准备好库、HDL代码的思想、约束生成;然后根据设计思想用 RTL 源码详细地、完整地为设计建立模型、定义设计中寄存器结构和数目、定义设计中的组合电路功能、定义设计中寄存器时钟等等的设计规格和实现。

② 完成 RTL 源码设计之后,应让设计开发与功能仿真并行进行:

·在设计开发阶段,我们使用 DC 来实现特定的设计目标(设计规则和优化约束),以及执行默认选项的初步综合.

·如果设计开发结果未能在 10%的偏差范围内满足时序目标,则需要修正 HDL 代码,然后重复设计开发和功能验证的过程.

·在功能仿真中,通过特定的工具来确定设计是否能按如所需的功能工作.

·如果设计未能满足功能要求, 我们必须修改设计代码以及重复设计开发和功能仿真. 继续设计开发和功能仿真直至设计功能正确及满足小于 10%偏差的时序目标.

③ 使用 DC 完成设计的综合并满足设计目标.这个过程包括三个步骤,即综合=转化+逻辑优化+映射,首先将 RTL 源代码转化为通用的布尔等式,然后设计的约束对电路进行逻辑综合和优化,使电路能满足设计的目标或者约束,最后使用目标工艺库的逻辑单元映射成门

级网表,在将设计综合成门级网表之后,要验证此时的设计是否满足设计目标.如果不能满足设计目标,此时需要产生及分析报告确定问题及解决问题

④当设计满足功能、时序以及其他的设计目标的时候,需要执行物理层设计最后分析物理层设计的性能,也就是使用DC的拓扑模式,加入floorplan的物理信息后进行综合分析设计的性能。如果结果未能满足设计目标,应返回第三步.如果满足设计目标,则本部分设计周期完成.

一个图是DC在设计流程中的位置:

这个图将上面的流程图细化,着重与DC的部分,描述了使用DC进行逻辑综合时要做的事,同时,也是对前面的流程图解说的图形概述。在综合的时候,首先DC的HDL compiler把HDL代码转化成DC自带的GTECH格式,然后DC的library compiler 根据标准设计约束(SDC)文件、IP-DW库、工艺库、图形库、(使用拓扑模式时,还要加入ICC生成的DEF模式,加载物理布局信息)进行时序优化、数据通路优化、功耗优化(DC的power compiler进行)、测试的综合优化(DC的DFT compiler),最后得到优化后的网表。

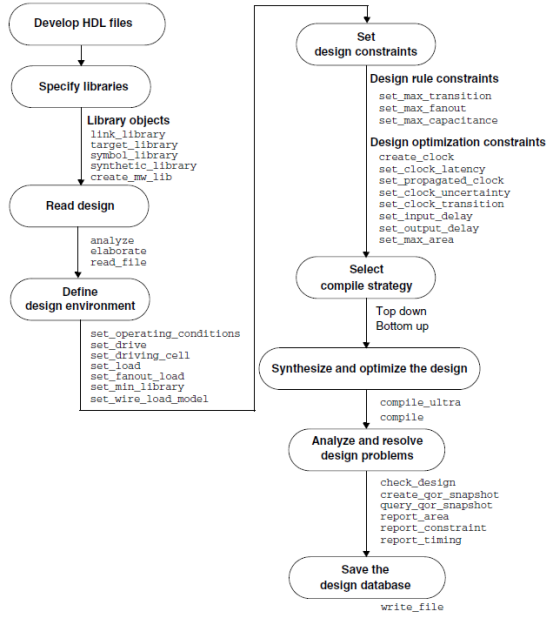

最后一个图是,使用DC进行基本的逻辑综合的流程图与相应的命令:

这个图给出了使用DC进行逻辑综合时的基本步骤,我们根据这个图运行DC,下面是这个图的具体解说:

①准备设计文件,DC 的设计输入文件一般为 HDL 文件。

②指定库文件,需要指定的库文件包括:

链接库(link library) 、目标库(target library) 、符号库(symbol library)、综合库(synthetic library)

下面是库的解释,具体的解释在后面有说,这里先进行简单地概述一下:

Link library & target library

Link library 和 target library 统称为 technology library(即工艺库,习惯称之为综合库),technology library 由半导体制造商提供,包含相关 cell 的信息及设计约束标准,其中:

Target library: 在门级优化及映射的时候提供生成网表的 cell,即DC 用于创建实际电路的库。

Link library: 提供设计网表中的 cell,可以跟target_library使用同一个库,但是 DC 不用 link library中的 cell 来综合设计。

当 DC 读入设计时,它自动读入由 link library 变量指定的库。当连接设计时,DC 先搜寻其内存中已经有的库,然后在搜寻由 link library 指定的库。

注:当读入的文件是门级网表时,需要把 link library 指向生成该门级网表的库文件,否则 DC 因不知道网表中门单元电路的功能而报错。 关于工艺库里面的具体内容,后面会专门进行说明。

Symbol library

Symbol library 提供 Design Vision GUI 中设计实现的图形符号,如果你使用脚本模式而不使用 GUI,此库可不指定 Symbol library

Synthetic library

即为 Designware library ,名字上翻译是综合库,但却常称之为IP库,而不是直译。特殊的 Designware library 是需要授权的(比如使用多级流水线的乘法器),默认的标准 Designware 由 DC 软件商提供,无需指定。

Create_mw_lib :主要使用DC的物理综合的时候,需要生成物理库

③读入设计 :

设计的读入过程是将设计文件载入内存,并将其转换为 DC 的中间格式,即GTECH 格式,GTECH 格式由“soft macros” 如 adders, comparators 等组成,这些组件来自 synopsys 的 synthetic lib,每种组件具有多种结构。

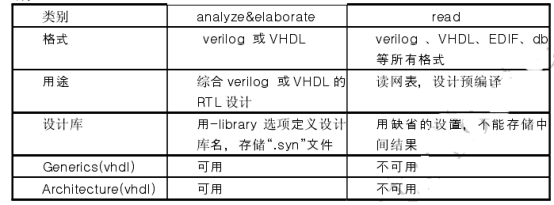

读入设计有两种实现方法实现方法:read 和 analyze & elaborate(实际上

read 是 analyze 与 elaborate 的打包操作 ),下面介绍二者在使用中的区

别:

从中可以看到,analyze & elaborate 可以自由指定设计库,并生成 GTECH中间文件前生成.syn 文件存储于 work 目录下,便于下次 elaborate 节省时间,我们一般选择 analyze & elaborate 的方法读入设计。

④定义设计环境:

定义对象包括工艺参数(温度、电压等),I/O 端口属性(负载、驱动、扇出),

统计 wire-load 模型,设计环境将影响设计综合及优化结果。

⑤设置设计约束:

设计约束包括设计规则约束和优化约束,设计规则约束(design rule

constraint)由工艺库决定,在设计编译过程中必须满足,用于使电路能按功能要求正常工作。设计优化约束定义了 DC 要达到的时序和面积优化目标,该约束由用户指定,DC 在不违反设计规则约束的前提下,遵循此约束综合设计。

⑥选择编译策略:

对于层次化设计,DC 中有两种编译策略供选择,分别为 top down 和 bottom

up。在 top down 策略中,顶层设计和子设计在一起编译,所有的环境和约束设置针对顶层设计,虽然此种策略自动考虑到相关的内部设计,但是此种策略不适合与大型设计,因为 top down 编译策略中,所以设计必须同时驻内存,硬件资源耗费大。在 bottom up 策略中,子设计单独约束,当子设计成功编译后,被设置为 dont_touch 属性,防止在之后的编译过程中被修改,所有同层子设计编译完成后,再编译之上的父设计,直至顶层设计编译完成。Bottom up 策略允许大规模设计,因为该策略不需要所有设计同时驻入内存。

⑦编译:

用 Compile 命令执行综合与优化过程,还可以利用一些选项指导编译和优化过程。

⑧分析及解决设计中存在的问题

DC 可以产生一些报告以反应设计的综合和优化结果,如:时序、面积、约束等报告,这些报告有助于分析和解决设计中存在的问题以改善综合结果,我们还可以利用 check_design 命令检验综合的设计的一致性。

⑨存储设计数据

DC 不会自动存储综合后的设计结果,因而需要在离开 DC 时手动存储设计数据。比如存储网表、延时信息等数据文件。

2、实战

在这里,我们将实战一下,做一下实验,让大家体验一下流程:

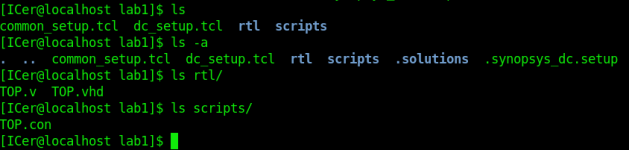

·首先准备好文件:

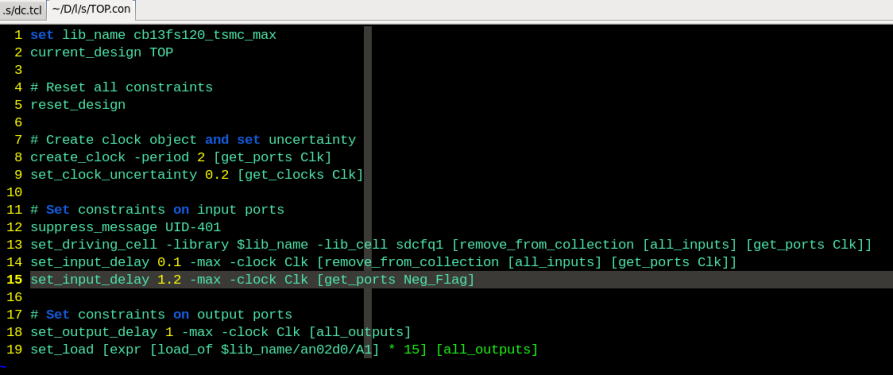

这个.synopsys_dc.setup文件(包含了com、dc_setup)、TOP.con文件是需要我们书写的,这里以及写好了,我们来看一下就好了。

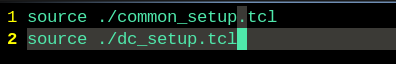

.synopsys_dc.setup的内容:

然后我们移步到common_setup.tcl和dc_setup.tcl的内容:

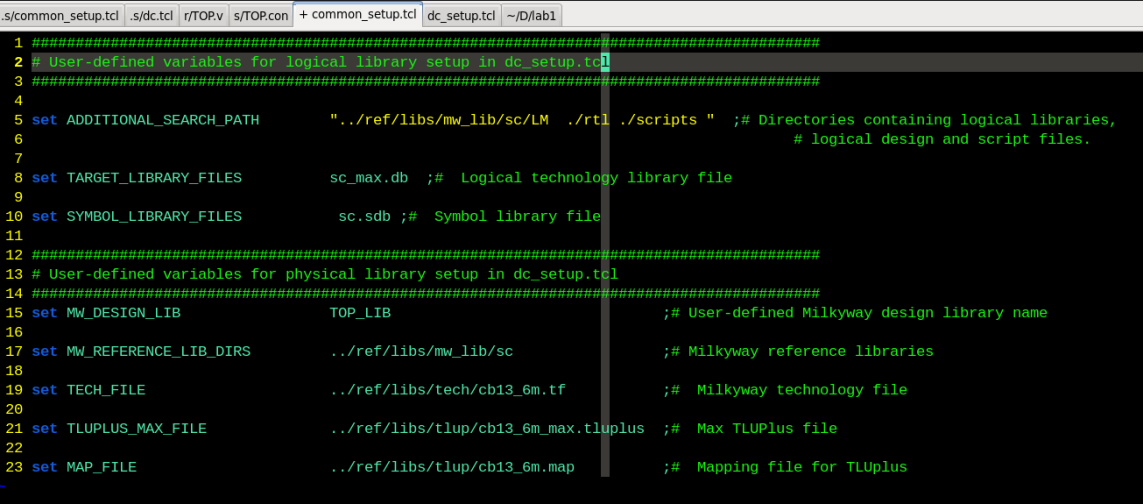

common_setup.tcl文件定义了库的名字和名称,上面是逻辑库,下面物理库:

5行:定义库的搜索路径,当找不到库时,从这个路径中寻找

8行:定义target library使用的库(注意,只是定义一个变量)

10行:定义图形库变量

15行:定义顶层设计库的变量名称

17行:定义milkyway(参考)库(的位置)

19行:定义工艺库(的位置)

21行:定义寄生参数库(的位置)

23行:定义工艺库和寄生参数库的映射关系库(的位置)

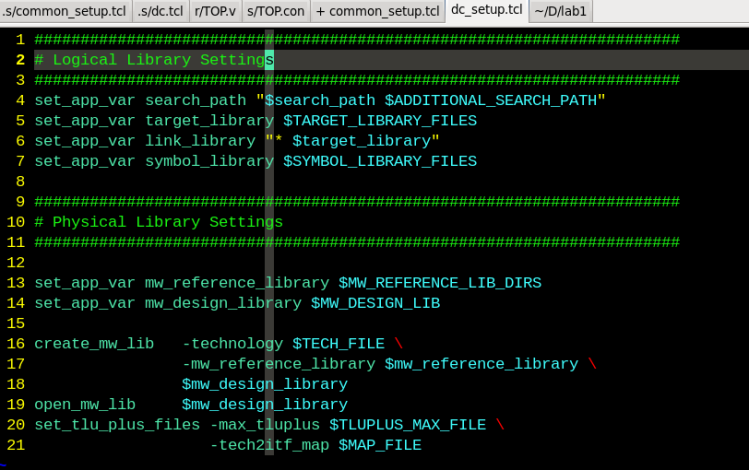

dc_setup.tcl的内容:

dc_setup.tcl文件就是指定库了,而不是单单地定义了,ser_app_var是定义DC内部变量,4~7这是指定搜索路径个各种库的路径和名称

下面的物理库设置中:

13行:指定milkyway(参考)库的名称

14行:指定当前设计的库的名称

16行:创建milkyway库,格式如图上面,需要工艺库、参考、当前设计库

19行:打开当前的设计库

20行:加载寄生参数(库)

·启动DC

这里是流程演示,因此我们使用图形化的方式启动:

design_vision -topo

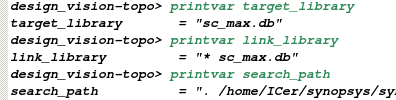

·读入设计前的检查

-->检查库是否正确设置:

-->检查逻辑库和物理课的一致性:

Check_library

检查可能不会通过,结果不影响综合的话,可以忽略

-->检查寄生参数文件和工艺库文件的一致性:(物理综合的时候需要检查)

check_tlu_plus_files

通过的话会有三个passed

·读入设计和查看设计

-->读入设计:

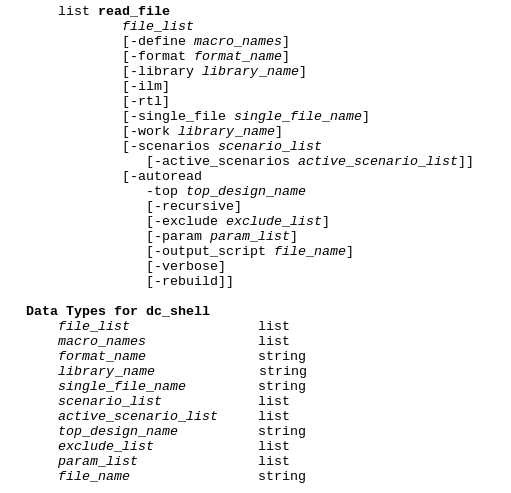

read_file -format verilog ./rtl/TOP.v

用法如下所示:

-->设置当前设计

要综合哪个模块,就把哪个模块设置为当前设计;

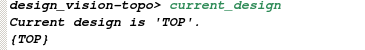

查看当前设计:current_design

设置当前设计:current_design TOP

-->link设计

Link设计,查看当前要综合的设计是否缺少子模块:

link

返回值是1,说明子模块完整

-->以ddc的格式保存未映射的设计(注意需要先创建unmapped文件夹):

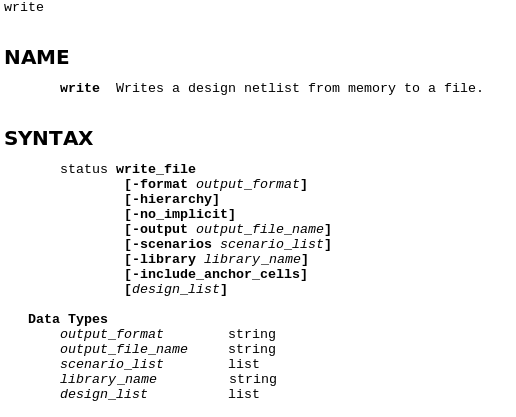

Write -hierarchy -f ddc -out unmapped/TOP.ddc

我们可以看看write的用法:

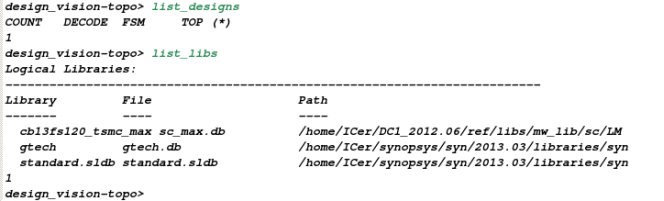

-->查看内存中的设计和库:

带*的设计为当前设计,要综合哪个模块就current_design哪个设计

然后list_libs是查看库和库的路径,这个命令也可以检查是否读入了对应的库

·约束设计(也就是上面流程图中的各种set)

我们通过执行约束文件来约束设计:

source TOP.con

其他选项我们在后面会叙述,我们这里只说一下5行的reset_design,这个就是剔除之前所有的约束,防止影响下面的约束。

·进行综合

Compile_ultra(这是在拓扑模式下进行综合的命令)

·综合后的检查(检查不通过的需要优化,这里只作为一般流程,没有进行优化)

report_constraint -all (查看是否违规)

report_timing (查看时序报告)

report_are (查看面积情况)

·保存综合后的设计(注意先创建mapped这个文件夹)

write -hierarchy -format ddc -output ./mapped/TOP.ddc

总结,大概的流程为:

准备好文件 ——>启动DC ——>读入设计前的检查——>读入设计和查看设计——>约束设计——>综合——>综合后检查(与优化)——>保存优化后的设计