教材知识点总结

存储技术

-

随机访问存储技术

-

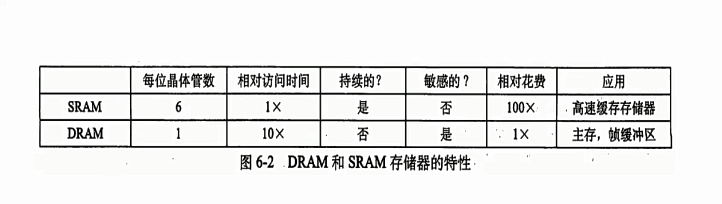

静态的(SRAM):SRAM将每个位存储在一个双稳态的存储器单元中

-

动态的(DRAM):DRAM将每个位存储为对一个电容的充电

-

特性比较:

-

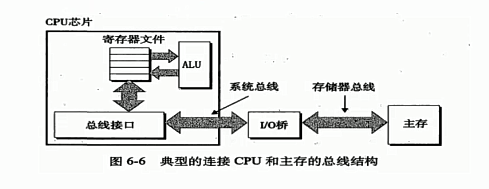

访问主存结构:

-

传统的DRAM:DRAM芯片中的单元被分成d个超单元,每个超单元都由W个DRAM单元组成,一个d*w的DRAM总共存储了dw位信息。超单元被组织成一个r行c列的长方形矩阵。

-

增强的DRAM

1、 快页模式DRAM

2、扩展输出数据DRAM

3、同步DRAM

4、双倍数据速率同步DRAM

5、 视频RAM

-

非易失性存储器

1、 电子可擦出PROM

2、可擦可编程ROM

3、闪存

-

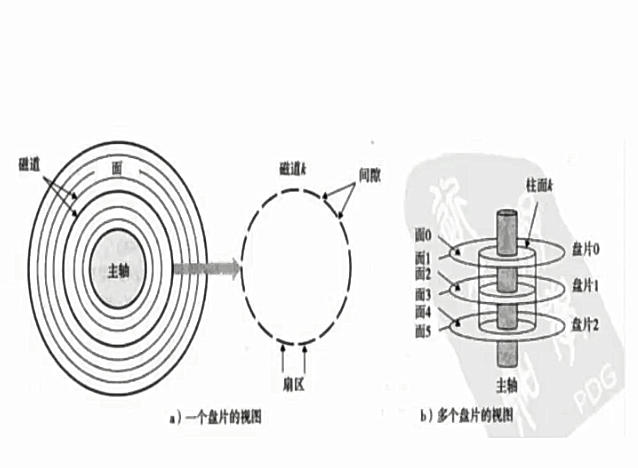

磁盘存储

- 磁盘

-

构造:旋转速率、数据位、间隙、柱面、磁道、扇区

-

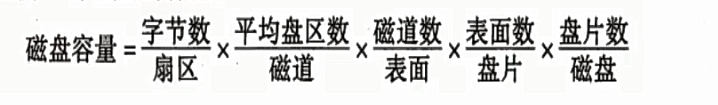

磁盘容量的决定因素:记录密度、磁道密度、面密度

-

公式:

- 固态硬盘的结构与特点

对程序数据引用的局部性

-

局部性原理:包括时间局部性与空间局部性

- 步长:随着步长的增加,空间局部性下降。

-

取指令的局部性

- 循环体具有良好的局部性。

-

评价原则:

- 重复引用同一个变量的程序-有良好的时间局部性。

- 对于具有步长为k的引用模式的程序,步长越小,空间局部性越好。

- 对于取指令来说,循环有好的时间和空间局部性。循环体越小,局部性越好

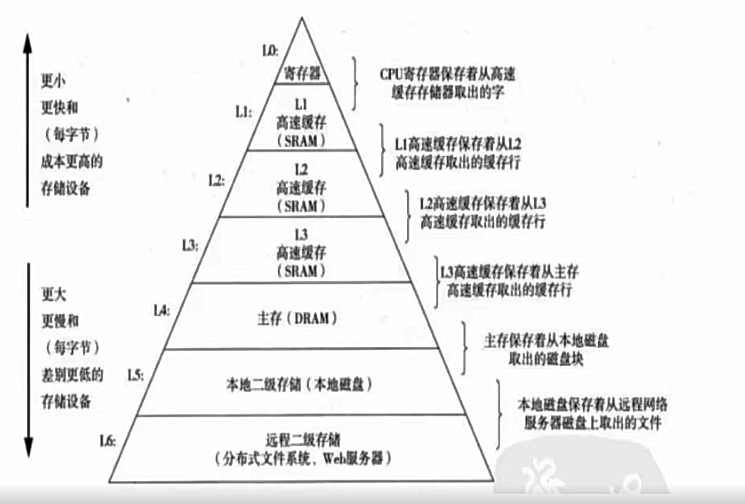

存储器层次结构

-

缓存:使用高速缓存的过程

-

存储器层次结构的中心思想:k层的更小更快的存储设备,作为k+1层的更大更慢的存储设备的缓存。

-

缓存命中与不命中

- 不命中分类:冷缓存、冲突不命中、容量不命中

高速缓存存储器

-

直接映射高速缓存

-

定义:每个组只有一行的高速缓存。

-

步骤:组选择 -> 行匹配 -> 字抽取

-

-

组相联高速缓存

-

定义:每个组都保存有多余一个的高速缓存行

-

步骤:组选择 -> 行匹配和字选择 -> 缓存中不命中时的行替换

-

-

全相联高速缓存

-

定义:每个组都包含所有高速缓存行

-

步骤:组选择 -> 行匹配和字选择

-

有关写的问题

-

直写:立即将w的高速缓存块写回到紧接着的低一层中。

- 优缺点:简单/每次写都会引起总线流量

-

写回:只有当替换算法要驱逐更新过的块时,才写到紧接着的低一层中。

- 优缺点:符合局部性原理,显著的减少总线流量/增加了复杂性,必须为每个高速缓存行维护一个额外的修改位

-

处理写不命中

-

写分配 -- 通常写回对应

-

非写分配 -- 通常直写对应

-

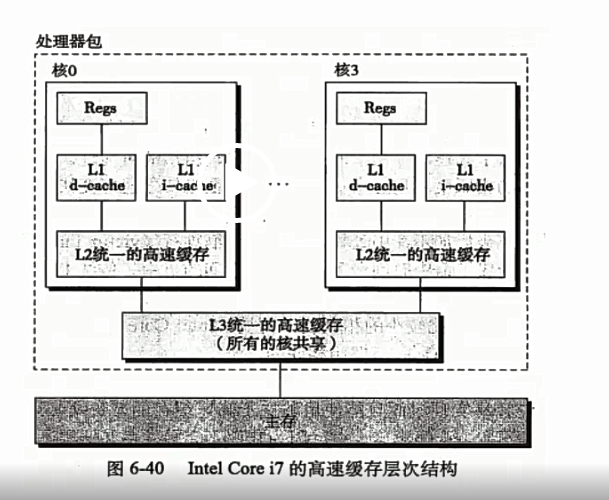

一个真实高速缓存层次结构的解剖

高速缓存参数的性能影响

-

高速缓存大小的影响:较大的高速缓存可能提高命中率,但也可能增加命中时间。

-

块大小的影响: 较大的块能利用程序间隙中的空间局部性,帮助提高命中率。

-

相联度的影响: 降低出现不命中出现抖动的可能性。

-

写策略的影响:用于更新存储器

编写高速缓存友好的代码

-

让程序把时间花在少量的核心函数上,这些函数通常把时间花在少量循环上。

-

尽量减小每个循环内部的缓存不命中数量。