1、新建一个文件夹,把所需仿真的.v文件放到这个文件夹中。

2、为了打开图形界面,需要在.v测试文件增多代码:

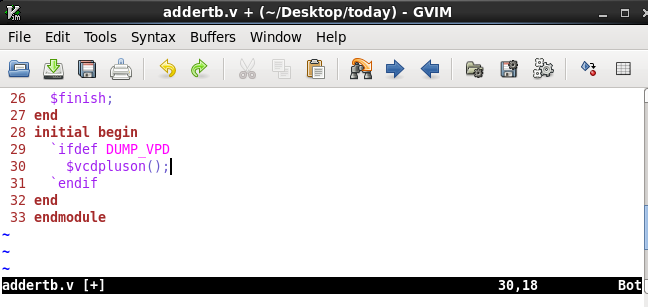

initial begin

`ifdef DUMP_VPD

$vcdpluson();

`endif

end

如图所示:

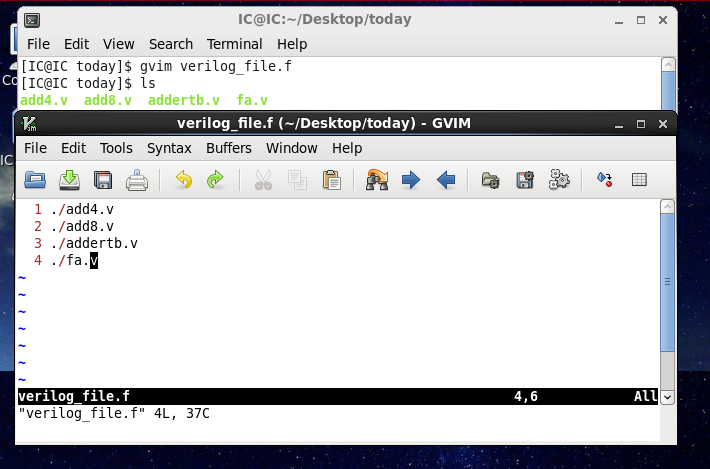

3、终端打开这个文件夹,然后命令gvim verilog_file.f。

4、把.v文件名输入,如图所示:

保存退出。(PS:按键g+f可以看.v文件的内容,按键Ctrl+o返回,如果可以这样操作,说明相对路径成功生成!)

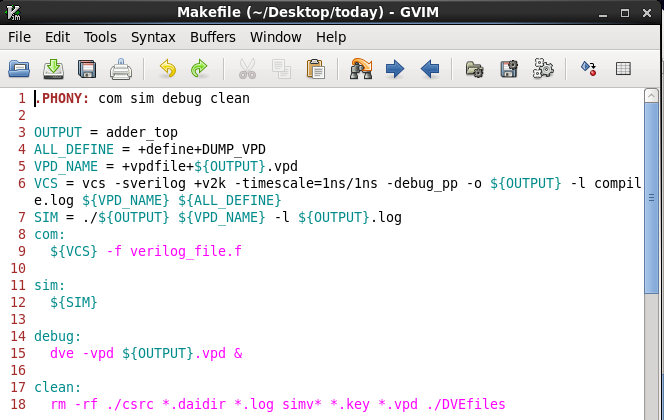

5、在verilog_file.f中输入命令tabnew Makefile,然后输入内容:

.PHONY: com sim debug clean

OUTPUT = adder_top

ALL_DEFINE = +define+DUMP_VPD

VPD_NAME = +vpdfile+${OUTPUT}.vpd

VCS = vcs -sverilog +v2k -timescale=1ns/1ns -debug_pp -o ${OUTPUT} -l compile.log ${VPD_NAME} ${ALL_DEFINE}

SIM = ./${OUTPUT} ${VPD_NAME} -l ${OUTPUT}.log

com:

${VCS} -f verilog_file.f

sim:

${SIM}

debug:

dve -vpd ${OUTPUT}.vpd &

clean:

rm -rf ./csrc *.daidir *.log simv* *.key *.vpd ./DVEfiles

如图所示:

6、输入命令就可以。

make com相当于(vcs -sverilog +v2k -timescale=1ns/1ns -debug_all -o adder_top -l compile.log -f verilog_file.f)。

make sim相当于(./adder_top -l run.log)。

make debug相当于(./simv -gui )。

make clean相当于(rm -rf ./csrc *.daidir *.log simv* *.key)。