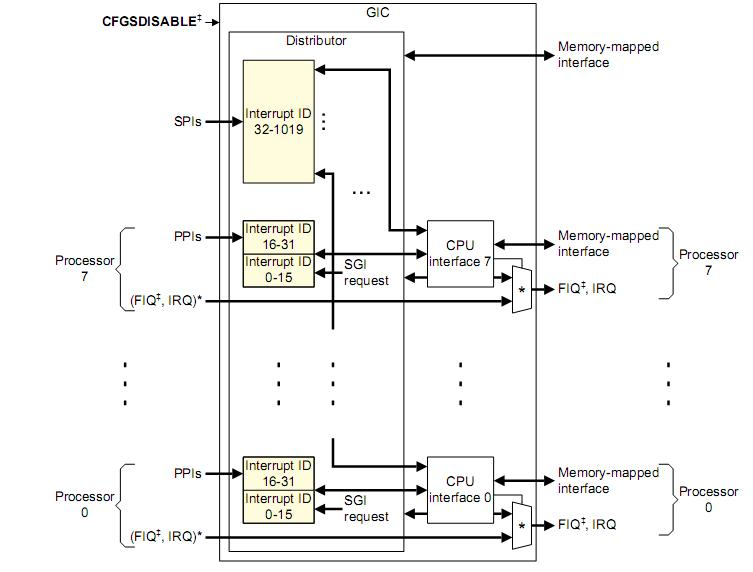

首先跟大家介绍下,Cyclone V SoC FPGA 的MPU子系统有包含一个通用中断控制器 ARM Generic Interrupt controler(GIC),GIC是负责收集所有的中断资源并上报到MPU进行处理。GIC 把中断分作了三类providing per processor interrupts (PPI),shared processor interrupts (SPI) 和software generated interrupts (SGI)。

HPS一共可以接受212个中断源(参见cyclone5_handbook.pdf 手册的 Table 9-3: GIC Interrupt Map 表格),其中0-31是系统软件中断和各个CPU的私有中断。32-211为包括FPGA在内的外设中断(这有 64个是来自 FPGA 架构中实现的专用外设和IP),GIC中称作是SPI,即可以共享的中断。

在双核系统中,GIC 由两个 Cortex- A9 处理器共享。您可以配置 HPS 组件以提供 64 个通用 FPGA- to- HPS 中断,从而使 FPGA 内核逻辑中软 IP 能够触发 MPU 的通用中断控制器 (GIC) 的中断。来自FPGA的中断的GIC编号从72开始(参见cyclone5_handbook.pdf 第843页)。

来自FPGA的中断通过以下 32 位接口实现:

- f2h_irq0—FPGA- to- HPS 中断 0 到 31

- f2h_irq1—FPGA- to- HPS 中断 32 到 63

比如上图dipsw组件的中断连接到HPS组件的f2h_irq0, 中断号设置为0, 实际对应到GIC中的中断号应该是72。另外图中还有一个f2h_irq1,这个对应着是从中断号104开始的(104-135共32个中断)。