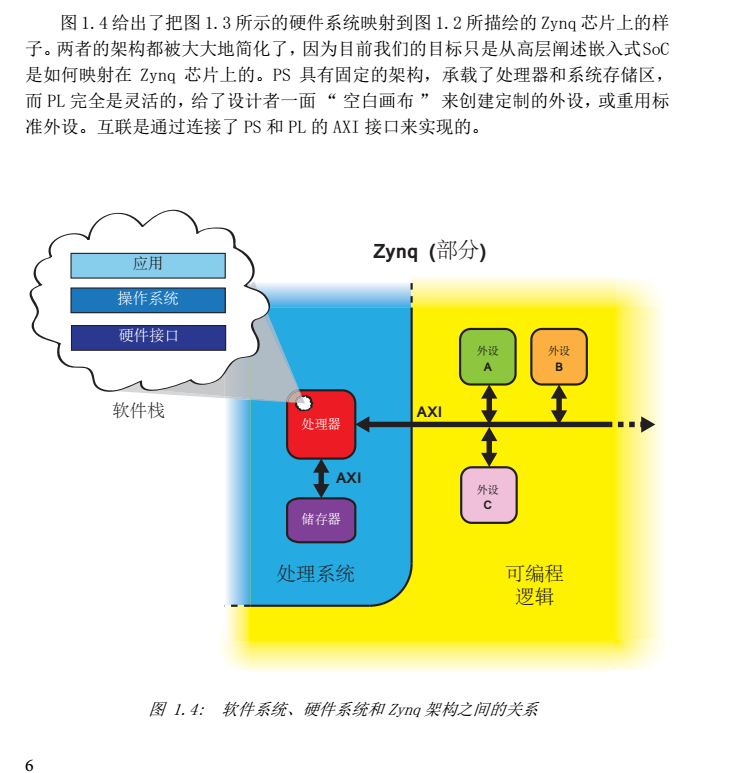

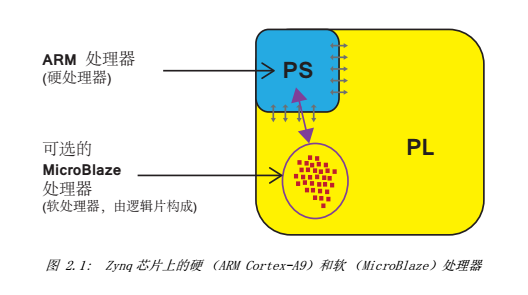

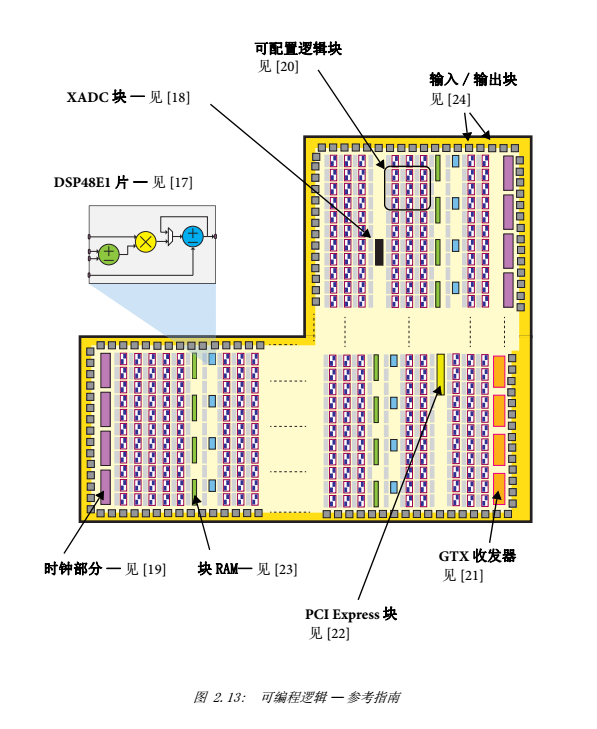

1.zynq开发板的构造以及推崇的设计理念

设计推崇的理念是设计有知识产权的可重用的IP模块。

设计推崇的理念是设计有知识产权的可重用的IP模块。

2.操作过程中遇到的问题以及解决方法

(1)综合速度慢解决方案:

我们都知道Vivado编译起来相当的慢,每次综合起来我就拿起了手机,这个方法可以提高编译速度,在VIVADO中一个run编译时支持的线程数如下表:(综合时一般是2线程)

|

|

Place |

Route |

|

Windows默认 |

2 |

2 |

|

Linux默认 |

4 |

4 |

|

Windows开启maxThreads=8 |

4 |

4 |

|

linux开启maxThreads=8 |

8 |

8 |

A:在tcl脚本处输入如下命令:

设置多线程的命令为: set_param general.maxThreads 4

读取当前线程数的命令: 为get_param general.maxThreads

B:增量编译设计:

1、首先完成非增量编译,获得参考的布局布线dcp文件;

2、当逻辑修改小于5%,需重新出版本,采用增量编译

3、按步骤打开:implementation setting——options——incremental compile,浏览文件

4、选择.runs / impl_1 / *.dcp

5、点击run implementation,等待结果

效果:预计能减少30%左右的时间。

(2)引脚指定约束xdc文件的编写语法要求等

参考网址

https://blog.csdn.net/angelbosj/article/details/52921563

http://xilinx.eetrend.com/article/8441

https://blog.csdn.net/feiliantong/article/details/78011665

(3)dcp文件的用途:http://blog.chinaaet.com/luozhongpin1989/p/37153

3.操作的流程

http://www.docin.com/p-1856047260.html

以一个工程为例,按照如下步骤开发关于block design

#1.create block design,产生一个空白的工程模板

#2.导入IP核,包括一些经常用到的核,如zynq-processing-system,axi-dma,conact,axi-fifo-data,以及我们需要的所有的自己编写的HLS的IP核

#3.选择auto-connect对模块进行连接,但是这个过程并不会把所有的模块都接好,所以还需要进一步的手动连接(需要注意的是对于axi相关的连线,能一根直接连接完毕就不要用多根自己连接,会导致编译错误)

#4.进行validate design————generate block design(相当于产生一个完整的工程)————create wrapper(将工程包装起来,右击source的system选择create HDL wrapper即可)

#5.执行综合和implementation(该过程费时间较长,可以先略过去)然后generate bitstream

#6.file--export hardware 然后launch SDK,打开SDK进行软件部分的设置

#7.软件部分的实现过程直接导入main.c等相关的文件,file ---refresh后,保存就会自动编译

#8.编译成功后,右击system_wrapper_hw_platform_0,在弹出来的对话框中选择run as ---run configurations,然后选择对应的bitstream文件,接下来就可以将文件下载到开发板,进行工程的执行。

转】用Vivado/SDK实现microblaze的一些总结