原文地址:http://lwn.net/Articles/250967/

1 简介

早期计算机比现在更为简单。系统的各种组件例如CPU,内存,大容量存储器和网口,由于被共同开发因而有非常均衡的表现。例如,内存和网口并不比CPU在提供数据的时候更(特别的)快。

曾今计算机稳定的基本结构悄然改变,硬件开发人员开始致力于优化单个子系统。于是电脑一些组件的性能大大的落后因而成为了瓶颈。由于开销的原因,大容量存储器和内存子系统相对于其他组件来说改善得更为缓慢。

大容量存储的性能问题往往靠软件来改善: 操作系统将常用(且最有可能被用)的数据放在主存中,因为后者的速度要快上几个数量级。或者将缓存加入存储设备中,这样就可以在不修改操作系统的前提下提升性能。{然而,为了在使用缓存时保证数据的完整性,仍然要作出一些修改。}这些内容不在本文的谈论范围之内,就不作赘述了。

而解决内存的瓶颈更为困难,它与大容量存储不同,几乎每种方案都需要对硬件作出修改。目前,这些变更主要有以下这些方式:

- RAM的硬件设计(速度与并发度)

- 内存控制器的设计

- CPU缓存

- 设备的直接内存访问(DMA)

本文主要关心的是CPU缓存和内存控制器的设计。在讨论这些主题的过程中,我们还会研究DMA。不过,我们首先会从当今商用硬件的设计谈起。这有助于我们理解目前在使用内存子系统时可能遇到的问题和限制。我们还会详细介绍RAM的分类,说明为什么会存在这么多不同类型的内存。

本文不会包括所有内容,也不会包括最终性质的内容。我们的讨论范围仅止于商用硬件,而且只限于其中的一小部分。另外,本文中的许多论题,我们只会点到为止,以达到本文目标为标准。对于这些论题,大家可以阅读其它文档,获得更详细的说明。

当本文提到操作系统特定的细节和解决方案时,针对的都是Linux。无论何时都不会包含别的操作系统的任何信息,作者无意讨论其他操作系统的情况。如果读者认为他/她不得不使用别的操作系统,那么必须去要求供应商提供其操作系统类似于本文的文档。

在开始之前最后的一点说明,本文包含大量出现的术语“经常”和别的类似的限定词。这里讨论的技术在现实中存在于很多不同的实现,所以本文只阐述使用得最广泛最主流的版本。在阐述中很少有地方能用到绝对的限定词。

1.1文档结构

这个文档主要视为软件开发者而写的。本文不会涉及太多硬件细节,所以喜欢硬件的读者也许不会觉得有用。但是在我们讨论一些有用的细节之前,我们先要描述足够多的背景。

在这个基础上,本文的第二部分将描述RAM(随机寄存器)。懂得这个部分的内容很好,但是此部分的内容并不是懂得其后内容必须部分。我们会在之后引用不少之前的部分,所以心急的读者可以跳过任何章节来读他们认为有用的部分。

第三部分会谈到不少关于CPU缓存行为模式的内容。我们会列出一些图标,这样你们不至于觉得太枯燥。第三部分对于理解整个文章非常重要。第四部分将简短的描述虚拟内存是怎么被实现的。这也是你们需要理解全文其他部分的背景知识之一。

第五部分会提到许多关于Non Uniform Memory Access (NUMA)系统。

第六部分是本文的中心部分。在这个部分里面,我们将回顾其他许多部分中的信息,并且我们将给阅读本文的程序员许多在各种情况下的编程建议。如果你真的很心急,那么你可以直接阅读第六部分,并且我们建议你在必要的时候回到之前的章节回顾一下必要的背景知识。

本文的第七部分将介绍一些能够帮助程序员更好的完成任务的工具。即便在彻底理解了某一项技术的情况下,距离彻底理解在非测试环境下的程序还是很遥远的。我们需要借助一些工具。

第八部分,我们将展望一些在未来我们可能认为好用的科技。

1.2 反馈问题

作者会不定期更新本文档。这些更新既包括伴随技术进步而来的更新也包含更改错误。非常欢迎有志于反馈问题的读者发送电子邮件。

1.3 致谢

我首先需要感谢Johnray Fuller尤其是Jonathan Corbet,感谢他们将作者的英语转化成为更为规范的形式。Markus Armbruster提供大量本文中对于问题和缩写有价值的建议。

1.4 关于本文

本文题目对David Goldberg的经典文献《What Every Computer Scientist Should Know About Floating-Point Arithmetic》[goldberg]表示致敬。Goldberg的论文虽然不普及,但是对于任何有志于严格编程的人都会是一个先决条件。

2 商用硬件现状

鉴于目前专业硬件正在逐渐淡出,理解商用硬件的现状变得十分重要。现如今,人们更多的采用水平扩展,也就是说,用大量小型、互联的商用计算机代替巨大、超快(但超贵)的系统。原因在于,快速而廉价的网络硬件已经崛起。那些大型的专用系统仍然有一席之地,但已被商用硬件后来居上。2007年,Red Hat认为,未来构成数据中心的“积木”将会是拥有最多4个插槽的计算机,每个插槽插入一个四核CPU,这些CPU都是超线程的。{超线程使单个处理器核心能同时处理两个以上的任务,只需加入一点点额外硬件}。也就是说,这些数据中心中的标准系统拥有最多64个虚拟处理器。当然可以支持更大的系统,但人们认为4插槽、4核CPU是最佳配置,绝大多数的优化都针对这样的配置。

在不同商用计算机之间,也存在着巨大的差异。不过,我们关注在主要的差异上,可以涵盖到超过90%以上的硬件。需要注意的是,这些技术上的细节往往日新月异,变化极快,因此大家在阅读的时候也需要注意本文的写作时间。

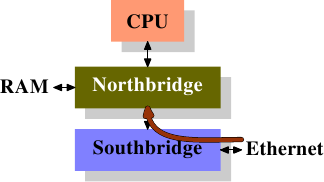

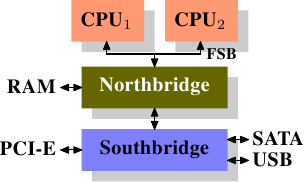

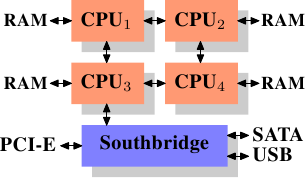

这么多年来,个人计算机和小型服务器被标准化到了一个芯片组上,它由两部分组成: 北桥和南桥,见图2.1。

图2.1 北桥和南桥组成的结构

CPU通过一条通用总线(前端总线,FSB)连接到北桥。北桥主要包括内存控制器和其它一些组件,内存控制器决定了RAM芯片的类型。不同的类型,包括DRAM、Rambus和SDRAM等等,要求不同的内存控制器。

为了连通其它系统设备,北桥需要与南桥通信。南桥又叫I/O桥,通过多条不同总线与设备们通信。目前,比较重要的总线有PCI、PCI Express、SATA和USB总线,除此以外,南桥还支持PATA、IEEE 1394、串行口和并行口等。比较老的系统上有连接北桥的AGP槽。那是由于南北桥间缺乏高速连接而采取的措施。现在的PCI-E都是直接连到南桥的。

这种结构有一些需要注意的地方:

- 从某个CPU到另一个CPU的数据需要走它与北桥通信的同一条总线。

- 与RAM的通信需要经过北桥

- RAM只有一个端口。{本文不会介绍多端口RAM,因为商用硬件不采用这种内存,至少程序员无法访问到。这种内存一般在路由器等专用硬件中采用。}

- CPU与南桥设备间的通信需要经过北桥

在上面这种设计中,瓶颈马上出现了。第一个瓶颈与设备对RAM的访问有关。早期,所有设备之间的通信都需要经过CPU,结果严重影响了整个系统的性能。为了解决这个问题,有些设备加入了直接内存访问(DMA)的能力。DMA允许设备在北桥的帮助下,无需CPU的干涉,直接读写RAM。到了今天,所有高性能的设备都可以使用DMA。虽然DMA大大降低了CPU的负担,却占用了北桥的带宽,与CPU形成了争用。

第二个瓶颈来自北桥与RAM间的总线。总线的具体情况与内存的类型有关。在早期的系统上,只有一条总线,因此不能实现并行访问。近期的RAM需要两条独立总线(或者说通道,DDR2就是这么叫的,见图2.8),可以实现带宽加倍。北桥将内存访问交错地分配到两个通道上。更新的内存技术(如FB-DRAM)甚至加入了更多的通道。

由于带宽有限,我们需要以一种使延迟最小化的方式来对内存访问进行调度。我们将会看到,处理器的速度比内存要快得多,需要等待内存。如果有多个超线程核心或CPU同时访问内存,等待时间则会更长。对于DMA也是同样。

除了并发以外,访问模式也会极大地影响内存子系统、特别是多通道内存子系统的性能。关于访问模式,可参见2.2节。

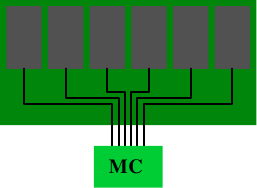

在一些比较昂贵的系统上,北桥自己不含内存控制器,而是连接到外部的多个内存控制器上(在下例中,共有4个)。

图2.2 拥有外部控制器的北桥

这种架构的好处在于,多条内存总线的存在,使得总带宽也随之增加了。而且也可以支持更多的内存。通过同时访问不同内存区,还可以降低延时。对于像图2.2中这种多处理器直连北桥的设计来说,尤其有效。而这种架构的局限在于北桥的内部带宽,非常巨大(来自Intel)。{出于完整性的考虑,还需要补充一下,这样的内存控制器布局还可以用于其它用途,比如说「内存RAID」,它可以与热插拔技术一起使用。}

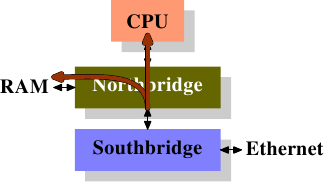

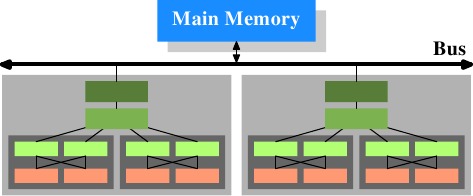

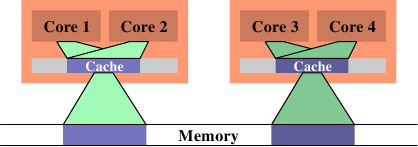

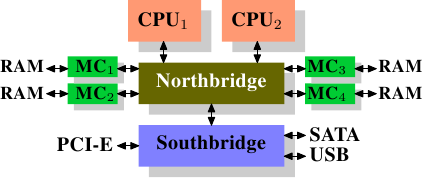

使用外部内存控制器并不是唯一的办法,另一个最近比较流行的方法是将控制器集成到CPU内部,将内存直连到每个CPU。这种架构的走红归功于基于AMD Opteron处理器的SMP系统。图2.3展示了这种架构。Intel则会从Nehalem处理器开始支持通用系统接口(CSI),基本上也是类似的思路——集成内存控制器,为每个处理器提供本地内存。

图2.3 集成的内存控制器

通过采用这样的架构,系统里有几个处理器,就可以有几个内存库(memory bank)。比如,在4 CPU的计算机上,不需要一个拥有巨大带宽的复杂北桥,就可以实现4倍的内存带宽。另外,将内存控制器集成到CPU内部还有其它一些优点,这里就不赘述了。

同样也有缺点。首先,系统仍然要让所有内存能被所有处理器所访问,导致内存不再是统一的资源(NUMA即得名于此)。处理器能以正常的速度访问本地内存(连接到该处理器的内存)。但它访问其它处理器的内存时,却需要使用处理器之间的互联通道。比如说,CPU 1如果要访问CPU 2的内存,则需要使用它们之间的互联通道。如果它需要访问CPU 4的内存,那么需要跨越两条互联通道。

使用互联通道是有代价的。在讨论访问远端内存的代价时,我们用「NUMA因子」这个词。在图2.3中,每个CPU有两个层级: 相邻的CPU,以及两个互联通道外的CPU。在更加复杂的系统中,层级也更多。甚至有些机器有不止一种连接,比如说IBM的x445和SGI的Altix系列。CPU被归入节点,节点内的内存访问时间是一致的,或者只有很小的NUMA因子。而在节点之间的连接代价很大,而且有巨大的NUMA因子。

目前,已经有商用的NUMA计算机,而且它们在未来应该会扮演更加重要的角色。人们预计,从2008年底开始,每台SMP机器都会使用NUMA。每个在NUMA上运行的程序都应该认识到NUMA的代价。在第5节中,我们将讨论更多的架构,以及Linux内核为这些程序提供的一些技术。

除了本节中所介绍的技术之外,还有其它一些影响RAM性能的因素。它们无法被软件所左右,所以没有放在这里。如果大家有兴趣,可以在第2.1节中看一下。介绍这些技术,仅仅是因为它们能让我们绘制的RAM技术全图更为完整,或者是可能在大家购买计算机时能够提供一些帮助。

以下的两节主要介绍一些入门级的硬件知识,同时讨论内存控制器与DRAM芯片间的访问协议。这些知识解释了内存访问的原理,程序员可能会得到一些启发。不过,这部分并不是必读的,心急的读者可以直接跳到第2.2.5节。

2.1 RAM类型

这些年来,出现了许多不同类型的RAM,各有差异,有些甚至有非常巨大的不同。那些很古老的类型已经乏人问津,我们就不仔细研究了。我们主要专注于几类现代RAM,剖开它们的表面,研究一下内核和应用开发人员们可以看到的一些细节。

第一个有趣的细节是,为什么在同一台机器中有不同的RAM?或者说得更详细一点,为什么既有静态RAM(SRAM {SRAM还可以表示「同步内存」。}),又有动态RAM(DRAM)。功能相同,前者更快。那么,为什么不全部使用SRAM?答案是,代价。无论在生产还是在使用上,SRAM都比DRAM要贵得多。生产和使用,这两个代价因子都很重要,后者则是越来越重要。为了理解这一点,我们分别看一下SRAM和DRAM一个位的存储的实现过程。

在本节的余下部分,我们将讨论RAM实现的底层细节。我们将尽量控制细节的层面,比如,在「逻辑的层面」讨论信号,而不是硬件设计师那种层面,因为那毫无必要。

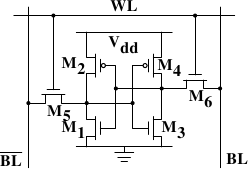

2.1.1 静态RAM

图2.6 6-T静态RAM

图2.4展示了6晶体管SRAM的一个单元。核心是4个晶体管M1-M4,它们组成两个交叉耦合的反相器。它们有两个稳定的状态,分别代表0和1。只要保持Vdd有电,状态就是稳定的。

当需要访问单元的状态时,升起字访问线WL。BL和BL上就可以读取状态。如果需要覆盖状态,先将BL和BL设置为期望的值,然后升起WL。由于外部的驱动强于内部的4个晶体管,所以旧状态会被覆盖。

更多详情,可以参考[sramwiki]。为了下文的讨论,需要注意以下问题:

一个单元需要6个晶体管。也有采用4个晶体管的SRAM,但有缺陷。

维持状态需要恒定的电源。

升起WL后立即可以读取状态。信号与其它晶体管控制的信号一样,是直角的(快速在两个状态间变化)。

状态稳定,不需要刷新循环。

SRAM也有其它形式,不那么费电,但比较慢。由于我们需要的是快速RAM,因此不在关注范围内。这些较慢的SRAM的主要优点在于接口简单,比动态RAM更容易使用。

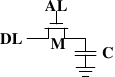

2.1.2 动态RAM

动态RAM比静态RAM要简单得多。图2.5展示了一种普通DRAM的结构。它只含有一个晶体管和一个电容器。显然,这种复杂性上的巨大差异意味着功能上的迥异。

图2.5 1-T动态RAM

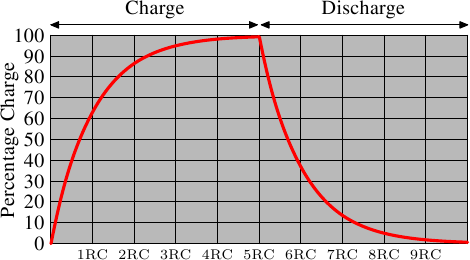

动态RAM的状态是保持在电容器C中。晶体管M用来控制访问。如果要读取状态,升起访问线AL,这时,可能会有电流流到数据线DL上,也可能没有,取决于电容器是否有电。如果要写入状态,先设置DL,然后升起AL一段时间,直到电容器充电或放电完毕。

动态RAM的设计有几个复杂的地方。由于读取状态时需要对电容器放电,所以这一过程不能无限重复,不得不在某个点上对它重新充电。

更糟糕的是,为了容纳大量单元(现在一般在单个芯片上容纳10的9次方以上的RAM单元),电容器的容量必须很小(0.000000000000001法拉以下)。这样,完整充电后大约持有几万个电子。即使电容器的电阻很大(若干兆欧姆),仍然只需很短的时间就会耗光电荷,称为「泄漏」。

这种泄露就是现在的大部分DRAM芯片每隔64ms就必须进行一次刷新的原因。在刷新期间,对于该芯片的访问是不可能的,这甚至会造成半数任务的延宕。(相关内容请察看【highperfdram】一章)

这个问题的另一个后果就是无法直接读取芯片单元中的信息,而必须通过信号放大器将0和1两种信号间的电势差增大。

最后一个问题在于电容器的冲放电是需要时间的,这就导致了信号放大器读取的信号并不是典型的矩形信号。所以当放大器输出信号的时候就需要一个小小的延宕,相关公式如下

这就意味着需要一些时间(时间长短取决于电容C和电阻R)来对电容进行冲放电。另一个负面作用是,信号放大器的输出电流不能立即就作为信号载体使用。图2.6显示了冲放电的曲线,x轴表示的是单位时间下的R*C

与静态RAM可以即刻读取数据不同的是,当要读取动态RAM的时候,必须花一点时间来等待电容的冲放电完全。这一点点的时间最终限制了DRAM的速度。

当然了,这种读取方式也是有好处的。最大的好处在于缩小了规模。一个动态RAM的尺寸是小于静态RAM的。这种规模的减小不单单建立在动态RAM的简单结构之上,也是由于减少了静态RAM的各个单元独立的供电部分。以上也同时导致了动态RAM模具的简单化。

综上所述,由于不可思议的成本差异,除了一些特殊的硬件(包括路由器什么的)之外,我们的硬件大多是使用DRAM的。这一点深深的影响了咱们这些程序员,后文将会对此进行讨论。在此之前,我们还是先了解下DRAM的更多细节。

2.1.3 DRAM 访问

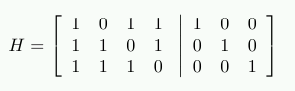

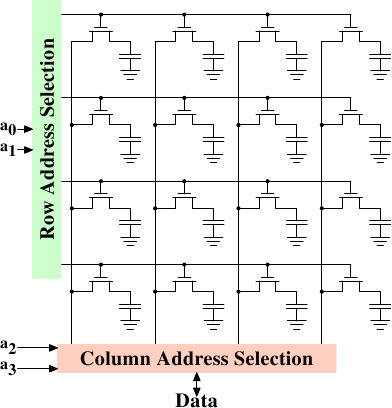

一个程序选择了一个内存位置使用到了一个虚拟地址。处理器转换这个到物理地址最后将内存控制选择RAM芯片匹配了那个地址。在RAM芯片去选择单个内存单元,部分的物理地址以许多地址行的形式被传递。

它单独地去处理来自于内存控制器的内存位置将完全不切实际:4G的RAM将需要 232 地址行。地址传递DRAM芯片的这种方式首先必须被路由器解析。一个路由器的N多地址行将有2N 输出行。这些输出行能被使用到选择内存单元。使用这个直接方法对于小容量芯片不再是个大问题

但如果许多的单元生成这种方法不在适合。一个1G的芯片容量(我反感那些SI前缀,对于我一个giga-bit将总是230 而不是109字节)将需要30地址行和230 选项行。一个路由器的大小及许多的输入行以指数方式递增当速度不被牺牲时。一个30地址行路由器需要一大堆芯片的真实身份另外路由器也就复杂起来了。更重要的是,传递30脉冲在地址行同步要比仅仅传递15脉冲困难的多。较少列能精确布局相同长度或恰当的时机(现代DRAM类型像DDR3能自动调整时序但这个限制能让他什么都能忍受)

图2.7展示了一个很高级别的一个DRAM芯片,DRAM被组织在行和列里。他们能在一行中对奇但DRAM芯片需要一个大的路由器。通过阵列方法设计能被一个路由器和一个半的multiplexer获得{多路复用器(multiplexer)和路由器是一样的,这的multiplexer需要以路由器身份工作当写数据时候。那么从现在开始我们开始讨论其区别.}这在所有方面会是一个大的存储。例如地址linesa0和a1通过行地址选择路由器来选择整个行的芯片的地址列,当读的时候,所有的芯片目录能使其纵列选择路由器可用,依据地址linesa2和a3一个纵列的目录用于数据DRAM芯片的接口类型。这发生了许多次在许多DRAM芯片产生一个总记录数的字节匹配给一个宽范围的数据总线。

对于写操作,内存单元的数据新值被放到了数据总线,当使用RAS和CAS方式选中内存单元时,数据是存放在内存单元内的。这是一个相当直观的设计,在现实中——很显然——会复杂得多,对于读,需要规范从发出信号到数据在数据总线上变得可读的时延。电容不会像前面章节里面描述的那样立刻自动放电,从内存单元发出的信号是如此这微弱以至于它需要被放大。对于写,必须规范从数据RAS和CAS操作完成后到数据成功的被写入内存单元的时延(当然,电容不会立刻自动充电和放电)。这些时间常量对于DRAM芯片的性能是至关重要的,我们将在下章讨论它。

另一个关于伸缩性的问题是,用30根地址线连接到每一个RAM芯片是行不通的。芯片的针脚是非常珍贵的资源,以至数据必须能并行传输就并行传输(比如:64位为一组)。内存控制器必须有能力解析每一个RAM模块(RAM芯片集合)。如果因为性能的原因要求并发行访问多个RAM模块并且每个RAM模块需要自己独占的30或多个地址线,那么对于8个RAM模块,仅仅是解析地址,内存控制器就需要240+之多的针脚。

在很长一段时间里,地址线被复用以解决DRAM芯片的这些次要的可扩展性问题。这意味着地址被转换成两部分。第一部分由地址位a0和a1选择行(如图2.7)。这个选择保持有效直到撤销。然后是第二部分,地址位a2和a3选择列。关键差别在于:只需要两根外部地址线。需要一些很少的线指明RAS和CAS信号有效,但是把地址线的数目减半所付出的代价更小。可是地址复用也带来自身的一些问题。我们将在2.2章中提到。

2.1.4 总结

如果这章节的内容有些难以应付,不用担心。纵观这章节的重点,有:

- 为什么不是所有的存储器都是SRAM的原因

- 存储单元需要单独选择来使用

- 地址线数目直接负责存储控制器,主板,DRAM模块和DRAM芯片的成本

- 在读或写操作结果之前需要占用一段时间是可行的

接下来的章节会涉及更多的有关访问DRAM存储器的实际操作的细节。我们不会提到更多有关访问SRAM的具体内容,它通常是直接寻址。这里是由于速度和有限的SRAM存储器的尺寸。SRAM现在应用在CPU的高速缓存和芯片,它们的连接件很小而且完全能在CPU设计师的掌控之下。我们以后会讨论到CPU高速缓存这个主题,但我们所需要知道的是SRAM存储单元是有确定的最大速度,这取决于花在SRAM上的艰难的尝试。这速度与CPU核心相比略慢一到两个数量级。

2.2 DRAM访问细节

在上文介绍DRAM的时候,我们已经看到DRAM芯片为了节约资源,对地址进行了复用。而且,访问DRAM单元是需要一些时间的,因为电容器的放电并不是瞬时的。此外,我们还看到,DRAM需要不停地刷新。在这一节里,我们将把这些因素拼合起来,看看它们是如何决定DRAM的访问过程。

我们将主要关注在当前的科技上,不会再去讨论异步DRAM以及它的各种变体。如果对它感兴趣,可以去参考[highperfdram]及[arstechtwo]。我们也不会讨论Rambus DRAM(RDRAM),虽然它并不过时,但在系统内存领域应用不广。我们将主要介绍同步DRAM(SDRAM)及其后继者双倍速DRAM(DDR)。

同步DRAM,顾名思义,是参照一个时间源工作的。由内存控制器提供一个时钟,时钟的频率决定了前端总线(FSB)的速度。FSB是内存控制器提供给DRAM芯片的接口。在我写作本文的时候,FSB已经达到800MHz、1066MHz,甚至1333MHz,并且下一代的1600MHz也已经宣布。但这并不表示时钟频率有这么高。实际上,目前的总线都是双倍或四倍传输的,每个周期传输2次或4次数据。报的越高,卖的越好,所以这些厂商们喜欢把四倍传输的200MHz总线宣传为“有效的”800MHz总线。

以今天的SDRAM为例,每次数据传输包含64位,即8字节。所以FSB的传输速率应该是有效总线频率乘于8字节(对于4倍传输200MHz总线而言,传输速率为6.4GB/s)。听起来很高,但要知道这只是峰值速率,实际上无法达到的最高速率。我们将会看到,与RAM模块交流的协议有大量时间是处于非工作状态,不进行数据传输。我们必须对这些非工作时间有所了解,并尽量缩短它们,才能获得最佳的性能。

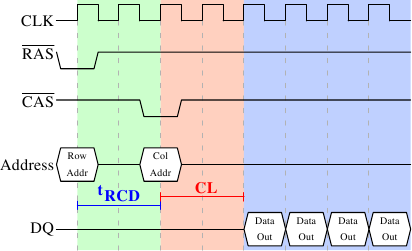

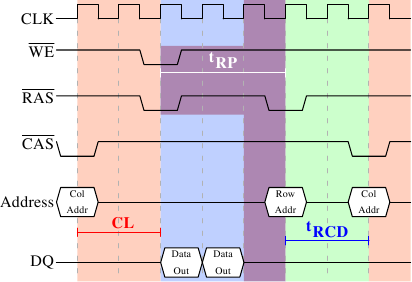

2.2.1 读访问协议

图2.8: SDRAM读访问的时序

图2.8展示了某个DRAM模块一些连接器上的活动,可分为三个阶段,图上以不同颜色表示。按惯例,时间为从左向右流逝。这里忽略了许多细节,我们只关注时钟频率、RAS与CAS信号、地址总线和数据总线。首先,内存控制器将行地址放在地址总线上,并降低RAS信号,读周期开始。所有信号都在时钟(CLK)的上升沿读取,因此,只要信号在读取的时间点上保持稳定,就算不是标准的方波也没有关系。设置行地址会促使RAM芯片锁住指定的行。

CAS信号在tRCD(RAS到CAS时延)个时钟周期后发出。内存控制器将列地址放在地址总线上,降低CAS线。这里我们可以看到,地址的两个组成部分是怎么通过同一条总线传输的。

至此,寻址结束,是时候传输数据了。但RAM芯片任然需要一些准备时间,这个时间称为CAS时延(CL)。在图2.8中CL为2。这个值可大可小,它取决于内存控制器、主板和DRAM模块的质量。CL还可能是半周期。假设CL为2.5,那么数据将在蓝色区域内的第一个下降沿准备就绪。

既然数据的传输需要这么多的准备工作,仅仅传输一个字显然是太浪费了。因此,DRAM模块允许内存控制指定本次传输多少数据。可以是2、4或8个字。这样,就可以一次填满高速缓存的整条线,而不需要额外的RAS/CAS序列。另外,内存控制器还可以在不重置行选择的前提下发送新的CAS信号。这样,读取或写入连续的地址就可以变得非常快,因为不需要发送RAS信号,也不需要把行置为非激活状态(见下文)。是否要将行保持为“打开”状态是内存控制器判断的事情。让它一直保持打开的话,对真正的应用会有不好的影响(参见[highperfdram])。CAS信号的发送仅与RAM模块的命令速率(Command Rate)有关(常常记为Tx,其中x为1或2,高性能的DRAM模块一般为1,表示在每个周期都可以接收新命令)。

在上图中,SDRAM的每个周期输出一个字的数据。这是第一代的SDRAM。而DDR可以在一个周期中输出两个字。这种做法可以减少传输时间,但无法降低时延。DDR2尽管看上去不同,但在本质上也是相同的做法。对于DDR2,不需要再深入介绍了,我们只需要知道DDR2更快、更便宜、更可靠、更节能(参见[ddrtwo])就足够了。

2.2.2 预充电与激活

图2.8并不完整,它只画出了访问DRAM的完整循环的一部分。在发送RAS信号之前,必须先把当前锁住的行置为非激活状态,并对新行进行预充电。在这里,我们主要讨论由于显式发送指令而触发以上行为的情况。协议本身作了一些改进,在某些情况下是可以省略这个步骤的,但预充电带来的时延还是会影响整个操作。

图2.9: SDRAM的预充电与激活

图2.9显示的是两次CAS信号的时序图。第一次的数据在CL周期后准备就绪。图中的例子里,是在SDRAM上,用两个周期传输了两个字的数据。如果换成DDR的话,则可以传输4个字。

即使是在一个命令速率为1的DRAM模块上,也无法立即发出预充电命令,而要等数据传输完成。在上图中,即为两个周期。刚好与CL相同,但只是巧合而已。预充电信号并没有专用线,某些实现是用同时降低写使能(WE)线和RAS线的方式来触发。这一组合方式本身没有特殊的意义(参见[micronddr])。

发出预充电信命令后,还需等待tRP(行预充电时间)个周期之后才能使行被选中。在图2.9中,这个时间(紫色部分)大部分与内存传输的时间(淡蓝色部分)重合。不错。但tRP大于传输时间,因此下一个RAS信号只能等待一个周期。

如果我们补充完整上图中的时间线,最后会发现下一次数据传输发生在前一次的5个周期之后。这意味着,数据总线的7个周期中只有2个周期才是真正在用的。再用它乘于FSB速度,结果就是,800MHz总线的理论速率6.4GB/s降到了1.8GB/s。真是太糟了。第6节将介绍一些技术,可以帮助我们提高总线有效速率。程序员们也需要尽自己的努力。

SDRAM还有一些定时值,我们并没有谈到。在图2.9中,预充电命令仅受制于数据传输时间。除此之外,SDRAM模块在RAS信号之后,需要经过一段时间,才能进行预充电(记为tRAS)。它的值很大,一般达到tRP的2到3倍。如果在某个RAS信号之后,只有一个CAS信号,而且数据只传输很少几个周期,那么就有问题了。假设在图2.9中,第一个CAS信号是直接跟在一个RAS信号后免的,而tRAS为8个周期。那么预充电命令还需要被推迟一个周期,因为tRCD、CL和tRP加起来才7个周期。

DDR模块往往用w-z-y-z-T来表示。例如,2-3-2-8-T1,意思是:

w 2 CAS时延(CL)

x 3 RAS-to-CAS时延(t RCD)

y 2 RAS预充电时间(t RP)

z 8 激活到预充电时间(t RAS)

T T1 命令速率

当然,除以上的参数外,还有许多其它参数影响命令的发送与处理。但以上5个参数已经足以确定模块的性能。

在解读计算机性能参数时,这些信息可能会派上用场。而在购买计算机时,这些信息就更有用了,因为它们与FSB/SDRAM速度一起,都是决定计算机速度的关键因素。

喜欢冒险的读者们还可以利用它们来调优系统。有些计算机的BIOS可以让你修改这些参数。SDRAM模块有一些可编程寄存器,可供设置参数。BIOS一般会挑选最佳值。如果RAM模块的质量足够好,我们可以在保持系统稳定的前提下将减小以上某个时延参数。互联网上有大量超频网站提供了相关的文档。不过,这是有风险的,需要大家自己承担,可别怪我没有事先提醒哟。

2.2.3 重充电

谈到DRAM的访问时,重充电是常常被忽略的一个主题。在2.1.2中曾经介绍,DRAM必须保持刷新。……行在充电时是无法访问的。[highperfdram]的研究发现,“令人吃惊,DRAM刷新对性能有着巨大的影响”。

根据JEDEC规范,DRAM单元必须保持每64ms刷新一次。对于8192行的DRAM,这意味着内存控制器平均每7.8125µs就需要发出一个刷新命令(在实际情况下,由于刷新命令可以纳入队列,因此这个时间间隔可以更大一些)。刷新命令的调度由内存控制器负责。DRAM模块会记录上一次刷新行的地址,然后在下次刷新请求时自动对这个地址进行递增。

对于刷新及发出刷新命令的时间点,程序员无法施加影响。但我们在解读性能参数时有必要知道,它也是DRAM生命周期的一个部分。如果系统需要读取某个重要的字,而刚好它所在的行正在刷新,那么处理器将会被延迟很长一段时间。刷新的具体耗时取决于DRAM模块本身。

2.2.4 内存类型

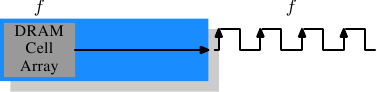

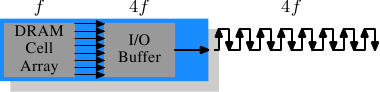

我们有必要花一些时间来了解一下目前流行的内存,以及那些即将流行的内存。首先从SDR(单倍速)SDRAM开始,因为它们是DDR(双倍速)SDRAM的基础。SDR非常简单,内存单元和数据传输率是相等的。

图2.10: SDR SDRAM的操作

在图2.10中,DRAM单元阵列能以等同于内存总线的速率输出内容。假设DRAM单元阵列工作在100MHz上,那么总线的数据传输率可以达到100Mb/s。所有组件的频率f保持相同。由于提高频率会导致耗电量增加,所以提高吞吐量需要付出很高的的代价。如果是很大规模的内存阵列,代价会非常巨大。{功率 = 动态电容 x 电压2 x 频率}。而且,提高频率还需要在保持系统稳定的情况下提高电压,这更是一个问题。因此,就有了DDR SDRAM(现在叫DDR1),它可以在不提高频率的前提下提高吞吐量。

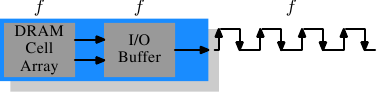

图2.11 DDR1 SDRAM的操作

我们从图2.11上可以看出DDR1与SDR的不同之处,也可以从DDR1的名字里猜到那么几分,DDR1的每个周期可以传输两倍的数据,它的上升沿和下降沿都传输数据。有时又被称为“双泵(double-pumped)”总线。为了在不提升频率的前提下实现双倍传输,DDR引入了一个缓冲区。缓冲区的每条数据线都持有两位。它要求内存单元阵列的数据总线包含两条线。实现的方式很简单,用同一个列地址同时访问两个DRAM单元。对单元阵列的修改也很小。

SDR DRAM是以频率来命名的(例如,对应于100MHz的称为PC100)。为了让DDR1听上去更好听,营销人员们不得不想了一种新的命名方案。这种新方案中含有DDR模块可支持的传输速率(DDR拥有64位总线):

100MHz x 64位 x 2 = 1600MB/s

于是,100MHz频率的DDR模块就被称为PC1600。由于1600 > 100,营销方面的需求得到了满足,听起来非常棒,但实际上仅仅只是提升了两倍而已。{我接受两倍这个事实,但不喜欢类似的数字膨胀戏法。}

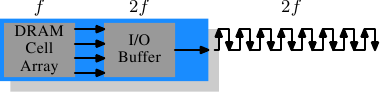

图2.12: DDR2 SDRAM的操作

为了更进一步,DDR2有了更多的创新。在图2.12中,最明显的变化是,总线的频率加倍了。频率的加倍意味着带宽的加倍。如果对单元阵列的频率加倍,显然是不经济的,因此DDR2要求I/O缓冲区在每个时钟周期读取4位。也就是说,DDR2的变化仅在于使I/O缓冲区运行在更高的速度上。这是可行的,而且耗电也不会显著增加。DDR2的命名与DDR1相仿,只是将因子2替换成4(四泵总线)。图2.13显示了目前常用的一些模块的名称。

阵列频率 总线频率 数据率 名称(速率) 名称

(FSB)133MHz 266MHz 4,256MB/s PC2-4200 DDR2-533 166MHz 333MHz 5,312MB/s PC2-5300 DDR2-667 200MHz 400MHz 6,400MB/s PC2-6400 DDR2-800 250MHz 500MHz 8,000MB/s PC2-8000 DDR2-1000 266MHz 533MHz 8,512MB/s PC2-8500 DDR2-1066

图2.13: DDR2模块名

在命名方面还有一个拧巴的地方。FSB速度是用有效频率来标记的,即把上升、下降沿均传输数据的因素考虑进去,因此数字被撑大了。所以,拥有266MHz总线的133MHz模块有着533MHz的FSB“频率”。

DDR3要求更多的改变(这里指真正的DDR3,而不是图形卡中假冒的GDDR3)。电压从1.8V下降到1.5V。由于耗电是与电压的平方成正比,因此可以节约30%的电力。加上管芯(die)的缩小和电气方面的其它进展,DDR3可以在保持相同频率的情况下,降低一半的电力消耗。或者,在保持相同耗电的情况下,达到更高的频率。又或者,在保持相同热量排放的情况下,实现容量的翻番。

DDR3模块的单元阵列将运行在内部总线的四分之一速度上,DDR3的I/O缓冲区从DDR2的4位提升到8位。见图2.14。

图2.14: DDR3 SDRAM的操作

一开始,DDR3可能会有较高的CAS时延,因为DDR2的技术相比之下更为成熟。由于这个原因,DDR3可能只会用于DDR2无法达到的高频率下,而且带宽比时延更重要的场景。此前,已经有讨论指出,1.3V的DDR3可以达到与DDR2相同的CAS时延。无论如何,更高速度带来的价值都会超过时延增加带来的影响。

DDR3可能会有一个问题,即在1600Mb/s或更高速率下,每个通道的模块数可能会限制为1。在早期版本中,这一要求是针对所有频率的。我们希望这个要求可以提高一些,否则系统容量将会受到严重的限制。

图2.15显示了我们预计中各DDR3模块的名称。JEDEC目前同意了前四种。由于Intel的45nm处理器是1600Mb/s的FSB,1866Mb/s可以用于超频市场。随着DDR3的发展,可能会有更多类型加入。

图2.15: DDR3模块名

阵列频率 总线频率 数据速率 名称(速率) 名称

(FSB)100MHz 400MHz 6,400MB/s PC3-6400 DDR3-800 133MHz 533MHz 8,512MB/s PC3-8500 DDR3-1066 166MHz 667MHz 10,667MB/s PC3-10667 DDR3-1333 200MHz 800MHz 12,800MB/s PC3-12800 DDR3-1600 233MHz 933MHz 14,933MB/s PC3-14900 DDR3-1866

所有的DDR内存都有一个问题:不断增加的频率使得建立并行数据总线变得十分困难。一个DDR2模块有240根引脚。所有到地址和数据引脚的连线必须被布置得差不多一样长。更大的问题是,如果多于一个DDR模块通过菊花链连接在同一个总线上,每个模块所接收到的信号随着模块的增加会变得越来越扭曲。DDR2规范允许每条总线(又称通道)连接最多两个模块,DDR3在高频率下只允许每个通道连接一个模块。每条总线多达240根引脚使得单个北桥无法以合理的方式驱动两个通道。替代方案是增加外部内存控制器(如图2.2),但这会提高成本。

这意味着商品主板所搭载的DDR2或DDR3模块数将被限制在最多四条,这严重限制了系统的最大内存容量。即使是老旧的32位IA-32处理器也可以使用64GB内存。即使是家庭对内存的需求也在不断增长,所以,某些事必须开始做了。

一种解法是,在处理器中加入内存控制器,我们在第2节中曾经介绍过。AMD的Opteron系列和Intel的CSI技术就是采用这种方法。只要我们能把处理器要求的内存连接到处理器上,这种解法就是有效的。如果不能,按照这种思路就会引入NUMA架构,当然同时也会引入它的缺点。而在有些情况下,我们需要其它解法。

Intel针对大型服务器方面的解法(至少在未来几年),是被称为全缓冲DRAM(FB-DRAM)的技术。FB-DRAM采用与DDR2相同的器件,因此造价低廉。不同之处在于它们与内存控制器的连接方式。FB-DRAM没有用并行总线,而用了串行总线(Rambus DRAM had this back when, too, 而SATA是PATA的继任者,就像PCI Express是PCI/AGP的继承人一样)。串行总线可以达到更高的频率,串行化的负面影响,甚至可以增加带宽。使用串行总线后

- 每个通道可以使用更多的模块。

- 每个北桥/内存控制器可以使用更多的通道。

- 串行总线是全双工的(两条线)。

FB-DRAM只有69个脚。通过菊花链方式连接多个FB-DRAM也很简单。FB-DRAM规范允许每个通道连接最多8个模块。

在对比下双通道北桥的连接性,采用FB-DRAM后,北桥可以驱动6个通道,而且脚数更少——6x69对比2x240。每个通道的布线也更为简单,有助于降低主板的成本。

全双工的并行总线过于昂贵。而换成串行线后,这不再是一个问题,因此串行总线按全双工来设计的,这也意味着,在某些情况下,仅靠这一特性,总线的理论带宽已经翻了一倍。还不止于此。由于FB-DRAM控制器可同时连接6个通道,因此可以利用它来增加某些小内存系统的带宽。对于一个双通道、4模块的DDR2系统,我们可以用一个普通FB-DRAM控制器,用4通道来实现相同的容量。串行总线的实际带宽取决于在FB-DRAM模块中所使用的DDR2(或DDR3)芯片的类型。

我们可以像这样总结这些优势:

DDR2 FB-DRAM

DDR2 FB-DRAM 脚 240 69 通道 2 6 每通道DIMM数 2 8 最大内存 16GB 192GB 吞吐量 ~10GB/s ~40GB/s

如果在单个通道上使用多个DIMM,会有一些问题。信号在每个DIMM上都会有延迟(尽管很小),也就是说,延迟是递增的。不过,如果在相同频率和相同容量上进行比较,FB-DRAM总是能快过DDR2及DDR3,因为FB-DRAM只需要在每个通道上使用一个DIMM即可。而如果说到大型内存系统,那么DDR更是没有商用组件的解决方案。

2.2.5 结论

通过本节,大家应该了解到访问DRAM的过程并不是一个快速的过程。至少与处理器的速度相比,或与处理器访问寄存器及缓存的速度相比,DRAM的访问不算快。大家还需要记住CPU和内存的频率是不同的。Intel Core 2处理器运行在2.933GHz,而1.066GHz FSB有11:1的时钟比率(注: 1.066GHz的总线为四泵总线)。那么,内存总线上延迟一个周期意味着处理器延迟11个周期。绝大多数机器使用的DRAM更慢,因此延迟更大。在后续的章节中,我们需要讨论延迟这个问题时,请把以上的数字记在心里。

前文中读命令的时序图表明,DRAM模块可以支持高速数据传输。每个完整行可以被毫无延迟地传输。数据总线可以100%被占。对DDR而言,意味着每个周期传输2个64位字。对于DDR2-800模块和双通道而言,意味着12.8GB/s的速率。

但是,除非是特殊设计,DRAM的访问并不总是串行的。访问不连续的内存区意味着需要预充电和RAS信号。于是,各种速度开始慢下来,DRAM模块急需帮助。预充电的时间越短,数据传输所受的惩罚越小。

硬件和软件的预取(参见第6.3节)可以在时序中制造更多的重叠区,降低延迟。预取还可以转移内存操作的时间,从而减少争用。我们常常遇到的问题是,在这一轮中生成的数据需要被存储,而下一轮的数据需要被读出来。通过转移读取的时间,读和写就不需要同时发出了。

2.3 主存的其它用户

除了CPU外,系统中还有其它一些组件也可以访问主存。高性能网卡或大规模存储控制器是无法承受通过CPU来传输数据的,它们一般直接对内存进行读写(直接内存访问,DMA)。在图2.1中可以看到,它们可以通过南桥和北桥直接访问内存。另外,其它总线,比如USB等也需要FSB带宽,即使它们并不使用DMA,但南桥仍要通过FSB连接到北桥。

DMA当然有很大的优点,但也意味着FSB带宽会有更多的竞争。在有大量DMA流量的情况下,CPU在访问内存时必然会有更大的延迟。我们可以用一些硬件来解决这个问题。例如,通过图2.3中的架构,我们可以挑选不受DMA影响的节点,让它们的内存为我们的计算服务。还可以在每个节点上连接一个南桥,将FSB的负荷均匀地分担到每个节点上。除此以外,还有许多其它方法。我们将在第6节中介绍一些技术和编程接口,它们能够帮助我们通过软件的方式改善这个问题。

最后,还需要提一下某些廉价系统,它们的图形系统没有专用的显存,而是采用主存的一部分作为显存。由于对显存的访问非常频繁(例如,对于1024x768、16bpp、60Hz的显示设置来说,需要95MB/s的数据速率),而主存并不像显卡上的显存,并没有两个端口,因此这种配置会对系统性能、尤其是时延造成一定的影响。如果大家对系统性能要求比较高,最好不要采用这种配置。这种系统带来的问题超过了本身的价值。人们在购买它们时已经做好了性能不佳的心理准备。

继续阅读:

- 第2节: CPU的高速缓存

- 第3节: 虚拟内存

- 第4节: NUMA系统

- 第5节: 程序员可以做什么 - 高速缓存的优化

- 第6节: 程序员可以做什么 - 多线程的优化

- 第7节: 内存性能工具

- 第8节: 未来的技术

- 第9节: 附录与参考书目

内存部分2:CPU缓存

今天的CPU比25年前复杂得多。在那些日子里,CPU内核的频率与内存总线的频率相同。内存访问仅比寄存器访问慢一点。但是在90年代初,情况发生了巨大变化,当时CPU设计人员增加了CPU内核的频率,但是内存总线的频率和RAM芯片的性能却没有成比例地增加。如上一节所述,这并不是由于无法构建更快的RAM。可能,但不经济。与当前CPU内核一样快的RAM比任何动态RAM贵几个数量级。

如果在具有很少,非常快的RAM的机器和具有很多相对较快的RAM的机器之间进行选择,则在工作集大小超过小RAM大小以及访问辅助存储介质的成本的情况下,第二个总是赢家。作为硬盘驱动器。这里的问题是辅助存储(通常是硬盘)的速度,必须使用辅助存储来容纳工作集的换出部分。访问这些磁盘要比DRAM访问慢几个数量级。

幸运的是,这不一定是一个全有或全无的决定。除了大量的DRAM外,计算机还可以具有少量的高速SRAM。一种可能的实现方式是将处理器的地址空间的某个区域专用为包含SRAM,其余为DRAM。操作系统的任务将是优化分配数据以利用SRAM。基本上,SRAM在这种情况下用作处理器寄存器集的扩展。

尽管这是一种可能的实现方式,但它并不可行。忽略将这种SRAM支持的内存的物理资源映射到进程的虚拟地址空间的问题(这本身很难做到),这种方法将需要每个进程在软件中管理该内存区域的分配。存储器区域的大小可能因处理器而异(即,处理器具有不同数量的昂贵的SRAM支持的存储器)。组成程序一部分的每个模块都将要求其共享快速存储器,这会通过同步要求而带来额外的成本。简而言之,具有快速内存的收益将被管理资源的开销完全吞噬。

因此,代替将SRAM置于OS或用户的控制之下,它成为一种资源,由处理器透明地使用和管理。在这种模式下,SRAM用于在主存储器中制作数据的临时副本(换句话说,用于缓存),该数据很可能会被处理器很快使用。这是可能的,因为程序代码和数据具有时间和空间局部性。这意味着在很短的时间内,很有可能重用相同的代码或数据。对于代码而言,这意味着代码中最有可能出现循环,从而使同一代码一遍又一遍地执行(空间局部性的完美案例 )。数据访问也理想地限于小区域。即使在短时间内使用的内存没有紧密结合在一起,也很可能在不久之后重新使用相同的数据(时间局部性)。对于代码,这意味着,例如,在循环中进行了一个函数调用,并且该函数位于地址空间中的其他位置。该函数可能在内存中很远,但是对该函数的调用将及时关闭。对于数据而言,这意味着一次限制使用的内存总量(工作集大小)是理想的,但由于RAM的随机访问性质,使用的内存并不紧密。认识到局部性是当今我们使用CPU缓存概念的关键。

一个简单的计算可以显示理论上缓存的有效性。假设对主存储器的访问需要200个周期,而对缓存的访问则需要15个周期。然后,如果没有缓存,则使用100个数据元素进行100次编码将在内存操作上花费2,000,000个周期,如果可以缓存所有数据,则仅花费168,500个周期。增长了91.5%。

用于缓存的SRAM的大小比主存储器小很多倍。根据作者使用带CPU缓存的工作站的经验,缓存大小始终约为主内存大小的1/1000(今天:4MB缓存和4GB主内存)。仅此一点并不构成问题。如果工作集(当前正在处理的数据集)的大小小于缓存大小,则没有关系。但是,计算机无缘无故拥有大量的主要记忆。工作集必然大于缓存。对于运行多个进程的系统尤其如此,其中工作集的大小是所有单个进程和内核的大小之和。

解决高速缓存的有限大小所需的是一组好的策略,以确定在任何给定时间应缓存的内容。由于并非完全同时使用工作集的所有数据,因此 我们可以使用技术将缓存中的某些数据临时替换为其他数据。也许可以在实际需要数据之前完成此操作。这种预取将消除访问主内存的一些成本,因为它相对于程序的执行是异步发生的。所有这些技术以及更多技术都可以用来使缓存看起来比实际更大。我们将在3.3节中讨论它们。一旦利用了所有这些技术,就应由程序员来帮助处理器。如何做到这一点将在第6节中讨论。

3.1概述中的CPU缓存

在深入研究CPU缓存实现的技术细节之前,一些读者可能会发现首先更详细地了解缓存如何适合现代计算机系统的“全局”是有用的。

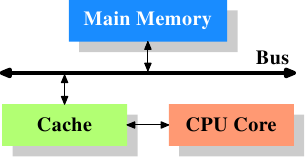

图3.1:最低缓存配置

图3.1显示了最低缓存配置。它对应于在部署CPU缓存的早期系统中可以找到的体系结构。CPU内核不再直接连接到主存储器。{在更早的系统中,缓存也像CPU和主存储器一样被附加到系统总线上。这不是真正的解决方案,而是更多的技巧。}所有的加载和存储都必须经过缓存。CPU内核与缓存之间的连接是一种特殊的快速连接。在简化表示中,主存储器和高速缓存连接到系统总线,该系统总线也可用于与系统的其他组件进行通信。我们将系统总线称为“ FSB”,这是当今使用的名称。请参阅第2.2节。在本节中,我们将忽略北桥。假定存在它是为了促进CPU与主存储器的通信。

即使过去几十年的计算机使用了von Neumann架构,经验也表明,分离用于代码和数据的缓存是有利的。自1993年以来,英特尔一直使用独立的代码和数据缓存,从此再也没有回头。代码和数据所需的内存区域几乎彼此独立,这就是为什么独立的缓存可以更好地工作的原因。近年来,出现了另一个优势:最常用处理器的指令解码步骤很慢;缓存解码的指令可以加快执行速度,特别是当管道由于预测错误或无法预测的分支而为空时。

引入缓存后不久,系统变得更加复杂。高速缓存与主内存之间的速度差异再次增大,以至于添加了另一级高速缓存,该级别比第一级高速缓存更大,更慢。出于经济原因,仅增加一级缓存的大小是不可行的。如今,甚至有一些机器可以正常使用三级缓存。具有这种处理器的系统如图3.2所示。随着单个CPU中内核数量的增加,将来缓存级别的数量可能还会增加。

图3.2:具有3级缓存的处理器

图3.2显示了缓存的三个级别,并介绍了我们将在本文档的其余部分中使用的术语。L1d是1级数据高速缓存,L1i是1级指令高速缓存,以此类推。实际上,数据流不需要在从核心到主存储器的途中通过任何更高级别的缓存。CPU设计人员在设计缓存的接口时有很大的自由度。对于程序员来说,这些设计选择是看不见的。

另外,我们拥有具有多个核心的处理器,每个核心可以具有多个“线程”。芯和一个螺纹之间的区别是,单独的芯具有的单独的副本(几乎{早期多核处理器甚至有单独的2级级高速缓存和无3次级高速缓存。 })中的所有硬件资源。除非内核同时使用相同的资源(例如,与外部的连接),否则它们可以完全独立地运行。另一方面,线程几乎共享处理器的所有资源。英特尔的线程实现只为线程提供了单独的寄存器,即使这是有限的,某些寄存器也是共享的。因此,现代CPU的完整外观如图3.3所示。

图3.3:多处理器,多核,多线程

在此图中,我们有两个处理器,每个处理器具有两个内核,每个内核具有两个线程。线程共享1级缓存。核心(深灰色阴影)具有单独的1级缓存。CPU的所有内核共享更高级别的缓存。当然,这两个处理器(两个大盒子用浅灰色阴影表示)不共享任何缓存。所有这些都很重要,尤其是当我们讨论高速缓存对多进程和多线程应用程序的影响时。

3.2高速缓存操作

为了了解使用缓存的成本和节省,我们必须将第2节中有关机器体系结构和RAM技术的知识与上一节中描述的缓存结构相结合。

默认情况下,CPU内核读取或写入的所有数据都存储在缓存中。有一些无法缓存的内存区域,但这只是OS实现者必须关心的事情;应用程序程序员看不到它。还有一些指令允许程序员有意绕过某些缓存。这将在第6节中讨论。

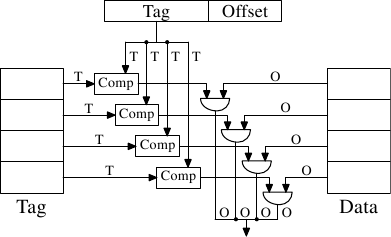

如果CPU需要数据字,则首先搜索缓存。显然,缓存不能包含整个主内存的内容(否则我们就不需要缓存),但是由于所有内存地址都是可缓存的,因此每个缓存条目都使用主内存中数据字的地址进行标记。这样,读取或写入地址的请求可以在缓存中搜索匹配的标签。在此上下文中,该地址可以是虚拟地址,也可以是物理地址,具体取决于缓存的实现。

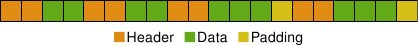

由于标签除了实际内存外还需要空间,因此选择单词作为缓存的粒度效率很低。对于x86机器上的32位字,标签本身可能需要32位或更多。此外,由于空间局部性是高速缓存所基于的原理之一,因此不考虑这一点将很不利。由于相邻的内存可能会一起使用,因此也应该一起将其加载到缓存中。还要记住我们在2.2.1节中学到的内容:如果RAM模块可以连续传输许多数据字而无需新的CAS甚至RAS,则它们的效率要高得多。信号。因此,存储在高速缓存中的条目不是单个单词,而是几个连续单词的“行”。在早期的缓存中,这些行的长度为32个字节。现在的标准是64个字节。如果内存总线为64位宽,则意味着每条高速缓存线进行8次传输。DDR有效地支持此传输模式。

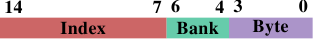

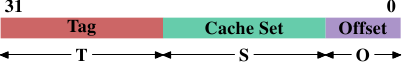

当处理器需要内存内容时,整个高速缓存行将被加载到L1d中。通过根据缓存行大小屏蔽地址值来计算每个缓存行的内存地址。对于64字节的高速缓存行,这意味着低6位被清零。丢弃的位用作高速缓存行的偏移量。在某些情况下,剩余的位用于在缓存中定位该行并作为标记。实际上,地址值分为三个部分。对于32位地址,它可能如下所示:

高速缓存行大小为2 O时 ,低O位用作高速缓存行的偏移量。接下来的S位选择“缓存集”。我们很快将详细介绍为什么将集合而不是单个插槽用于高速缓存行。到目前为止,足以理解有2 S套高速缓存行。这样就剩下构成标签的前32 位-S - O = T位。这些T位是与每个高速缓存行相关联的值,以区分所有 别名{地址中具有相同S部分的所有高速缓存行都由相同别名知道。}缓存在同一缓存集中。用于寻址缓存集的S位不必存储,因为它们对于同一集合中的所有缓存行都是相同的。

当指令修改内存时,处理器仍然必须首先加载高速缓存行,因为没有一条指令会立即修改整个高速缓存行(规则除外:如第6.1节所述的写合并)。因此,必须加载写操作之前的高速缓存行的内容。缓存不可能保留部分缓存行。已被写入但尚未被写回到主存储器的高速缓存行被称为“脏”。一旦写入,脏标志将被清除。

为了能够在缓存中加载新数据,几乎总是首先需要在缓存中腾出空间。从L1d逐出将高速缓存行向下推入L2(使用相同的高速缓存行大小)。当然,这意味着必须在L2中放置空间。反过来,这可能会将内容推入L3并最终推入主存储器。每次搬迁都越来越昂贵。这里描述的是专用缓存的模型,这是现代AMD和VIA处理器首选的模型 。英特尔实现了包含性缓存{这种概括并不完全正确。一些缓存是互斥的,某些包含缓存具有互斥的缓存属性。} L1d中的每个高速缓存行也存在于L2中。因此,从L1d驱逐要快得多。有了足够的L2缓存,浪费在两个地方的内容上的内存的缺点是最小的,并且在收回时会得到回报。专用高速缓存的可能优点是,加载新的高速缓存行仅需触摸L1d而不是L2,这可能会更快。

只要不更改为处理器体系结构定义的内存模型,就可以允许CPU根据需要管理高速缓存。例如,处理器利用很少或没有内存总线活动,并主动将脏的缓存行写回到主内存是非常好的选择。x86和x86-64的处理器之间,制造商之间甚至同一制造商的模型之间的各种缓存体系结构,都证明了内存模型抽象的强大功能。

在对称多处理器(SMP)系统中,CPU的缓存不能彼此独立地工作。所有处理器都应该始终看到相同的内存内容。维持这种统一的内存视图称为“缓存一致性”。如果一个处理器仅查看其自己的缓存和主内存,它将看不到其他处理器中脏缓存行的内容。提供从另一处理器对一个处理器的高速缓存的直接访问将是非常昂贵的,并且是巨大的瓶颈。而是,处理器检测另一个处理器何时要读取或写入某个高速缓存行。

如果检测到写访问并且处理器在其高速缓存中具有该高速缓存行的干净副本,则将该高速缓存行标记为无效。将来的引用将需要重新加载缓存行。请注意,对另一个CPU的读取访问并不一定要使它无效,可以很好地保留多个干净副本。

更复杂的缓存实现允许发生另一种可能性。如果当前在第一个处理器的缓存中将另一个处理器要读取或写入的缓存行标记为脏,则需要采取不同的措施。在这种情况下,主存储器已过期,发出请求的处理器必须从第一个处理器获取缓存行内容。通过侦听,第一个处理器会注意到这种情况,并自动向发出请求的处理器发送数据。该操作绕过了主内存,尽管在某些实现中,内存控制器应该注意到这种直接传输并将更新的缓存行内容存储在主内存中。如果访问是为了写入第一个处理器,则使它的本地高速缓存行副本无效。

随着时间的流逝,已经开发了许多高速缓存一致性协议。最重要的是MESI,我们将在3.3.4节中介绍。所有这一切的结果可以归纳为一些简单的规则:

- 任何其他处理器的高速缓存中都没有脏高速缓存行。

- 同一缓存行的干净副本可以驻留在任意多个缓存中。

如果可以维持这些规则,那么即使在多处理器系统中,处理器也可以有效地使用其缓存。处理器所需要做的就是监视彼此的写访问,并将地址与其本地缓存中的地址进行比较。在下一节中,我们将进一步介绍有关实施的更多细节,尤其是成本。

最后,我们至少应该给与缓存命中和未命中相关的成本印象。这些是英特尔为奔腾M列出的数字:

去哪里 周期数 寄存器 <= 1 1天 〜3 L2 〜14 主记忆体 〜240

这些是以CPU周期为单位的实际访问时间。有趣的是,对于片上L2缓存,访问时间的很大一部分(可能甚至是大部分)是由线路延迟引起的。这是一个物理限制,只会随着高速缓存大小的增加而变得更糟。只有缩小工艺(例如,从Merom的60nm到Intel的Penryn的45nm)才能提高这些数字。

该表中的数字看起来很高,但是幸运的是,不必为每次发生的高速缓存加载和未命中支付全部费用。成本的某些部分可以隐藏。当今的处理器都使用不同长度的内部管线,在这些管线中对指令进行解码并准备执行。如果将值传输到寄存器,则准备工作的一部分是从内存(或缓存)中加载值。如果内存加载操作可以在管道中足够早地开始,则它可能与其他操作并行发生,并且可能隐藏了加载的全部成本。对于L1d,这通常是可能的;也适用于一些具有较长L2流水线的处理器。

尽早开始读取内存有很多障碍。这可能很简单,因为没有足够的资源来进行内存访问,或者可能是加载的最终地址由于另一条指令而变得较晚才可用。在这些情况下,无法完全隐藏负载成本。

对于写操作,CPU不必等待该值安全地存储在内存中。只要执行以下指令似乎与将值存储在内存中具有相同的效果,就不会阻止CPU使用快捷方式。它可以尽早开始执行下一条指令。在影子寄存器的帮助下,影子寄存器可以保存常规寄存器中不再可用的值,甚至可以更改要在不完整的写操作中存储的值。

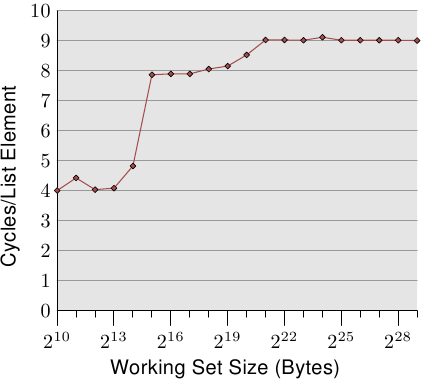

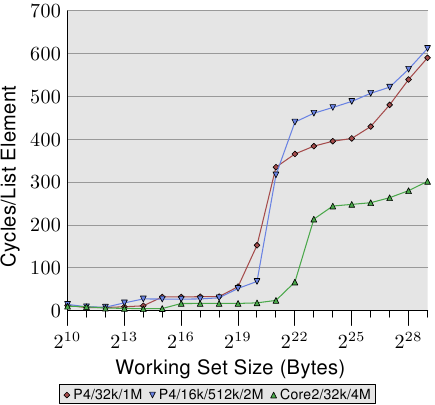

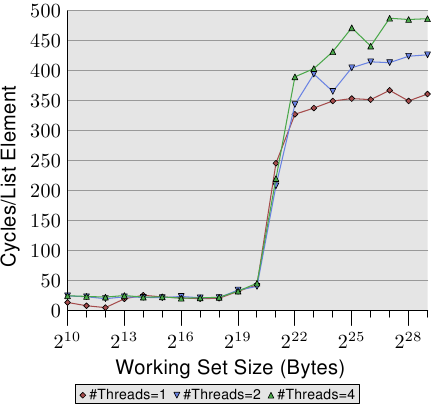

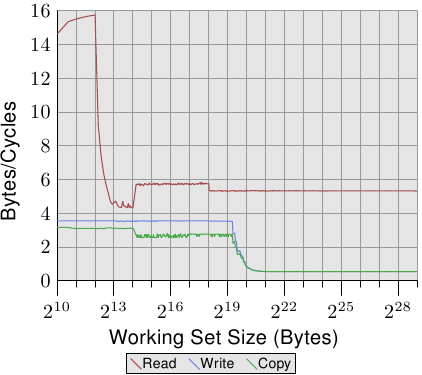

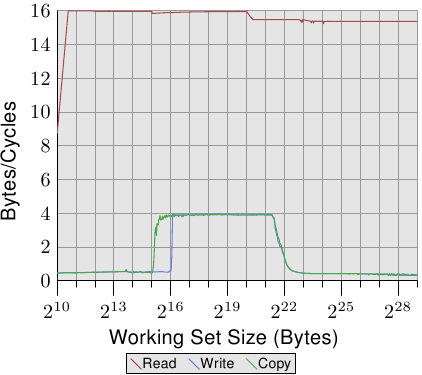

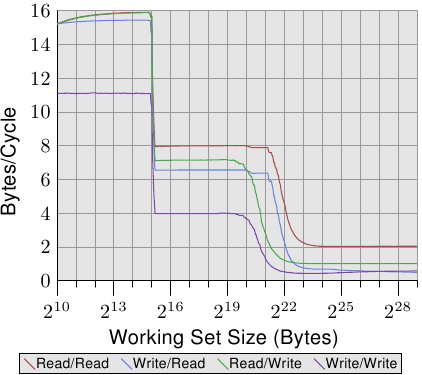

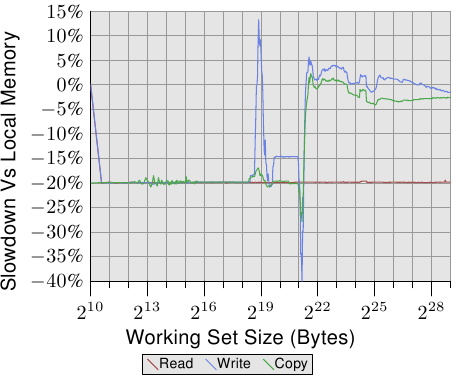

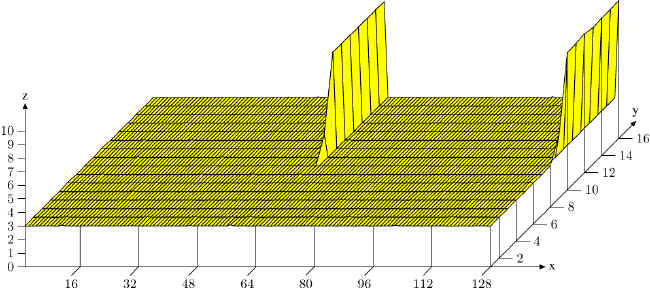

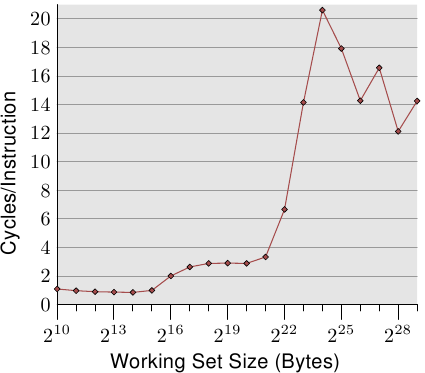

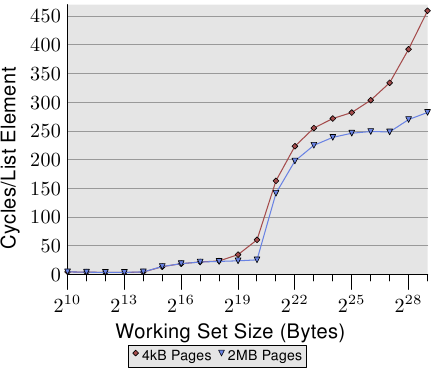

图3.4:随机写入的访问时间

有关缓存行为的影响的说明,请参见图3.4。稍后我们将讨论生成数据的程序。它是对程序的简单模拟,该程序以随机方式重复访问可配置的内存量。每个数据项都有固定的大小。元素的数量取决于所选的工作集大小。Y轴显示处理一个元素所需的平均CPU周期数。请注意,Y轴的比例是对数的。在所有此类X轴图中同样如此。工作集的大小始终以2的幂表示。

该图显示了三个不同的平台。这并不奇怪:特定的处理器具有L1d和L2高速缓存,但没有L3。根据一些经验,我们可以推断出L1d的大小为2 13个字节,而L2的大小为2 20个字节。如果整个工作集都适合L1d,则每个元素的每次操作周期都小于10。一旦超出L1d大小,处理器就必须从L2加载数据,并且平均时间会上升到大约28。一旦L2不足现在,时间跃升至480个循环甚至更多。这是许多或大多数操作必须从主存储器加载数据的时候。更糟糕的是:由于数据正在被修改,脏的缓存行也必须被写回。

该图应有足够的动机来研究有助于改进缓存使用率的编码改进。在这里,我们谈论的不是百分之几;我们谈论的是有时可能的数量级改进。在第6节中,我们将讨论允许编写更有效代码的技术。下一节将详细介绍CPU缓存设计。有知识是好的,但对于本文的其余部分则不是必需的。因此可以跳过本节。

3.3 CPU缓存实现细节

高速缓存实现者的问题是,巨大的主内存中的每个单元都可能必须被高速缓存。如果程序的工作集足够大,则意味着有许多主内存位置会争用缓存中的每个位置。以前已经注意到,缓存与主内存大小的比例为1:1000并不罕见。

3.3.1关联性

有可能实现一个高速缓存,其中每个高速缓存行可以保存任何内存位置的副本。这称为完全关联缓存。为了访问高速缓存行,处理器核心将必须将每个高速缓存行的标签与请求地址的标签进行比较。标签将由地址的整个部分组成,而不是高速缓存行的偏移量(也就是说, 第3.2节中的S为零)。

有一些这样实现的缓存,但是通过查看当前使用的L2的数量,将表明这是不切实际的。给定一个具有64B高速缓存行的4MB高速缓存,该高速缓存将具有65,536个条目。为了获得足够的性能,缓存逻辑必须能够在短短几个周期内从所有这些条目中选择一个与给定标签匹配的条目。实现这一点的努力将是巨大的。

图3.5:完全关联的缓存原理图

对于每个高速缓存行,都需要一个比较器来比较大标签(注意,S为零)。每个连接旁边的字母表示以位为单位的宽度。如果未给出,则为单条位线。每个比较器必须比较两个T位宽的值。然后,基于结果,选择适当的缓存行内容并使之可用。这需要合并尽可能多的 O数据行,因为有缓存桶。实现单个比较器所需的晶体管数量很大,特别是因为它必须非常快地工作。没有迭代比较器可用。节省比较器数量的唯一方法是通过迭代比较标签来减少比较器的数量。出于与迭代比较器不相同的原因,这是不合适的:它花费的时间太长。

完全关联的缓存适用于小型缓存(例如,某些Intel处理器上的TLB缓存是完全关联的),但这些缓存很小,甚至很小。我们最多谈论的是几十个条目。

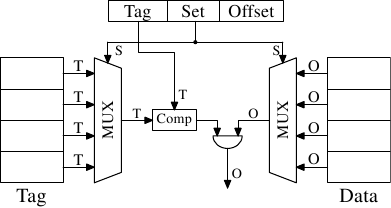

对于L1i,L1d和更高级别的缓存,需要一种不同的方法。可以做的是限制搜索。在最极端的限制下,每个标签都恰好映射到一个缓存条目。计算很简单:给4MB / 64B高速缓存提供65,536个条目,我们可以使用地址的6至21位(16位)直接寻址每个条目。低6位是高速缓存行的索引。

图3.6:直接映射的缓存原理图

这样的直接映射缓存如图3.6所示,它非常快速且易于实施。它仅需要一个比较器,一个多路复用器(在此图中两个是将标签和数据分开的,但这对设计不是硬性要求),以及一些逻辑来仅选择有效的缓存行内容。由于速度要求,比较器很复杂,但是现在只有一个。结果,可以花更多的精力来加快速度。这种方法的真正复杂性在于多路复用器。简单多路复用器中的晶体管数量随O(log N)的增加而增加,其中N是高速缓存线的数量。这是可以忍受的,但可能会变慢,在这种情况下,可以通过在多路复用器中的晶体管上花费更多的空间来并行化某些工作并提高速度来提高速度。随着高速缓存大小的增加,晶体管的总数可以缓慢增长,这使得该解决方案非常有吸引力。但这有一个缺点:只有程序使用的地址相对于直接映射所使用的位均匀分布时,它才能很好地工作。如果不是这样(通常是这种情况),则某些缓存条目会被大量使用,因此会被重复逐出,而其他缓存条目则几乎不会被使用或保持为空。

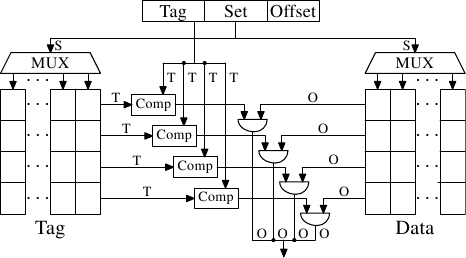

图3.7:集关联缓存原理图

通过使缓存集具有关联性可以解决此问题。集关联缓存结合了完整关联缓存和直接映射缓存的功能,可以在很大程度上避免这些设计的缺点。图3.7显示了集合关联缓存的设计。标签和数据存储分为几组,由地址选择。这类似于直接映射的缓存。但是,对于缓存中的每个设置值而言,只有一个值被缓存,而不是每个设置值只有一个元素。并行比较所有set成员的标签,这与完全关联的缓存的功能类似。

结果是高速缓存不容易被不幸的或故意选择具有相同组号的地址所破坏,同时高速缓存的大小不受可并行实现的比较器数量的限制。如果缓存增长(在此图中),那么只有列数增加,而不是行数增加。仅当增加高速缓存的关联性时,行数才会增加。如今,处理器对二级缓存或更高级别使用的关联性级别高达16。L1缓存通常会加倍。

| L2 快取 大小 | 关联性 | |||||||

|---|---|---|---|---|---|---|---|---|

| 直接 | 2 | 4 | 8 | |||||

| CL = 32 | CL = 64 | CL = 32 | CL = 64 | CL = 32 | CL = 64 | CL = 32 | CL = 64 | |

| 512k | 27,794,595 | 20,422,527 | 25,222,611 | 18,303,581 | 24,096,510 | 17,356,121 | 23,666,929 | 17,029,334 |

| 1M | 19,007,315 | 13,903,854 | 16,566,738 | 12,127,174 | 15,537,500 | 11,436,705 | 15,162,895 | 11,233,896 |

| 2M | 12,230,962 | 8,801,403 | 9,081,881 | 6,491,011 | 7,878,601 | 5,675,181 | 7,391,389 | 5,382,064 |

| 4M | 7,749,986 | 5,427,836 | 4,736,187 | 3,159,507 | 3,788,122 | 2,418,898 | 3,430,713 | 2,125,103 |

| 8M | 4,731,904 | 3,209,693 | 2,690,498 | 1,602,957 | 2,207,655 | 1,228,190 | 2,111,075 | 1,155,847 |

| 1600万 | 2,620,587 | 1,528,592 | 1,958,293 | 1,089,580 | 1,704,878 | 883,530 | 1,671,541 | 862,324 |

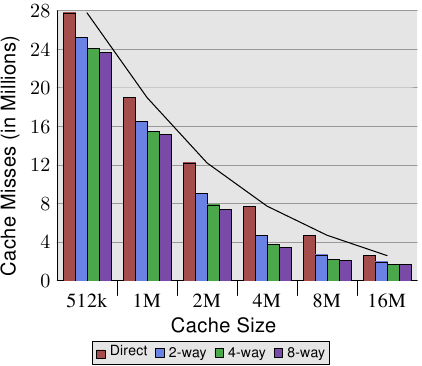

表3.1:缓存大小,关联性和行大小的影响

给定我们的4MB / 64B高速缓存和8路集关联性,我们剩下的高速缓存具有8,192个集,并且仅13位标签用于寻址高速缓存集。为了确定高速缓存集中的哪些条目(如果有)包含所寻址的高速缓存行,必须比较8个标签。在很短的时间内这样做是可行的。通过实验我们可以看到这是有道理的。

表3.1列出了用于更改高速缓存大小,高速缓存行大小和关联集大小的程序(在这种情况下,gcc,这是所有程序中最重要的基准)的L2高速缓存未命中数。在第7.2节中,我们将介绍该工具来模拟此测试所需的缓存。

以防万一这还不是很明显,所有这些值之间的关系是缓存大小为

缓存行大小×关联性×套数

通过使用以下方式将地址映射到缓存中

O =日志2缓存行大小

S =日志2集数

按照第3.2节中的图所示。

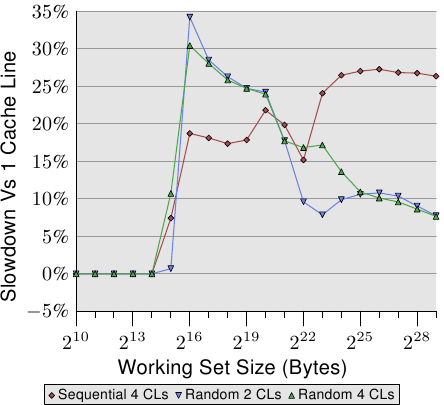

图3.8:缓存大小与关联性(CL = 32)

图3.8使表的数据更易理解。它显示了32字节的固定高速缓存行大小的数据。查看给定缓存大小的数字,可以发现关联确实可以帮助显着减少缓存未命中的次数。对于从直接映射到2路集关联高速缓存的8MB高速缓存,几乎可以节省44%的高速缓存未命中。与直接映射的缓存相比,处理器可以通过集合关联缓存将更多的工作集保留在缓存中。

在文献中,偶尔可以读到引入关联性与将缓存大小加倍具有相同的效果。在某些极端情况下确实如此,从4MB高速缓存到8MB高速缓存的跳转可以看出这一点。但是,对于进一步加倍的关联性而言,确实是不正确的。从数据中可以看出,连续增益要小得多。但是,我们不应该完全忽略这些影响。在示例程序中,峰值内存使用量为5.6M。因此,对于8MB高速缓存,同一高速缓存集不可能有太多(超过两个)用途。使用更大的工作集,可以节省更多的钱,正如我们从较小的缓存大小的关联性的更大好处中看到的那样。

通常,将高速缓存的关联性提高到8以上似乎对单线程工作负载几乎没有影响。随着使用共享L2的多核处理器的引入,情况发生了变化。现在,您基本上有两个程序在同一个缓存上命中,这实际上导致了关联性减半(或四核处理器四分之一)。因此可以预料,随着内核数量的增加,共享缓存的关联性应该会增加。一旦这不再可能(16路集关联已经很困难),处理器设计人员就必须开始使用共享的L3高速缓存以及更多,而L2高速缓存可能由一部分内核共享。

我们可以在图3.8中研究的另一个影响是高速缓存大小的增加如何帮助提高性能。在不知道工作集大小的情况下无法解释此数据。显然,与较小的缓存相比,与主内存一样大的缓存将带来更好的结果,因此,对具有可衡量的好处的最大缓存大小通常没有限制。

如上所述,工作集的峰值大小为5.6M。这没有给我们提供最大有用缓存大小的任何绝对数量,但可以让我们估计数量。问题在于,并非所有使用的内存都是连续的,因此,即使使用16M高速缓存和5.6M工作集,我们也会发生冲突(请参阅2路集关联16MB高速缓存相对于直接映射版本的好处) 。但是可以肯定的是,在相同的工作负载下,32MB高速缓存的好处可以忽略不计。但是谁说工作集必须保持不变?工作量随时间增长,因此缓存大小也应随之增加。当购买机器时,必须选择一个愿意支付的缓存大小,这是值得衡量的工作集大小。为什么如此重要,请参见图3.10。

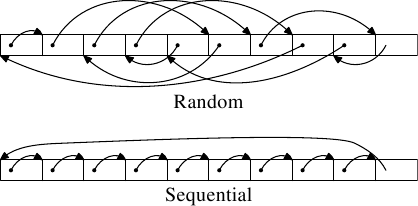

图3.9:测试内存布局

运行两种类型的测试。在第一个测试中,元素将被顺序处理。测试程序跟随指针n, 但是将数组元素链接在一起,以便按照在内存中找到它们的顺序遍历它们。这可以在图3.9的下部看到。最后一个元素有一个反向引用。在第二个测试中(该图的上部),以随机顺序遍历数组元素。在这两种情况下,数组元素都构成一个循环的单链列表。

3.3.2缓存效果的度量

通过测量程序可以创建所有图形,该程序可以模拟任意大小的工作集,读写访问权限以及顺序访问或随机访问。我们已经在图3.4中看到了一些结果。程序创建一个与该类型元素的工作集大小相对应的数组:

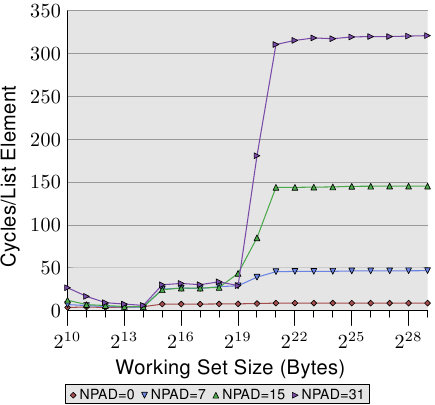

struct l { struct l * n; long int pad [NPAD]; };

使用n元素(按顺序或随机顺序)将所有条目链接在循环列表中。即使元素是按顺序排列的,从一个条目前进到下一个条目始终使用指针。该垫元素是有效载荷,它可以尽量增大。在某些测试中,数据被修改,而在另一些测试中,程序仅执行读取操作。

在性能度量中,我们谈论的是工作集大小。工作集由结构l 元素的数组组成。2 N字节的工作集包含

2 N / sizeof(结构l)

元素。显然sizeof(struct l)取决于NPAD的值 。对于32位系统,NPAD = 7表示每个数组元素的大小为32字节,对于64位系统,其大小为64字节。

单线程顺序访问

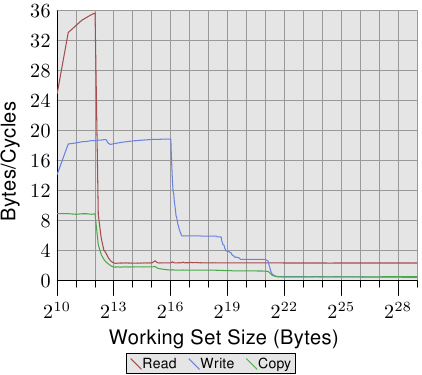

最简单的情况是遍历列表中的所有条目。列表元素顺序排列,密集排列。处理顺序是向前还是向后都无所谓,处理器可以很好地处理两个方向。我们在这里(以及随后的所有测试中)测量的是处理单个列表元素需要多长时间。时间单位是处理器周期。结果如图3.10所示。除非另有说明,所有测量均在64位模式下,这意味着结构的奔腾4的机器上制成升与NPAD = 0是在大小的8个字节。

图3.10:顺序读取访问,NPAD = 0

图3.11:几种尺寸的顺序读取

前两个测量值被噪声污染。测得的工作负载实在太小,无法滤除系统其余部分的影响。我们可以安全地假设所有值都处于4个循环级别。考虑到这一点,我们可以看到三个不同的级别:

- 工作集大小最大为2个14字节。

- 从2 15字节到2 20字节。

- 从2 21字节开始。

这些步骤很容易解释:处理器具有16kB L1d和1MB L2。我们看不到从一个级别到另一级别的过渡中的尖锐边缘,因为高速缓存也被系统的其他部分使用,因此高速缓存并非专门用于程序数据。特别地,L2缓存是统一缓存,也用于指令(注意:Intel使用包含性缓存)。

可能不太期望的是不同工作集大小的实际时间。L1d命中的时间是预期的:L1d命中后的加载时间在P4上约为4个周期。但是第二层访问呢?一旦L1d不足以保存数据,人们可能会期望每个元素要花费14个周期或更长时间,因为这是L2的访问时间。但是结果表明,仅需要大约9个周期。可以通过处理器中的高级逻辑来解释这种差异。预期使用连续的内存区域,处理器会预取下一条缓存行。这意味着当实际使用下一行时,它已经中途加载。因此,等待下一个缓存行加载所需的延迟比L2访问时间小得多。

一旦工作集大小超过L2大小,预取的效果就更加明显。在我们说主存储器访问需要200多个周期之前。只有通过有效的预取,处理器才可以将访问时间保持在9个周期之内。从200与9之间的差异中可以看出,这很好地实现了。

我们可以至少在间接预取的同时观察处理器。在图3.11中,我们看到了相同工作集大小的时间,但是这次我们看到了结构l的不同大小的图表 。这意味着列表中的元素较少但较大。不同的大小会导致(仍然连续)列表中n个元素之间的距离增加。在图形的四种情况下,距离分别为0、56、120和248个字节。

在底部,我们可以看到上图的线,但是这次它或多或少显示为一条平线。其他情况的时间简直糟透了。我们也可以在该图中看到三个不同的级别,并且可以看到工作集大小较小的测试中存在较大的错误(再次忽略它们)。只要只涉及L1d,这些线或多或少都相互匹配。无需预取,因此所有元素大小每次访问都只需达到L1d。

对于L2缓存命中,我们看到三个新行几乎完全匹配,但是它们处于较高级别(大约28个)。这是L2的访问时间级别。这意味着从L2到L1d的预取基本上是禁用的。即使NPAD = 7,我们也需要为循环的每次迭代添加一条新的缓存行;对于 NPAD = 0,相反,循环必须迭代八次才需要下一个缓存行。预取逻辑无法在每个周期加载新的缓存行。因此,我们看到在每次迭代中都有从L2加载的停顿。

一旦工作集大小超过L2容量,它将变得更加有趣。现在,所有四行的差异很大。不同的元素大小显然在性能差异中起很大作用。处理器应识别步幅的大小,而不要为NPAD提取不必要的缓存行= 15和31,因为元素大小小于预取窗口(请参见6.3.1节)。元素大小妨碍预取工作的原因是硬件预取的限制:它不能跨越页面边界。每次增加大小,我们都会将硬件调度程序的有效性降低50%。如果允许硬件预取器跨越页面边界并且下一页不驻留或有效,则OS必须参与定位页面。这意味着程序将遇到未启动的页面错误。这是完全不可接受的,因为处理器不知道页面是否存在或不存在。在后一种情况下,操作系统将不得不中止该过程。无论如何,对于NPAD= 7或更高版本,每个列表元素需要一个缓存行,而硬件预取器不能做很多事情。根本没有时间从内存中加载数据,因为处理器的全部工作都是读取一个字,然后加载下一个元素。

速度下降的另一个重要原因是TLB缓存未命中。这是一个高速缓存,其中存储了虚拟地址到物理地址的转换结果,如第4节中所述。TLB高速缓存非常小,因为它必须非常快。如果重复访问的页面多于TLB缓存具有的条目,则必须不断重复进行从虚拟地址到物理地址的转换。这是非常昂贵的操作。对于较大的元素,将在较少的元素上分摊TLB查找的成本。这意味着必须为每个列表元素计算的TLB条目总数较高。

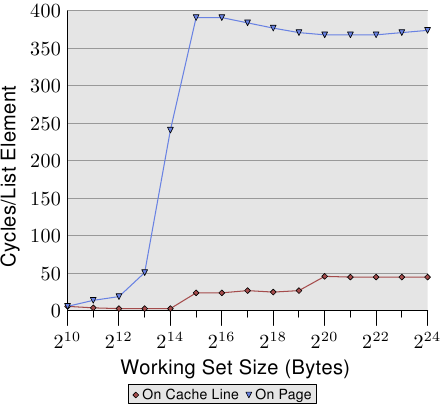

要观察TLB的影响,我们可以运行其他测试。对于一种测量,我们像往常一样顺序排列元素。对于占一整个缓存行的元素,我们使用 NPAD = 7。对于第二个度量,我们将每个列表元素放在单独的页面上。每页的其余部分保持不变,我们不将其计入工作集大小的总数中。{是的,这有点不一致,因为在其他测试中,我们在元素大小中计算结构的未使用部分,并且可以定义NPAD,以便每个元素填充一页。在这种情况下,工作集的大小将有很大的不同。但是,这并不是该测试的重点,而且由于预取仍然无效,因此差异不大。}结果是,对于第一次测量,每个列表迭代都需要一个新的缓存行,并且对于每64个元素,都需要一个新页面。对于第二次测量,每次迭代都需要加载新页面上的新缓存行。

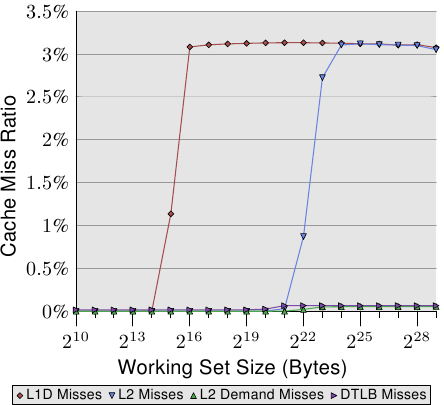

图3.12:TLB对顺序读取的影响

结果如图3.12所示。测量是在与图3.11相同的机器上进行的。由于可用RAM的限制,工作集大小必须限制为2 24字节,这需要1GB才能将对象放置在单独的页面上。下方的红色曲线恰好对应于图3.11中的 NPAD = 7曲线。我们看到了显示L1d和L2缓存大小的不同步骤。第二条曲线看起来截然不同。重要的功能是当工作台尺寸达到2 13时开始出现巨大的尖峰个字节。这是TLB缓存溢出时。使用64字节的元素大小,我们可以计算出TLB缓存具有64个条目。没有程序错误会影响成本,因为程序会锁定内存以防止其被换出。

可以看出,计算物理地址并将其存储在TLB中所需的周期数非常高。图3.12中的图形显示了极端情况,但现在应该清楚,对于较大的NPAD值,降低速度的一个重要因素是TLB缓存的效率降低。由于必须在可以读取L2或主存储器的高速缓存行之前计算物理地址,因此地址转换惩罚会增加存储器访问时间。这部分解释了为什么NPAD = 31时每个列表元素的总成本要比RAM的理论访问时间高。

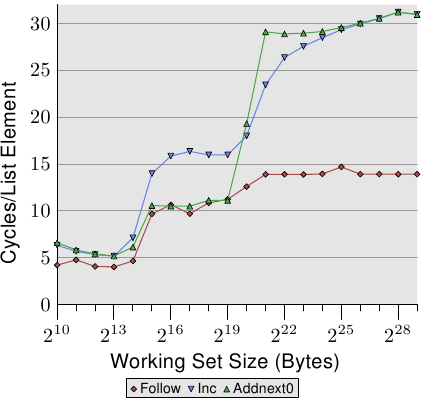

图3.13:顺序读写NPAD = 1

通过查看修改列表元素的测试运行的数据,我们可以瞥见预取实现的更多详细信息。图3.13显示了三行。元素宽度在所有情况下均为16个字节。第一行是现在熟悉的列表遍历,它是基准。第二行标记为“ Inc”,在继续进行下一个操作之前,仅增加当前元素的pad [0]成员。第三行标记为“ Addnext0”,将下一个元素的 pad [0]列表元素添加到当前列表元素的pad [0]成员中。

幼稚的假设是“ Addnext0”测试运行较慢,因为它需要做的工作更多。在前进到下一个列表元素之前,必须加载该元素中的值。这就是为什么令人惊讶的是,对于某些工作集大小,该测试实际上比“ Inc”测试运行得更快。对此的解释是,来自下一个列表元素的负载基本上是强制预取。只要程序前进到下一个列表元素,我们就可以确定该元素已经在L1d缓存中。结果,我们看到只要工作集大小适合L2缓存,“ Addnext0”的性能就和简单的“跟随”测试一样好。

不过,“ Addnext0”测试在L2中用完的速度比“ Inc”测试快。它需要从主存储器加载更多数据。这就是为什么“ Addnext0”测试在2个21字节的工作集大小下达到28个周期级别的原因。28个循环级别是“跟随”测试达到的14个循环级别的两倍。这也很容易解释。由于其他两个测试修改了内存,因此二级缓存逐出为新的缓存行腾出空间不能简单地丢弃数据。而是必须将其写入内存。这意味着FSB上的可用带宽减少了一半,因此将数据从主存储器传输到L2所需的时间加倍。

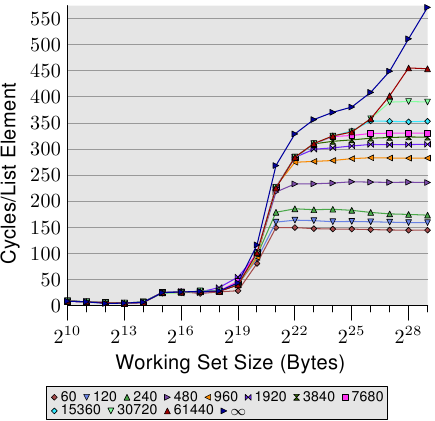

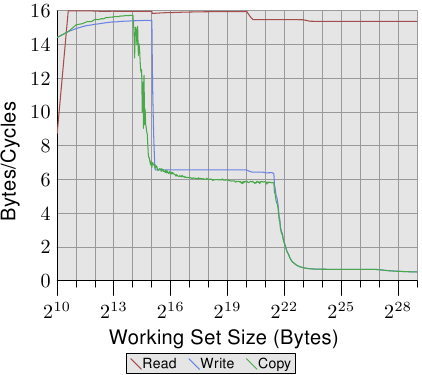

图3.14:更大的L2 / L3缓存的优势

顺序有效的缓存处理的最后一个方面是缓存的大小。这应该是显而易见的,但仍应指出。图3.14显示了具有128字节元素的增量基准测试的时序(在64位计算机上,NPAD = 15)。这次我们看到来自三台不同机器的测量结果。前两台机器是P4,最后一台是Core2处理器。前两个通过具有不同的缓存大小来区分自己。第一处理器具有32k L1d和1M L2。第二个具有16k L1d,512k L2和2M L3。Core2处理器具有32k L1d和4M L2。

图中有趣的部分不一定是Core2处理器相对于其他两个处理器的性能(尽管令人印象深刻)。这里的主要关注点是对于相应的最后一级缓存而言,工作集大小过大且主内存大量涉及的区域。

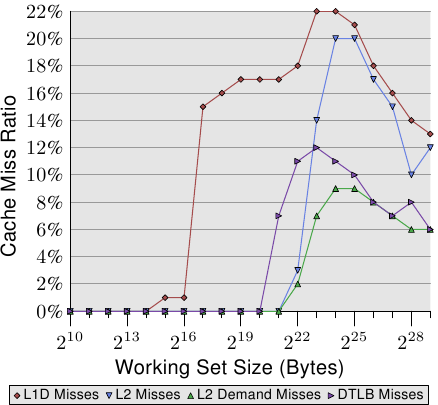

| 设定 尺寸 | 顺序的 | 随机 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| L2命中 | L2小姐 | #Iter | 丢失/击中率 | 每个迭代的L2访问 | L2命中 | L2小姐 | #Iter | 丢失/击中率 | 每个迭代的L2访问 | |

| 2 20 | 88,636 | 843 | 16,384 | 0.94% | 5.5 | 30,462 | 4721 | 1,024 | 13.42% | 34.4 |

| 2 21 | 88,105 | 1,584 | 8,192 | 1.77% | 10.9 | 21,817 | 15,151 | 512 | 40.98% | 72.2 |

| 2 22 | 88,106 | 1,600 | 4,096 | 1.78% | 21.9 | 22,258 | 22,285 | 256 | 50.03% | 174.0 |

| 2 23 | 88,104 | 1,614 | 2,048 | 1.80% | 43.8 | 27,521 | 26,274 | 128 | 48.84% | 420.3 |

| 2 24 | 88,114 | 1,655 | 1,024 | 1.84% | 87.7 | 33,166 | 29,115 | 64 | 46.75% | 973.1 |

| 2 25 | 88,112 | 1,730 | 512 | 1.93% | 175.5 | 39,858 | 32,360 | 32 | 44.81% | 2,256.8 |

| 2 26 | 88,112 | 1,906 | 256 | 2.12% | 351.6 | 48,539 | 38,151 | 16 | 44.01% | 5,418.1 |

| 2 27 | 88,114 | 2,244 | 128 | 2.48% | 705.9 | 62,423 | 52,049 | 8 | 45.47% | 14,309.0 |

| 2 28 | 88,120 | 2,939 | 64 | 3.23% | 1,422.8 | 81,906 | 87,167 | 4 | 51.56% | 42,268.3 |

| 2 29 | 88,137 | 4,318 | 32 | 4.67% | 2,889.2 | 119,079 | 163,398 | 2 | 57.84% | 141,238.5 |

表3.2:顺序游走和随机游走的L2命中和未命中,NPAD = 0

不出所料,最后一级缓存越大,曲线停留在与L2访问成本相对应的较低级别上的时间就越长。注意的重要部分是它提供的性能优势。第二个处理器(稍早一些)可以在2个20字节的工作集上执行工作,是第一个处理器的两倍。全部归功于末级缓存大小的增加。带有4M L2的Core2处理器性能更好。

对于随机的工作负载,这可能并不意味着那么多。但是,如果可以将工作负载调整为最后一级缓存的大小,则可以显着提高程序性能。这就是为什么有时值得花额外的钱购买具有更大缓存的处理器。

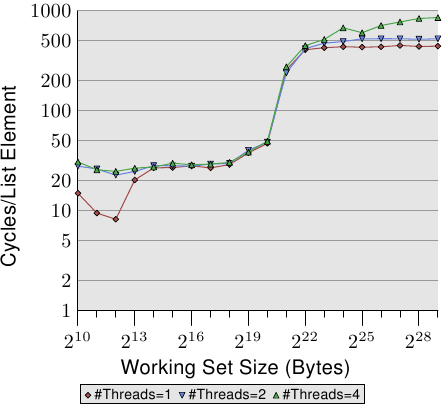

单线程随机访问测量

我们已经看到,通过将高速缓存行预取到L2和L1d中,处理器能够隐藏大多数主存储器甚至L2访问延迟。但是,只有在可预测的内存访问时,此方法才能很好地工作。

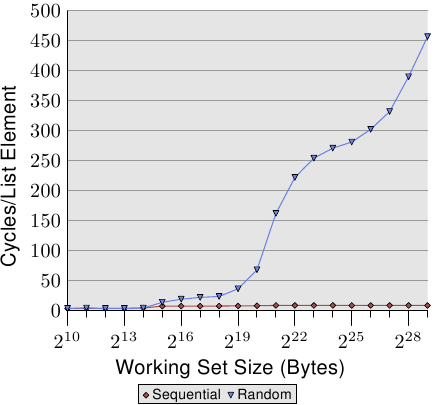

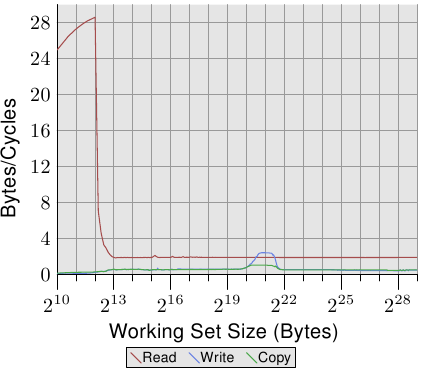

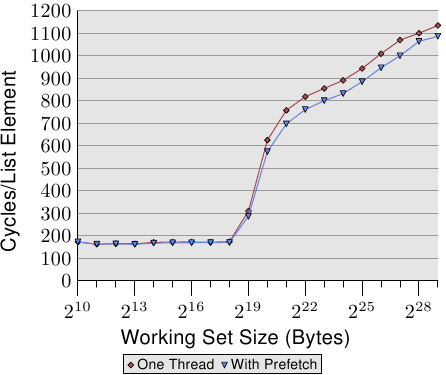

图3.15:顺序vs随机读取,NPAD = 0

如果访问是不可预测的或随机的,则情况会大不相同。图3.15比较了顺序访问的每个列表元素的时间(与图3.10相同)与列表元素在工作集中随机分布的时间。顺序由随机确定的链表确定。处理器无法可靠地预取数据。如果彼此之间不久使用的元素在内存中也彼此靠近,这只能是偶然的。

图3.15有两点需要注意。首先,大量是增加工作集大小所需的周期。这台机器可以在200-300个周期内访问主存储器,但在这里我们可以达到450个周期甚至更多。我们之前已经看到过这种现象(比较图3.11)。自动预取实际上在这里不利。

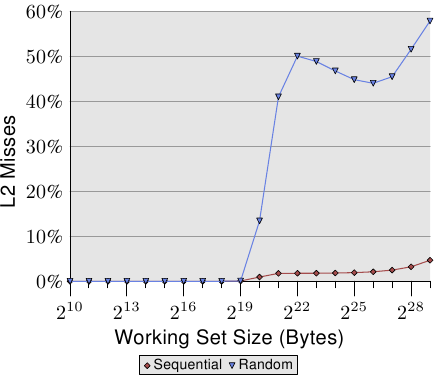

第二个有趣的点是,曲线在各个平稳阶段并没有变平,就像在顺序访问情况下一样。曲线不断上升。为了解释这一点,我们可以针对各种工作集大小来测量程序的L2访问。结果如图3.16和表3.2所示。

该图显示,当工作集大小大于L2大小时,缓存未命中率(L2未命中/ L2访问)开始增加。该曲线与图3.15中的曲线具有相似的形式:它迅速上升,略微下降并再次开始上升。与每个列表元素图的周期有很强的相关性。L2丢失率将一直增长,直到最终达到接近100%的水平。给定足够大的工作集(和RAM),可以任意降低任何随机选择的高速缓存行位于L2或正在加载的可能性。

仅增加的高速缓存未命中率就可以解释一些成本。但是还有另一个因素。查看表3.2,我们可以在L2 /#Iter列中看到该程序每次迭代使用的L2总数正在增长。每个工作集的大小是以前的两倍。因此,如果不进行缓存,我们期望主存储器访问量增加一倍。使用缓存和(几乎)完美的可预测性,我们看到数据中的L2使用量适度增加,用于顺序访问。该增加是由于工作集大小的增加而已。

图3.16:L2d丢失率

图3.17:页面明智随机化,NPAD = 7

对于随机访问,每增加一倍的工作集大小,每个元素的时间就会增加100%以上。这意味着每个列表元素的平均访问时间会增加,因为工作集的大小只会增加一倍。其背后的原因是TLB未命中率上升。在图3.17中,我们看到了NPAD随机访问的成本 = 7。仅这次,随机化才被修改。在正常情况下,将整个随机列表作为一个块(用标记∞表示),其他11条曲线则显示以较小块进行的随机化。对于标记为“ 60”的曲线,每组60页(245.760字节)分别被随机分配。这意味着在遍历下一个块中的元素之前,将遍历该块中的所有列表元素。这具有限制在任何一次使用的TLB条目数量的效果。

NPAD = 7 的元素大小为64字节,与缓存行大小相对应。由于列表元素的随机顺序,硬件预取器不太可能发挥作用,最肯定的是不会影响少数元素。这意味着L2高速缓存未命中率与一个块中整个列表的随机化没有显着差异。随着块大小的增加,测试的性能渐近地接近一块随机化的曲线。这意味着后一个测试用例的性能受到TLB遗漏的影响很大。如果可以降低TLB的未命中率,则性能将显着提高(在一项测试中,我们稍后将看到高达38%的信息)。

3.3.3写行为

在开始查看当多个执行上下文(线程或进程)使用同一内存时的缓存行为之前,我们必须探索缓存实现的详细信息。高速缓存应该是一致的,并且这种一致性对于用户级代码应该是完全透明的。内核代码是另一回事。有时需要刷新缓存。

这特别意味着,如果修改了缓存行,则在该时间点之后系统的结果与根本没有缓存并且主存储器位置本身已被修改的结果相同。这可以通过两种方式或策略来实现:

- 直写式缓存实现;

- 回写缓存实现。

直写式高速缓存是实现高速缓存一致性的最简单方法。如果写入了高速缓存行,则处理器也会立即将高速缓存行写入主内存。这样可以确保主存储器和缓存始终保持同步。只要替换缓存行,就可以简单地丢弃缓存内容。此缓存策略很简单,但不是很快。例如,一遍又一遍地修改局部变量的程序将在FSB上创建大量流量,即使该数据可能未在其他任何地方使用并且寿命很短。

回写策略更为复杂。在这里,处理器不会立即将修改后的高速缓存行写回到主存储器。而是,将缓存行仅标记为脏。当将来某个时候从缓存中删除缓存行时,脏位将指示处理器在那时写回数据,而不仅仅是丢弃内容。

回写式高速缓存有机会显着提高性能,这就是为什么具有良好处理器的系统中的大多数内存都以这种方式进行高速缓存的原因。处理器甚至可以利用FSB上的可用容量来存储必须排空的高速缓存行的内容。这样可以清除脏位,并且当需要缓存中的空间时,处理器可以删除缓存行。

但是回写实现存在一个重大问题。当有多个处理器(或核心或超线程)可用并访问相同的内存时,仍必须确保两个处理器始终都能看到相同的内存内容。如果一个处理器上的高速缓存行脏了(即尚未被写回),而第二个处理器试图读取相同的内存位置,则读取操作不能仅转到主内存。而是需要第一个处理器的缓存行的内容。在下一节中,我们将了解当前的实现方式。

在此之前,还有两个要提及的缓存策略:

- 写合并 和

- 无法缓存。

这两种策略都用于不由实际RAM支持的地址空间的特殊区域。内核为地址范围设置了这些策略(在x86处理器上使用内存类型范围寄存器MTRR),其余的自动发生。MTRR也可用于在直写和回写策略之间进行选择。

写合并是有限的缓存优化,更常用于图形卡等设备上的RAM。由于到设备的传输成本比本地RAM访问高得多,因此避免进行过多的传输就显得尤为重要。如果下一个操作修改了下一个字,那么仅因为写入了该行中的一个字而传输整个缓存行是浪费的。可以轻易想象这是一种普遍现象,在大多数情况下,屏幕上水平相邻像素的内存也是相邻的。顾名思义,写合并会在写出缓存行之前合并多个写访问。在理想情况下,整个缓存行逐字修改,只有在写入最后一个字之后,才将缓存行写入设备。这可以显着加快对设备上RAM的访问。

最后是不可缓存的内存。这通常意味着内存位置根本不受RAM支持。它可能是一个特殊的地址,该地址经过硬编码以在CPU外部具有某些功能。对于商用硬件,内存映射的地址范围通常是这种情况,它转换为对连接到总线(PCIe等)的卡和设备的访问。在嵌入式板上有时会找到这样的存储地址,该地址可用于打开和关闭LED。缓存这样的地址显然不是一个好主意。在这种情况下,LED用于调试或状态报告,因此希望尽快看到。PCIe卡上的内存可以在没有CPU交互的情况下进行更改,因此不应缓存此内存。

3.3.4多处理器支持

在上一节中,我们已经指出了多个处理器发挥作用时遇到的问题。对于那些不共享的缓存级别(至少是L1d),即使是多核处理器也存在问题。

提供从一个处理器到另一处理器的高速缓存的直接访问是完全不切实际的。刚开始时连接速度不够快。实际的选择是在需要时将缓存内容转移到另一个处理器。请注意,这也适用于不在同一处理器上共享的缓存。

现在的问题是,何时必须进行此高速缓存行传输?这个问题很容易回答:当一个处理器需要高速缓存行时,该高速缓存行在另一处理器的高速缓存中脏了以进行读取或写入。但是,处理器如何确定另一个处理器的缓存中的缓存行是否脏了?假定仅仅是因为高速缓存行由另一个处理器加载将是次优的(最好)。通常,大多数内存访问是读取访问,并且生成的高速缓存行不会变脏。高速缓存行上的处理器操作很频繁(当然,为什么还要写这篇论文?),这意味着在每次写访问之后广播有关已更改的高速缓存行的信息是不切实际的。

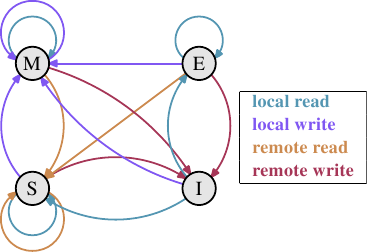

多年来开发的是MESI缓存一致性协议(已修改,互斥,共享,无效)。该协议以使用MESI协议时高速缓存行可以处于的四个状态命名:

- 已修改:本地处理器已修改高速缓存行。这也意味着它是任何缓存中的唯一副本。

- Exclusive(独占):缓存行未修改,但已知不会加载到任何其他处理器的缓存中。

- 共享:缓存行未修改,可能存在于另一个处理器的缓存中。

- 无效:缓存行无效,即未使用。

多年以来,该协议是从较简单的版本发展而来的,这些版本不那么复杂但也不太有效。通过这四个状态,可以有效地实现回写式高速缓存,同时还支持在不同处理器上并发使用只读数据。

图3.18:MESI协议转换

通过处理器侦听或监听其他处理器的工作,无需过多的工作即可完成状态更改。处理器执行的某些操作在外部引脚上宣告,从而使处理器的缓存处理对外部可见。所讨论的高速缓存行的地址在地址总线上可见。在以下状态及其转换的描述中(如图3.18所示),我们将指出何时涉及总线。

最初,所有缓存行都是空的,因此也是无效的。如果将数据加载到缓存中以进行写入,则缓存将更改为“已修改”。是否加载了数据以读取新状态取决于另一个处理器是否也加载了缓存行。如果是这种情况,则新状态为共享,否则为独占。

如果从本地处理器读取或写入了一条修改的高速缓存行,则指令可以使用当前的高速缓存内容,并且状态不会更改。如果第二个处理器要从缓存行中读取,则第一个处理器必须将其缓存的内容发送给第二个处理器,然后它才能将状态更改为“共享”。发送到第二处理器的数据也由将内容存储在存储器中的存储器控制器接收和处理。如果没有发生,则无法将缓存行标记为“共享”。如果第二处理器要写入高速缓存行,则第一处理器发送高速缓存行内容,并在本地将高速缓存行标记为无效。这是臭名昭著的“所有权请求”(RFO)操作。在上一级缓存中执行此操作,就像I→M转换相对昂贵一样。对于直写式缓存,我们还必须增加将新的缓存行内容写入下一个更高级别的缓存或主内存所需的时间,从而进一步增加了成本。

如果高速缓存行处于“共享”状态,并且本地处理器从中读取数据,则无需更改状态,并且可以从高速缓存中满足读取请求。如果将缓存行本地写入缓存行,也可以使用,但状态变为已修改。它还要求将其他处理器中缓存行的所有其他可能副本标记为无效。因此,必须通过RFO消息将写操作通知其他处理器。如果第二个处理器请求读取缓存行,则无需执行任何操作。主存储器包含当前数据,并且本地状态已共享。如果第二个处理器想要写入高速缓存行(RFO),则将高速缓存行简单标记为无效。无需总线操作。

独占状态几乎等于一个关键的区别共享状态:本地的写操作也没有必须要在总线上公布。已知本地缓存副本是唯一的副本。这可能是一个巨大的优势,因此处理器将尝试在“独占”状态而不是“共享”状态下保持尽可能多的缓存行。如果那一刻信息不可用,则后者是备用。还可以完全排除独占状态,而不会引起功能问题。由于E→M转换要比S→M转换快得多,因此只有性能会受到影响。

根据状态转换的描述,应该清楚多处理器操作所特有的成本在哪里。是的,填充缓存仍然很昂贵,但现在我们还必须注意RFO消息。每当必须发送这样的消息时,事情就会变慢。

在两种情况下,需要RFO消息:

- 线程从一个处理器迁移到另一个处理器,所有缓存行必须一次移到新处理器上。

- 在两个不同的处理器中确实需要高速缓存行。{在较小的级别上,同一处理器上的两个内核也是如此。成本略低。RFO消息可能会发送多次。}

在多线程或多进程程序中,总是需要同步。此同步是使用内存实现的。因此,存在一些有效的RFO消息。它们仍然必须保持尽可能少的频率。不过,还有其他来源的RFO消息。在第6节中,我们将解释这些情况。高速缓存一致性协议消息必须在系统的处理器之间分配。直到很明显,系统中的所有处理器都有机会回复该消息,MESI转换才能发生。这意味着答复可能花费的最长时间决定了一致性协议的速度。{这就是为什么我们今天看到例如带有三个插槽的AMD Opteron系统的原因。考虑到每个处理器只有三个超链接,而南桥连接则需要一个超链接,因此每个处理器都相距一跳。}总线上可能会发生冲突,在NUMA系统中延迟可能很高,当然,庞大的通信量也会减慢速度。所有充分的理由集中于避免不必要的流量。

还有一个以上的问题,涉及一个以上的处理器在运行。影响是高度特定于机器的,但原则上始终存在问题:FSB是共享资源。在大多数机器中,所有处理器都通过一条总线连接到内存控制器(请参见图2.1)。如果单个处理器可以使总线饱和(通常是这种情况),则共享同一总线的两个或四个处理器将限制每个处理器可用的带宽。

即使每个处理器都有自己的总线(如图2.2所示),也仍然有通向内存模块的总线。通常,这是一条总线,但是,即使在图2.2中的扩展模型中,对同一内存模块的并发访问也会限制带宽。

对于AMD模型,每个处理器可以具有本地内存也是如此。是的,所有处理器都可以快速并发访问其本地内存。但是多线程和多进程程序(至少有时会不时)必须访问相同的内存区域以进行同步。

并发受到可用于实现必要同步的有限带宽的严重限制。需要仔细设计程序,以最大程度地减少从不同处理器和内核对相同内存位置的访问。以下测量将显示此以及其他与多线程代码有关的缓存效果。

多线程测量

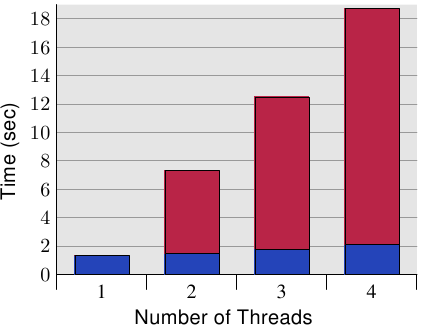

为了确保理解在不同处理器上同时使用相同的缓存行而引入的问题的严重性,我们将在此处查看以前使用的同一程序的更多性能图。但是,这一次,同时运行多个线程。测量的是所有线程中最快的运行时间。这意味着完成所有线程后完成运行的时间甚至更长。使用的机器有四个处理器;测试最多使用四个线程。所有处理器共用一条总线到内存控制器,而只有一条总线到内存模块。

图3.19:顺序读取访问,多线程

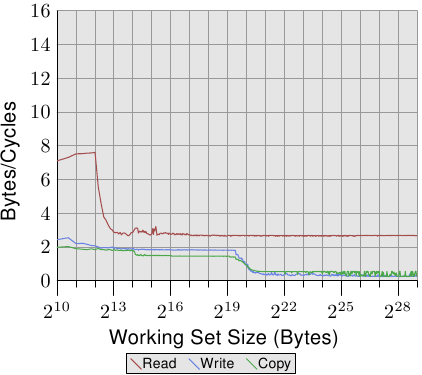

图3.19显示了128字节条目的顺序只读访问的性能(在64位计算机上,NPAD = 15)。对于一个线程的曲线,我们可以预期得到类似于图3.11的曲线。测量是针对另一台机器的,因此实际数字有所不同。

该图中的重要部分当然是运行多个线程时的行为。请注意,遍历链表时不会修改内存,也不会尝试使线程保持同步。即使不需要RFO消息并且可以共享所有缓存行,我们发现使用两个线程时最快的线程的性能下降最多18%,而使用四个线程时的性能下降高达34%。由于无需在处理器之间传输高速缓存行,因此,这种速度下降仅是由两个瓶颈之一或两者引起的:从处理器到内存控制器的共享总线,以及从内存控制器到内存模块的总线。一旦工作集大小大于此计算机中的L3缓存,所有三个线程将预取新的列表元素。

当我们修改内存时,事情变得更加难看。图3.20显示了顺序增量测试的结果。

图3.20:顺序递增,多线程

该图的Y轴使用对数刻度。因此,不要被表面上很小的差异所欺骗。运行两个线程仍然有18%的罚款,而运行四个线程现在却有93%的惊人罚款。这意味着当使用四个线程时,预取流量和回写流量会使总线大大饱和。

我们使用对数刻度显示L1d范围的结果。可以看到的是,一旦运行了多个线程,L1d基本上就失效了。仅当L1d不足以容纳工作集时,单线程访问时间才超过20个周期。当多个线程正在运行时,即使使用最小的工作集大小,这些访问时间也会立即达到。

问题的一方面未在此处显示。用这个特定的测试程序很难衡量。即使测试修改了内存,因此我们必须期待RFO消息,但是当使用多个线程时,我们不会看到L2范围的更高成本。该程序将不得不使用大量的内存,并且所有线程必须并行访问同一内存。如果没有大量的同步,那么这将很难实现,而这将占据执行时间。

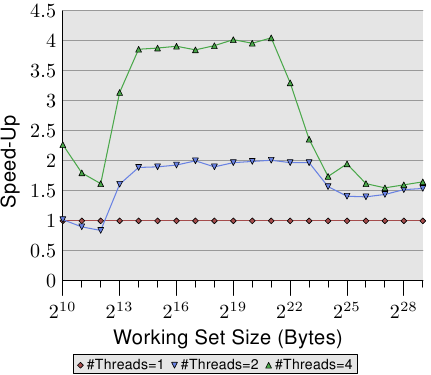

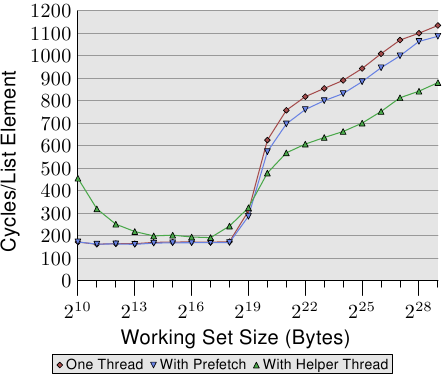

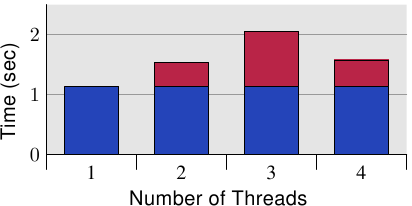

图3.21:随机Addnextlast,多线程

最后,在图3.21中,我们获得了具有随机访问内存的Addnextlast测试的编号。提供此数字主要是为了显示惊人的数字。在极端情况下,现在需要大约1,500个周期来处理单个列表元素。使用更多线程甚至更成问题。我们可以总结一个表中多线程使用的效率。

#线程 顺序读 赛克公司 兰德添加 2 1.69 1.69 1.54 4 2.98 2.07 1.65 表3.3:多线程效率

该表在图3.21的三个图中显示了最大工作集大小的多线程运行的效率。该数字表示通过使用两个或四个线程,对于最大的工作集大小,测试程序可能会以最快的速度进行加速。对于两个线程,理论上的加速极限为2,对于四个线程,其理论极限为4。两个线程的数量还不错。但是对于四个线程,最后一次测试的数字表明,超过两个线程几乎不值得。额外的好处是微不足道的。如果我们稍微不同地表示图3.21中的数据,就可以更容易地看到这一点。

图3.22:通过并行加速

图3.22中的曲线显示了加速因子,即与单线程执行的代码相比的相对性能。我们必须忽略最小的尺寸,测量不够准确。对于L2和L3缓存的范围,我们可以看到我们确实实现了几乎线性的加速。我们几乎分别达到2和4的系数。但是,一旦L3缓存不足以容纳工作集,数字就会崩溃。它们崩溃到两个线程和四个线程的加速相同的程度(请参阅表3.3的第四列)。这就是为什么几乎找不到具有四个以上都使用同一个内存控制器的CPU插槽的主板的原因之一。具有更多处理器的机器必须以不同的方式构建(请参阅第5节)。

这些数字不是通用的。在某些情况下,即使适合最后一级缓存的工作集也不允许线性加速。实际上,这是规范,因为线程通常不像该测试程序中那样解耦。另一方面,可以使用大型工作集,并且仍然可以利用两个以上的线程。但是,这样做需要思考。我们将在第6节中讨论一些方法。

特殊情况:超线程

超线程(有时称为对称多线程,SMT)由CPU实现,是一种特殊情况,因为各个线程不能真正同时运行。它们都共享几乎所有的处理资源(寄存器集除外)。各个内核和CPU仍可并行工作,但是每个内核上实现的线程都受到此限制的限制。从理论上讲,每个内核可以有很多线程,但是到目前为止,英特尔的CPU最多每个内核只有两个线程。CPU负责线程的时间复用。但是,仅此一点并没有多大意义。真正的优势在于,当当前运行的超线程延迟时,CPU可以调度另一个超线程。在大多数情况下,这是由内存访问引起的延迟。

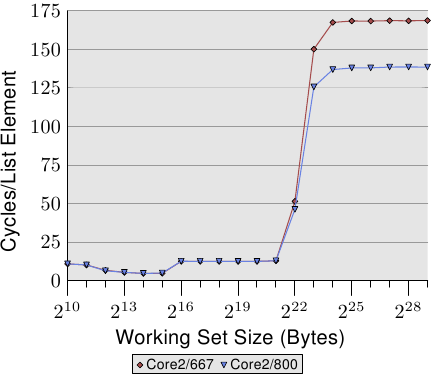

如果两个线程在一个超线程内核上运行,则当两个线程的组合运行时间低于单线程代码的运行时间时,该程序仅比单线程代码更有效 。通过重叠通常顺序发生的不同内存访问的等待时间,可以做到这一点。一个简单的计算显示了对高速缓存命中率的最低要求,以达到一定的速度。

程序的执行时间可以通过仅具有一级缓存的简单模型来估算,如下所示(请参见[htimpact]):

T exe = N [(1-F mem)T proc + F mem(G命中T缓存+(1-G命中)T miss)]

变量的含义如下:

ñ = 指令数。 ˚F MEM = 访问内存的N的分数。 G打 = 命中缓存的负载的分数。 Ť PROC = 每条指令的周期数。 T缓存 = 缓存命中的周期数。 Ť小姐 = 高速缓存未命中的周期数。 Ť EXE = 程序的执行时间。

为了使使用两个线程有意义,两个线程中每个线程的执行时间必须最多为单线程代码的一半。任一侧的唯一变量是高速缓存命中数。如果我们求解不使线程执行速度降低50%或更多所需的最小高速缓存命中率的等式,则会得到图3.23所示的图。

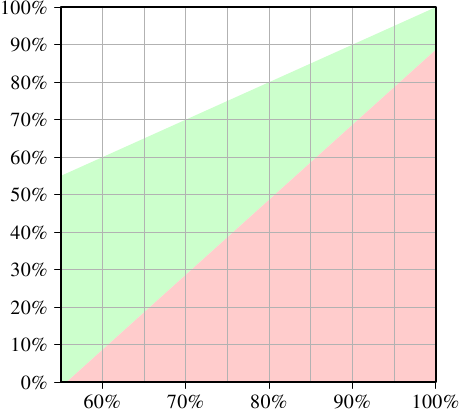

图3.23:加速时的最小高速缓存命中率

X轴表示单线程代码的缓存命中率G hit。Y轴显示了多线程代码所需的高速缓存命中率。该值永远不能高于单线程命中率,因为否则,单线程代码也将使用该改进的代码。对于低于55%的单线程命中率,程序在任何情况下都可以受益于使用线程。由于高速缓存未命中,CPU或多或少足够闲置,无法运行第二个超线程。

绿色区域是目标。如果线程的运行速度小于50%,并且每个线程的工作量减半,则合并的运行时可能少于单线程运行时。对于此处的建模系统(使用具有超线程的P4的数字),对于单线程代码,命中率为60%的程序对于双线程程序,命中率为至少10%。这通常是可行的。但是,如果单线程代码的命中率达到95%,那么多线程代码的命中率至少应达到80%。那更难。尤其是,这是超线程的问题,因为现在每个超线程可用的有效缓存大小(此处为L1d,实际上也为L2等等)减少了一半。两个超线程都使用相同的缓存来加载其数据。

因此,超线程仅在有限的情况下才有用。单线程代码的高速缓存命中率必须足够低,以使给定上述公式并减小高速缓存大小,新的命中率仍能达到目标。然后只有这样,使用超线程才有意义。在实践中,结果是否更快取决于处理器是否足以将一个线程中的等待时间与其他线程中的执行时间重叠。必须将代码并行化的开销添加到新的总运行时中,而这种额外的成本通常不能忽略。

在6.3.4节中,我们将看到一种技术,其中线程紧密协作,而通过公共缓存的紧密耦合实际上是一个优势。如果只有程序员愿意花时间和精力来扩展他们的代码,则该技术可以适用于许多情况。

应该清楚的是,如果两个超线程执行完全不同的代码(即,操作系统将两个线程视为单独的处理器来执行单独的进程),则缓存大小实际上减少了一半,这意味着缓存显着增加错过。除非缓存足够大,否则此类OS调度实践会令人怀疑。除非计算机的工作负载由通过其设计确实可以从超线程中受益的进程组成,否则最好关闭计算机BIOS中的超线程。{保持启用超线程的另一个原因是调试。SMT擅长在并行代码中发现一些问题。}

3.3.5其他详细信息

到目前为止,我们讨论的地址由三部分组成,即标签,设置索引和高速缓存行偏移量。但是实际使用什么地址?今天,所有相关的处理器都为进程提供虚拟地址空间,这意味着有两种不同的地址:虚拟和物理。

虚拟地址的问题在于它们不是唯一的。随着时间的推移,虚拟地址可以引用不同的物理内存地址。不同过程中的同一地址也可能是指不同的物理地址。因此,使用物理内存地址总是更好,对吧?

这里的问题是指令使用虚拟地址,并且这些虚拟地址必须在内存管理单元(MMU)的帮助下转换为物理地址。这是不平凡的操作。在执行指令的管道中,物理地址可能仅在以后的阶段可用。这意味着缓存逻辑必须非常快速地确定是否缓存了内存位置。如果可以使用虚拟地址,则可以在管道中更早地进行高速缓存查找,并且在高速缓存命中的情况下,可以使内存内容可用。结果是,管道可以隐藏更多的内存访问成本。

处理器设计者当前正在将虚拟地址标记用于第一级缓存。这些高速缓存很小,可以轻松清除。如果进程的页表树发生更改,则至少需要部分清除缓存。如果处理器具有指定已更改的虚拟地址范围的指令,则有可能避免完全刷新。鉴于L1i和L1d缓存的低延迟(〜3个周期),几乎必须使用虚拟地址。

对于较大的高速缓存,包括L2,L3,...,高速缓存需要物理地址标记。这些高速缓存具有更高的延迟,并且虚拟→物理地址转换可以及时完成。由于这些高速缓存较大(即,在清除高速缓存时会丢失大量信息),并且由于主内存访问延迟而重新填充高速缓存需要很长时间,因此刷新它们通常会很昂贵。

通常,没有必要知道这些缓存中地址处理的详细信息。它们无法更改,影响性能的所有因素通常都是应避免的或与高成本相关的事情。高速缓存容量的溢出很不好,如果大多数使用的高速缓存行属于同一组,则所有高速缓存都会尽早出现问题。使用虚拟寻址的缓存可以避免后者,但是对于用户级进程而言,避免使用物理地址寻址的缓存是不可能的。可能要记住的唯一细节是,如果可能的话,不要在同一过程中将同一物理内存位置映射到两个或多个虚拟地址。

缓存的另一个细节对程序员而言并不有趣,那就是缓存替换策略。大多数高速缓存会最先退出最近最少使用(LRU)元素。这始终是一个很好的默认策略。随着更大的关联性(由于增加了更多的核心,关联性的确在未来几年中可能会进一步增长),维护LRU列表变得越来越昂贵,我们可能会看到采用了不同的策略。

至于缓存的替换,程序员没有什么可以做的。如果高速缓存正在使用物理地址标签,则无法找出虚拟地址如何与高速缓存集相关联。可能所有逻辑页中的缓存行都映射到相同的缓存集,而许多缓存未使用。如果有的话,操作系统的工作就是安排这种情况不经常发生。

随着虚拟化技术的出现,事情变得更加复杂。现在,甚至连操作系统都无法控制物理内存的分配。虚拟机监视器(VMM,又名虚拟机管理程序)负责物理内存分配。

程序员可以做的最好的事情是:a)完全使用逻辑存储器页面,b)使用尽可能有意义的页面大小来尽可能地分散物理地址。页面大小也有其他好处,但这是另一个主题(请参见第4节)。

3.4指令缓存

不仅缓存了处理器使用的数据,还缓存了数据。由处理器执行的指令也被缓存。但是,此缓存比数据缓存的问题要少得多。有以下几个原因:

- 执行的代码量取决于所需代码的大小。通常,代码的大小取决于问题的复杂性。问题的复杂性是固定的。

- 尽管程序的数据处理是由程序员设计的,但程序的指令通常是由编译器生成的。编译器作者了解良好代码生成的规则。

- 程序流比数据访问模式更可预测。当今的CPU非常擅长检测模式。这有助于预取。

- 代码始终具有相当好的空间和时间局部性。

程序员应遵循一些规则,但是这些规则主要由有关如何使用工具的规则组成。我们将在第6节中讨论它们。在这里,我们仅讨论指令高速缓存的技术细节。

自从CPU的核心时钟急剧增加,并且高速缓存(甚至是一级高速缓存)和核心之间的速度差异不断增大以来,CPU一直在流水线化。这意味着一条指令的执行分阶段进行。首先解码一条指令,然后准备参数,最后执行它。这样的流水线可能会很长(对于Intel的Netburst架构,> 20个阶段)。较长的流水线意味着,如果流水线停滞(即,流经该流水线的指令流被中断),则需要一段时间才能恢复速度。例如,如果无法正确预测下一条指令的位置或加载下一条指令所需的时间太长(例如,当必须从内存中读取时),则会发生管道停顿。

结果,CPU设计人员在分支预测上花费了大量时间和芯片资源,从而尽可能少地发生管道停顿。

在CISC处理器上,解码阶段也可能需要一些时间。x86和x86-64处理器尤其受影响。因此,近年来,这些处理器不在L1i中缓存指令的原始字节序列,而是缓存已解码的指令。在这种情况下,L1i被称为“跟踪缓存”。跟踪高速缓存允许处理器在发生高速缓存命中的情况下跳过流水线的第一步,如果流水线停滞,则特别好。

如前所述,从L2开始的缓存是包含代码和数据的统一缓存。显然,这里的代码以字节序列形式缓存,并且不被解码。

为了获得最佳性能,只有少数与指令缓存相关的规则:

- 生成尽可能小的代码。当出于使用管道的原因而进行软件流水处理需要创建更多代码或使用小代码的开销过高时,会有例外。

- 只要有可能,请帮助处理器做出良好的预取决策。这可以通过代码布局或显式预取来完成。

这些规则通常由编译器的代码生成来实施。程序员可以做一些事情,我们将在第6节中讨论它们。

3.4.1自我修改代码

在早期的计算机时代,记忆是一种溢价。人们竭尽全力减小程序的大小,以便为程序数据腾出更多空间。经常部署的一个技巧是随着时间的推移更改程序本身。有时仍会发现这种自修改代码(SMC),主要是出于性能方面的原因或出于安全漏洞的考虑。

通常应避免使用SMC。尽管通常可以正确执行它,但在某些情况下并不能正确执行,如果执行不正确,则会造成性能问题。显然,更改后的代码无法保存在包含已解码指令的跟踪缓存中。但是,即使由于根本未执行代码(或一段时间未执行)而未使用跟踪缓存,处理器也可能会出现问题。如果即将到来的指令已经进入管道而被更改,则处理器必须放弃很多工作并重新开始。甚至在某些情况下,处理器的大多数状态都必须放弃。

最后,由于处理器(出于简单性的原因,并且因为在所有情况下99.9999999%的情况都是如此)假定代码页是不可变的,因此L1i实现不使用MESI协议,而是使用简化的SI协议。这意味着,如果检测到修改,则必须做出很多悲观的假设。

强烈建议尽可能避免使用SMC。内存不再是一种稀缺资源。最好编写单独的函数,而不是根据特定需要修改一个函数。也许有一天可以将SMC支持设为可选,并且我们可以检测到试图以这种方式修改代码的漏洞利用代码。如果绝对必须使用SMC,则写操作应绕过缓存,以免对L1i中所需的L1d中的数据造成问题。有关这些说明的更多信息,请参见第6.1节。

通常在Linux上,很容易识别包含SMC的程序。使用常规工具链构建时,所有程序代码均具有写保护。程序员必须在链接时执行大量的魔术操作,以创建代码页可写的可执行文件。发生这种情况时,现代的Intel x86和x86-64处理器具有专用的性能计数器,该计数器可对自修改代码的使用进行计数。在这些计数器的帮助下,即使程序由于宽松的权限而成功执行,也很容易用SMC识别程序。

3.5缓存缺失因素

我们已经看到,当内存访问错过高速缓存时,成本将飞涨。有时这是无法避免的,重要的是要了解实际成本以及可以采取哪些措施来缓解该问题。

3.5.1缓存和内存带宽

为了更好地了解处理器的功能,我们测量了最佳情况下可用的带宽。由于不同的处理器版本差异很大,因此这种测量特别有趣。这就是为什么此部分填充了几台不同机器的数据的原因。衡量性能的程序使用x86和x86-64处理器的SSE指令一次加载或存储16个字节。就像在其他测试中一样,工作集从1kB增加到512MB,并测量了每个周期可以加载或存储多少字节。

图3.24:Pentium 4带宽

图3.24显示了64位Intel Netburst处理器的性能。对于适合L1d的工作集大小,处理器能够每个周期读取完整的16个字节,即,每个周期执行一条加载指令(movaps指令一次移动16个字节)。该测试对读取的数据没有任何作用,我们仅测试读取的指令本身。一旦L1d不再足够,性能就会急剧下降到每个周期少于6个字节。步骤2 18字节是由于DTLB缓存的耗尽而导致的,这意味着每个新页面都要进行额外的工作。由于读取是顺序的,因此预取可以完美地预测访问,并且对于所有大小的工作集,FSB可以以每个周期大约5.3字节的速度流传输内存内容。不过,预取的数据不会传播到L1d中。这些当然是在实际程序中永远无法实现的数字。将它们视为实际限制。

比读取性能更惊人的是写入和复制性能。即使对于较小的工作集大小,写入性能也永远不会超过每个周期4个字节。这表明,在这些Netburst处理器中,英特尔选择对L1d使用直写模式,而性能显然受到L2速度的限制。这也意味着从一个内存区域复制到第二个非重叠内存区域的复制测试的性能不会显着变差。必要的读取操作非常快,并且可能与写入操作部分重叠。一旦L2缓存不再足够,写入和复制测量的最值得注意的细节就是性能低下。性能下降到每个周期0.5个字节!这意味着写操作要比读操作慢十倍。这意味着优化这些操作对于程序的性能甚至更为重要。

在图3.25中,我们看到了在同一处理器上运行两个线程的结果,一个线程固定在处理器的两个超线程中的每个线程上。

图3.25:具有2个超线程的P4带宽

该图以与前一个相同的比例显示,以说明差异,并且曲线仅由于测量两个并发线程的问题而有些抖动。结果是预期的。由于超线程共享除寄存器之外的所有资源,因此每个线程仅具有可用缓存和带宽的一半。这意味着即使每个线程都需要等待很多时间并且可以在执行时间上授予另一个线程,但这没有任何区别,因为另一个线程也必须等待内存。这确实显示了超线程的最坏使用。

图3.26:核心2带宽

与图3.24和3.25相比,图3.26和3.27的结果对于英特尔酷睿2处理器而言有很大不同。这是一个共享L2的双核处理器,它是P4机器上L2的四倍。但是,这仅解释了写入和复制性能的延迟下降。

有更大的差异。在整个工作集范围内的读取性能在每个周期的最佳16字节左右徘徊。2 20字节后读取性能的下降再次是由于工作集对于DTLB而言太大。实现这些高数量意味着处理器不仅能够预取数据并及时传输数据。这也意味着数据已预取到L1d中。

写入和复制性能也大不相同。处理器没有直写策略;写入的数据存储在L1d中,仅在必要时驱逐。这样可以使写入速度接近每个周期的最佳16字节。一旦L1d不再足够,性能就会大大下降。与Netburst处理器一样,写入性能明显较低。由于具有较高的读取性能,因此此处的差异更大。实际上,即使L2不再足够,速度差也会增加20倍!这并不意味着Core 2处理器性能不佳。相反,它们的性能始终优于Netburst核心。

图3.27:具有2个线程的Core 2带宽

在图3.27中,测试运行两个线程,分别在Core 2处理器的两个内核中的每个内核上运行。但是,两个线程都访问相同的内存,但不一定完全同步。读取性能的结果与单线程情况没有区别。在任何多线程测试用例中,还会看到一些抖动。

有趣的一点是适合L1d的工作集大小的写入和复制性能。从图中可以看出,性能与必须从主存储器读取数据的性能相同。两个线程争夺相同的内存位置,并且必须发送用于缓存行的RFO消息。有问题的是,即使两个内核共享高速缓存,也无法以L2高速缓存的速度处理这些请求。一旦L1d缓存不足,就将修改后的条目从每个内核的L1d刷新到共享L2中。到那时,性能显着提高,因为现在L2高速缓存可以满足L1d丢失,并且仅在尚未刷新数据时才需要RFO消息。这就是为什么我们看到这些尺寸的工作集速度降低了50%的原因。

由于一个供应商的处理器版本之间存在显着差异,因此当然值得一提其他供应商的处理器的性能。图3.28显示了AMD系列10h Opteron处理器的性能。该处理器具有64kB L1d,512kB L2和2MB L3。L3缓存在处理器的所有内核之间共享。性能测试的结果如图3.28所示。

图3.28:AMD系列10h Opteron带宽

关于数字的第一个细节是,如果L1d高速缓存足够,则处理器能够在每个周期处理两条指令。每个周期的读取性能超过32个字节,甚至每个周期18.7字节的写入性能也很高。但是,读取曲线迅速变平,每个周期只有2.3个字节,非常低。此测试的处理器不会预取任何数据,至少不会有效。

另一方面,写入曲线根据各种高速缓存的大小执行。对于L1d的完整大小,可以达到最高性能,L2的每个周期降低到6个字节,L3的每个周期降低到2.8个字节,如果L3不能容纳所有数据,则最终每个周期只有0.5个字节。L1d缓存的性能超过(旧)Core 2处理器的性能,L2访问同样快(Core 2具有更大的缓存),并且L3和主内存访问更慢。

复制性能不能优于读取或写入性能。这就是为什么我们看到曲线最初由读取性能主导,然后由写入性能主导的原因。

Opteron处理器的多线程性能如图3.29所示。

图3.29:带2个线程的AMD Fam 10h带宽

读取性能在很大程度上不受影响。每个线程的L1d和L2都像以前一样工作,在这种情况下,L3缓存也无法很好地预取。这两个线程不会对L3施加过大的压力。此测试中的最大问题是写入性能。线程共享的所有数据都必须通过L3缓存。这种共享似乎效率很低,因为即使L3高速缓存大小足以容纳整个工作集,其成本也明显高于L3访问。通过将该图与图3.27进行比较,我们可以看到,在适当的工作集大小范围内,Core 2处理器的两个线程以共享L2缓存的速度运行。仅在很小的工作范围内,Opteron处理器才能达到这种性能水平 仅L3的速度比Core 2的L2慢。

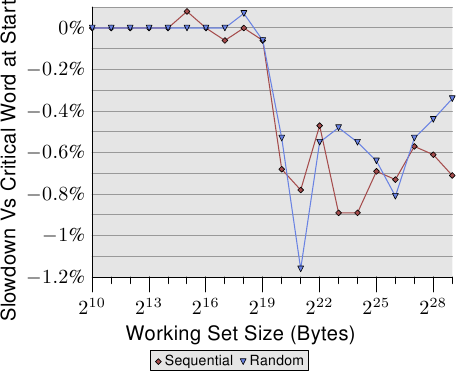

3.5.2关键单词加载

内存以小于缓存行大小的块形式从主内存传输到缓存中。今天,一次传输64位,并且缓存行大小为64或128字节。这意味着每条高速缓存行需要进行8或16次传输。

DRAM芯片可以突发模式传输这些64位块。这可以填充高速缓存行,而无需来自存储控制器的任何其他命令以及可能的相关延迟。如果处理器预取高速缓存行,则这可能是最佳的操作方式。

如果程序对数据的高速缓存访问或指令高速缓存未命中(这意味着这是强制性高速缓存未命中,因为数据是第一次使用,或者是容量高速缓存未命中,因为有限的高速缓存大小需要逐出高速缓存行)情况有所不同。程序继续执行所需的高速缓存行中的单词可能不是高速缓存行中的第一个单词。即使在突发模式下,并且具有双倍数据速率传输,各个64位块的到达时间也明显不同。每个块比上一个延迟到达4个CPU周期或更晚。如果程序需要继续的字是高速缓存行的第八行,则程序必须在第一个字到达后再等待30个或更多个周期。

事情不一定必须是这样。存储器控制器可以自由请求以不同顺序的高速缓存行的字。处理器可以传达程序正在等待哪个单词, 关键单词,并且存储控制器可以首先请求该单词。一旦字到达,程序就可以继续,而其余的高速缓存行到达并且高速缓存尚未处于一致状态。此技术称为“关键单词优先和早期重启”。

当今的处理器实现了这种技术,但是在某些情况下这是不可能的。如果处理器预取数据,则未知单词。如果处理器在预取操作进行期间请求高速缓存行,则它必须等到关键字到达后才能影响顺序。

图3.30:缓存行末尾的关键字

即使进行了这些优化,关键字在高速缓存行上的位置也很重要。图3.30显示了顺序访问和随机访问的跟踪测试。显示的是使用在第一个单词中追逐指针的指针运行测试的速度与在最后一个单词中指针的情况相比变慢。元素大小为64个字节,对应于缓存行大小。这些数字非常嘈杂,但是可以看出,一旦L2不足以容纳工作集大小,关键单词最后的情况下的性能就会降低大约0.7%。顺序访问似乎受到的影响更大。当预取下一个缓存行时,这将与上述问题一致。

3.5.3缓存放置

与超线程,内核和处理器相关的缓存位置不受程序员的控制。但是程序员可以确定在哪里执行线程,然后缓存与已使用的CPU之间的关系就变得很重要。

这里我们将不讨论何时选择运行线程的核心。我们将仅描述架构师在设置线程的亲和力时必须考虑的架构细节。

根据定义,超线程共享除寄存器集以外的所有内容。这包括L1缓存。这里没有更多要说的了。乐趣始于处理器的各个核心。每个内核至少具有自己的L1缓存。除此之外,今天没有太多共同之处:

- 早期的多核处理器具有单独的L2缓存,没有更高的缓存。

- 后来的英特尔机型共享了双核处理器的二级缓存。对于四核处理器,我们必须为两个内核的每对分别处理单独的二级缓存。没有更高级别的缓存。

- AMD的10h系列处理器具有单独的L2缓存和统一的L3缓存。

在处理器供应商的宣传材料中已经写了很多有关其各自型号优势的文章。如果内核处理的工作集不重叠,则单独的L2缓存具有优势。这对于单线程程序非常有效。由于今天仍然经常发生这种情况,因此这种方法的效果并不差。但是总会有一些重叠。缓存都包含公共运行时库中使用最频繁的部分,这意味着浪费了一些缓存空间。

像英特尔的双核处理器一样,完全共享L1之外的所有缓存可以具有很大的优势。如果在两个内核上工作的线程的工作集明显重叠,则总可用高速缓存将增加,并且工作集可以更大而不会降低性能。如果工作集不重叠,那么英特尔的高级智能缓存管理应该可以防止任何一个内核独占整个缓存。

但是,如果两个内核将大约一半的缓存用于其各自的工作集,则会产生一些摩擦。缓存必须不断权衡两个内核的缓存使用情况,而作为这种重新平衡的一部分而执行的逐出可能会选择得很差。为了查看问题,我们看了另一个测试程序的结果。

图3.31:具有两个进程的带宽

测试程序具有一个过程,该过程使用SSE指令不断读取或写入2MB的内存块。之所以选择2MB,是因为它是该Core 2处理器的L2缓存的一半。该进程固定到一个核心,而第二个进程固定到另一个核心。第二个过程读取和写入大小可变的存储区域。该图显示了每个周期读取或写入的字节数。显示了四个不同的图形,每个图形分别用于读写过程。读/写图用于后台进程,该进程始终使用2MB的工作集进行写操作,而使用可变工作组的被测进程则进行读取。

图中有趣的部分是2 20和2 23字节之间的部分。如果两个内核的L2缓存完全分开,我们可以预期所有四个测试的性能将在2 21和2 22之间下降。字节,这意味着L2缓存一旦耗尽。如图3.31所示,情况并非如此。对于后台进程正在编写的情况,这是最明显的。在工作集大小达到1MB之前,性能开始下降。这两个进程不共享内存,因此这些进程不会导致生成RFO消息。这些是纯粹的缓存逐出问题。智能缓存处理存在以下问题,即每个可用核心的高速缓存大小比每个可用核心2MB的缓存更接近1MB。只能希望,如果内核之间共享的高速缓存仍然是即将到来的处理器的功能,那么用于智能高速缓存处理的算法将是固定的。

在引入更高级别的缓存之前,拥有带有两个L2缓存的四核处理器只是一个权宜之计。与单独的插槽和双核处理器相比,该设计没有明显的性能优势。两个内核通过同一总线进行通信,该总线在外部显示为FSB。没有特殊的快速通道数据交换。

多核处理器的缓存设计的未来将位于更多的层。AMD的10h处理器家族起步。我们是否将继续看到较低级别的高速缓存由处理器核心的子集共享,还有待观察。高速缓存和频繁使用的高速缓存无法在许多内核之间共享,因此需要额外的高速缓存级别。性能将受到影响。它还将需要具有高关联性的超大型缓存。高速缓存大小和关联性这两个数字都必须随共享高速缓存的核心数成比例。使用大型L3缓存和合理大小的L2缓存是一个合理的权衡。L3高速缓存较慢,但理想情况下不如L2高速缓存使用得那么频繁。

对于程序员而言,所有这些不同的设计都意味着制定计划决策时的复杂性。必须了解工作负载和机器体系结构的详细信息才能获得最佳性能。幸运的是,我们有支持来确定机器体系结构。这些接口将在后面的部分中介绍。

3.5.4 FSB影响

FSB在机器性能中起着核心作用。缓存内容只能在与内存的连接允许的情况下尽快存储和加载。我们可以通过在两台机器上运行一个程序来显示出多少,这两个机器的内存模块的速度只是不同。图3.32显示了在64位计算机上NPAD = 7时Addnext0测试的结果(将下一个元素pad [0]元素的内容添加到自己的pad [0]元素中) 。这两台机器都具有Intel Core 2处理器,第一台使用667MHz DDR2模块,第二台使用800MHz模块(增加了20%)。

图3.32:FSB速度的影响

数据显示,当FSB真正承受大型工作台尺寸的压力时,我们的确受益匪浅。此测试中测得的最大性能提升为18.2%,接近理论最大值。这表明,更快的FSB确实可以节省大量时间。工作集是否适合高速缓存(这些处理器具有4MB的L2)并不重要。必须记住,我们正在这里测量一个程序。系统的工作集包括所有同时运行的进程所需的内存。这样,使用较小的程序很容易超过4MB内存。

今天,某些英特尔处理器支持FSB速度高达1,333MHz,这意味着将再增加60%。未来将看到更高的速度。如果速度很重要并且工作集大小更大,那么快速的RAM和较高的FSB速度无疑是值得的。但是,必须谨慎,因为即使处理器可能支持更高的FSB速度,主板/北桥也可能不支持。检查规格至关重要。

内存部分3:虚拟内存

4个虚拟内存

处理器的虚拟内存子系统实现提供给每个进程的虚拟地址空间。这使每个进程都认为它在系统中是单独存在的。虚拟内存的优点列表将在其他地方详细介绍,因此在此不再赘述。相反,本节着重于虚拟内存子系统的实际实现细节以及相关的成本。

虚拟地址空间由CPU的内存管理单元(MMU)实现。操作系统必须填写页表数据结构,但是大多数CPU自己完成其余工作。这实际上是一个非常复杂的机制。理解它的最好方法是介绍用于描述虚拟地址空间的数据结构。

MMU执行的地址转换输入是虚拟地址。通常,对其价值的限制很少(如果有的话)。虚拟地址在32位系统上是32位值,在64位系统上是64位值。在某些系统上,例如x86和x86-64,所使用的地址实际上涉及另一个间接级别:这些体系结构使用段,这些段仅导致将偏移量添加到每个逻辑地址。我们可以忽略地址生成的这一部分,它是微不足道的,而不是程序员在内存处理性能方面必须关心的部分。{ x86上的细分限制与性能相关,但这是另一回事。}

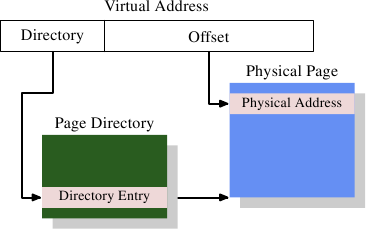

4.1最简单的地址转换

有趣的部分是虚拟地址到物理地址的转换。MMU可以逐页重新映射地址。正如寻址高速缓存行时一样,虚拟地址也分为不同的部分。这些部分用于索引各种表,这些表用于构建最终物理地址。对于最简单的模型,我们只有一层表。

图4.1:1级地址转换

图4.1显示了如何使用虚拟地址的不同部分。顶部用于选择页面目录中的条目;操作系统可以单独设置该目录中的每个条目。页面目录条目确定物理内存页面的地址;页面目录中的多个条目可以指向相同的物理地址。通过将页面目录中的页面地址与虚拟地址中的低位组合在一起,可以确定存储单元的完整物理地址。页面目录条目还包含有关页面的一些其他信息,例如访问权限。

页面目录的数据结构存储在内存中。操作系统必须分配连续的物理内存,并将该内存区域的基地址存储在特殊寄存器中。然后,将虚拟地址的适当位用作页面目录的索引,该目录实际上是目录条目的数组。

举一个具体的例子,这是用于x86机器上4MB页面的布局。虚拟地址的偏移量部分为22位,足以寻址4MB页中的每个字节。虚拟地址的其余10位选择页面目录中的1024个条目之一。每个条目包含一个4MB页面的10位基址,该地址与偏移量结合在一起形成一个完整的32位地址。

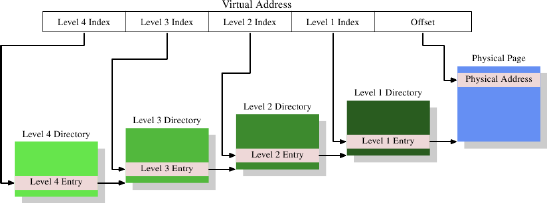

4.2多层页表

4MB页面不是常态,它们会浪费大量内存,因为OS必须执行的许多操作都需要与内存页面对齐。对于4kB页(32位计算机上的规范,并且仍然经常在64位计算机上使用),虚拟地址的Offset部分的大小仅为12位。这留下20位作为页面目录的选择器。具有2 20个条目的表是不实际的。即使每个条目只有4个字节,表的大小也将是4MB。由于每个进程可能具有其自己的不同页面目录,因此系统的许多物理内存将被这些页面目录占用。

解决方案是使用多个级别的页表。然后,它们可以代表一个稀疏的大页面目录,其中未实际使用的区域不需要分配的内存。因此,表示形式更加紧凑,可以在内存中使用许多进程的页表,而不会对性能造成太大影响。

今天,最复杂的页表结构包含四个级别。图4.2显示了这种实现的示意图。

图4.2:4级地址转换

在此示例中,虚拟地址被分为至少五个部分。其中四个部分是各个目录的索引。使用CPU中的专用寄存器来引用4级目录。4级到2级目录的内容是对下一个较低目录的引用。如果目录条目标记为空,则显然不需要指向任何较低的目录。这样,页面表树可以稀疏而紧凑。如图4.1所示,级别1目录的条目是部分物理地址,以及诸如访问权限之类的辅助数据。

为了确定对应于虚拟地址的物理地址,处理器首先确定最高级别目录的地址。该地址通常存储在寄存器中。然后,CPU获取与该目录相对应的虚拟地址的索引部分,并使用该索引来选择适当的条目。此项是下一个目录的地址,该目录使用虚拟地址的下一部分进行索引。此过程一直进行到到达1级目录为止,此时目录条目的值是物理地址的高位。通过添加虚拟地址中的页面偏移位来完成物理地址。此过程称为页面树漫游。一些处理器(例如x86和x86-64)在硬件中执行此操作,其他处理器则需要操作系统的帮助。

系统上运行的每个进程可能都需要自己的页表树。可以部分共享树,但这是一个例外。因此,如果页表树所需的内存尽可能小,则对性能和可伸缩性都有好处。理想的情况是将使用的内存在虚拟地址空间中放置在一起。实际使用的物理地址无关紧要。一个小型程序可能只需要在2、3和4级别的每个目录中使用一个目录,以及几个1级目录。在具有4kB页和每个目录512个条目的x86-64上,这允许寻址2MB的地址,总共有4个目录(每个级别一个)。1GB的连续内存可以使用一个目录访问2至4级,使用512个目录访问1级。

但是,假设所有内存都可以连续分配太简单了。出于灵活性的考虑,在大多数情况下,进程的堆栈和堆区域分配在地址空间的相对两端。如果需要,这可以使任何一个区域尽可能多地增长。这意味着最有可能需要两个2级目录,并相应地有更多的较低级目录。

但是,即使这样也不总是符合当前的做法。出于安全原因,可执行文件的各个部分(代码,数据,堆,堆栈,DSO,aka共享库)都映射在随机地址[nonselsec]。随机化扩展到各个部分的相对位置。这意味着在一个进程中使用的各种内存区域遍布整个虚拟地址空间。通过对随机化的地址位数施加一些限制,可以限制范围,但是可以肯定的是,在大多数情况下,对于第2级和第3级,进程只允许一个或两个目录运行。

如果性能确实比安全性重要得多,则可以关闭随机化。然后,操作系统通常通常至少将所有DSO连续加载到虚拟内存中。

4.3优化页表访问

页表的所有数据结构都保存在主存储器中;这是OS构造和更新表的地方。创建过程或更改页表后,将通知CPU。页表用于使用上述页表遍历将每个虚拟地址解析为物理地址。更重要的是:在解析虚拟地址的过程中,每个级别至少使用一个目录。这需要多达四个内存访问(对于正在运行的进程的单个访问),这很慢。可以将这些目录表条目视为普通数据,并将其缓存在L1d,L2等中,但这仍然太慢了。

从虚拟内存的早期开始,CPU设计人员就使用了不同的优化方法。一个简单的计算可以表明,仅将目录表条目保留在L1d和更高级别的缓存中将导致可怕的性能。每次绝对地址计算将需要对应于页表深度的多个L1d访问。这些访问不能并行化,因为它们取决于前一个查询的结果。在具有四个页表级别的计算机上,仅此一项就至少需要12个周期。加上L1d未命中的可能性,结果是指令流水线无法隐藏的结果。附加的L1d访问也将宝贵的带宽窃取到缓存。

因此,不仅可以缓存目录表条目,还可以缓存对物理页面地址的完整计算。出于代码和数据缓存起作用的相同原因,这种缓存的地址计算是有效的。由于虚拟地址的页面偏移部分在物理页面地址的计算中不起作用,因此仅将虚拟地址的其余部分用作缓存的标签。根据页面大小,这意味着成百上千的指令或数据对象共享相同的标签,因此也共享相同的物理地址前缀。

计算值存储在其中的缓存称为转换后备缓冲区(TLB)。它通常是一个很小的缓存,因为它必须非常快。就像其他高速缓存一样,现代CPU提供了多级TLB高速缓存。较高级别的缓存更大且更慢。L1TLB的小尺寸通常是通过使高速缓存与LRU逐出策略完全关联来弥补的。最近,此高速缓存的大小不断增长,并且在此过程中已更改为设置为关联的。因此,无论何时必须添加新条目,它都可能不是被驱逐并替换的最旧条目。

如上所述,用于访问TLB的标签是虚拟地址的一部分。如果标签在高速缓存中具有匹配项,则通过将虚拟地址的页面偏移量与高速缓存的值相加来计算最终的物理地址。这是一个非常快速的过程。之所以必须这样做,是因为对于使用绝对地址的每条指令,物理地址必须是可用的;在某些情况下,对于使用 物理地址作为键的L2查找,物理地址必须是可用 的。如果TLB查找未命中,则处理器必须执行页表遍历;这可能会非常昂贵。

如果地址在另一页上,则通过软件或硬件预取代码或数据可以隐式预取TLB的条目。硬件预取不能这样做,因为硬件可能会启动无效的页表遍历。因此,程序员无法依靠硬件预取来预取TLB条目。必须使用预取指令明确地完成此操作。就像数据和指令缓存一样,TLB可以出现在多个级别中。就像数据缓存一样,TLB通常以两种形式出现:一条指令TLB(ITLB)和一条数据TLB(DTLB)。像L2TLB这样的高层TLB通常是统一的,其他缓存也是如此。

4.3.1使用TLB的注意事项

TLB是处理器核心的全局资源。在处理器内核上执行的所有线程和进程都使用相同的TLB。由于虚拟地址到物理地址的转换取决于安装的页面表树,因此如果更改了页面表,则CPU无法盲目地重用缓存的条目。每个进程都有一个与内核和VMM(管理程序)(如果存在)不同的页表树(但不是同一进程中的线程)。进程的地址空间布局也可能会更改。有两种方法可以解决此问题:

- 每当更改页表树时,都会刷新TLB。

- TLB条目的标签被扩展以额外且唯一地标识它们引用的页表树。

在第一种情况下,只要执行上下文切换,就会刷新TLB。因为在大多数操作系统中,从一个线程/进程切换到另一个线程/进程需要执行一些内核代码,所以TLB刷新仅限于进入和离开内核地址空间。在虚拟化系统上,当内核必须调用VMM并返回时也会发生这种情况。如果内核和/或VMM不必使用虚拟地址,或者可以重用与进行系统/ VMM调用的进程或内核相同的虚拟地址,则仅在离开内核或VMM时才需要刷新TLB。 ,处理器将恢复执行其他进程或内核。

冲洗TLB是有效的,但价格昂贵。例如,在执行系统调用时,内核代码可能仅限于数千条指令,这些指令可能会触及几个新页面(或一个巨大的页面,在某些体系结构上就是Linux的情况)。这项工作将仅替换与触摸页面一样多的TLB条目。对于具有128条ITLB和256条DTLB条目的Intel Core2架构,完全刷新将意味着不必要地刷新了100多个和200个条目(分别)。当系统调用返回到相同的进程时,所有已刷新的TLB条目都可以再次使用,但它们将消失。对于内核或VMM中的常用代码也是如此。即使内核和VMM的页表通常不更改,在每次进入内核时,TLB也必须从头开始填充,并且 因此,从理论上讲,TLB条目可以保存很长时间。这也解释了为什么今天的处理器中的TLB缓存不更大:为什么程序很可能不会运行足够长的时间来填充所有这些条目。

当然,这一事实并没有使CPU架构师幸免。优化缓存刷新的一种可能性是单独使TLB条目无效。例如,如果内核代码和数据属于特定的地址范围,则仅必须将属于该地址范围的页面从TLB中逐出。这仅需要比较标签,因此不是很昂贵。如果部分地址空间发生更改(例如,通过调用munmap),此方法也很有用。

更好的解决方案是扩展用于TLB访问的标签。如果除了虚拟地址的一部分之外,还为每个页表树添加了唯一的标识符(即,进程的地址空间),则根本不必完全清除TLB。内核,VMM和各个进程都可以具有唯一的标识符。该方案的唯一问题是可用于TLB标签的位数受到严格限制,而地址空间的数目却没有受到限制。这意味着必须重复使用一些标识符。发生这种情况时,必须对TLB进行部分冲洗(如果可能的话)。所有带有重用标识符的条目都必须清除,但是希望这是一个更小的集合。

当系统上运行多个进程时,这种扩展的TLB标记具有一般优势。如果每个可运行进程的内存使用(以及由此产生的TLB条目使用)受到限制,则当再次调度该进程时,该进程最近使用的TLB条目很有可能仍位于TLB中。但是还有另外两个优点:

- 特殊的地址空间(例如内核和VMM使用的地址空间)通常只输入很短的时间。之后,控制权通常返回到发起呼叫的地址空间。没有标签,将执行两次TLB刷新。使用标记,将保留调用地址空间的缓存转换,并且由于内核和VMM地址空间根本不经常更改TLB条目,因此仍可以使用来自先前系统调用等的转换。

- 在同一进程的两个线程之间切换时,根本不需要进行TLB刷新。但是,如果没有扩展的TLB标签,进入内核的条目将破坏第一个线程的TLB条目。

某些处理器已经实现了一些扩展标签。AMD在Pacifica虚拟化扩展中引入了1位标签扩展。在虚拟化的上下文中,此1位地址空间ID(ASID)用于将VMM的地址空间与来宾域的地址空间区分开。这样,操作系统就可以避免每次输入VMM(例如,处理页面错误)或在控制权返回给来宾时VMM的TLB条目时都刷新来宾的TLB条目。该架构将允许将来使用更多位。其他主流处理器可能也会效仿并支持此功能。

4.3.2影响TLB性能

有几个因素会影响TLB的性能。第一个是页面的大小。显然,页面越大,越多的指令或数据对象将适合该页面。因此,较大的页面大小会减少所需的地址转换的总数,这意味着TLB缓存中需要的条目较少。大多数体系结构允许使用多种不同的页面大小。某些尺寸可以同时使用。例如,x86 / x86-64处理器的正常页面大小为4kB,但它们也可以分别使用4MB和2MB页面。IA-64和PowerPC允许将64kB之类的大小作为基本页面大小。

但是,使用大页面会带来一些问题。用于大页的内存区域在物理内存中必须是连续的。如果将用于管理物理内存的单位大小增加到虚拟内存页面的大小,则浪费的内存量将增加。各种内存操作(如加载可执行文件)都需要对齐页面边界。平均而言,这意味着每个映射都会浪费物理内存中每个映射的页面大小的一半。这种浪费很容易累加起来。因此,它为物理内存分配的合理单位大小设置了上限。

将单元大小增加到2MB以容纳x86-64上的大页面当然是不切实际的。大小太大。但这又意味着每个大页面必须由许多较小的页面组成。这些小页面在物理内存中必须是连续的 。分配2MB的连续物理内存(单位页面大小为4kB)可能很困难。它需要找到一个具有512个连续页面的空闲区域。在系统运行一段时间并且物理内存碎片化之后,这可能非常困难(或不可能)。

因此,在Linux上,有必要使用特殊的hugetlbfs文件系统在系统启动时预先分配这些大页面。保留一定数量的物理页面,以供大型虚拟页面专用。这限制了可能不总是使用的资源。这也是一个有限的池;增加它通常意味着重新启动系统。不过,在性能非常重要,资源充足且设置麻烦的情况下,较大的页面仍然是行之有效的方法。数据库服务器就是一个例子。

增加最小虚拟页面大小(与可选的大页面相对)也有其问题。内存映射操作(例如,加载应用程序)必须符合这些页面大小。不可能有更小的映射。对于大多数体系结构,可执行文件各个部分的位置具有固定的关系。如果页面大小增加到超出构建可执行文件或DSO时考虑的范围,则无法执行加载操作。记住此限制很重要。图4.3显示了如何确定ELF二进制文件的对齐要求。它被编码在ELF程序标头中。

$ eu-readelf -l / bin / ls 程序标题: 类型偏移VirtAddr PhysAddr FileSiz MemSiz Flg对齐 ... 负载0x000000 0x0000000000400000 0x0000000000400000 0x0132ac 0x0132ac RE 0x200000 负载0x0132b0 0x00000000006132b0 0x00000000006132b0 0x001a71 0x001a71 RW 0x200000 ...

图4.3:ELF程序标头指示对齐要求

在此示例中,为x86-64二进制,值是0x200000 = 2,097,152 = 2MB,它对应于处理器支持的最大页面大小。

使用较大页面大小的第二个效果是:页面表树的级别数减少了。由于虚拟地址中与页面偏移量相对应的部分增加了,因此剩下的比特数很少,需要通过页面目录进行处理。这意味着,在TLB丢失的情况下,必须完成的工作量减少了。

除了使用大页面大小之外,还可以通过将同时使用的数据移动到更少的页面来减少所需的TLB条目数。这类似于我们上面讨论的一些针对缓存使用的优化。只是现在所需的对齐方式很大。鉴于TLB条目的数量非常少,这可能是一个重要的优化。

4.4虚拟化的影响

OS映像的虚拟化将越来越普遍。这意味着将另一层内存处理添加到图片中。进程(基本上是监狱)或OS容器的虚拟化不属于此类,因为仅涉及一个OS。Xen或KVM之类的技术(无论有无处理器帮助)都可以执行独立的OS映像。在这些情况下,只有一个软件可以直接控制对物理内存的访问。

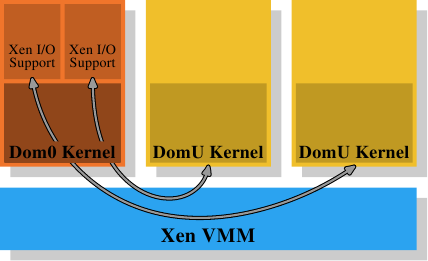

图4.4:Xen虚拟化模型

对于Xen(参见图4.4),Xen VMM是该软件。但是,VMM本身并未实现许多其他硬件控件。与其他早期系统(以及Xen VMM的第一个版本)上的VMM不同,内存和处理器之外的硬件由特权Dom0域控制。当前,该内核与非特权DomU内核基本上是同一内核,就内存处理而言,它们没有区别。在此重要的是,VMM将物理内存分发给Dom0和DomU内核,而Dom0和DomU内核本身将实现通常的内存处理,就好像它们直接在处理器上运行一样。

为了实现完成虚拟化所需的域的分离,Dom0和DomU内核中的内存处理不能不受限制地访问物理内存。VMM不会通过发出单独的物理页面并让来宾OS处理寻址来分发内存。这将无法为故障域或恶意来宾域提供任何保护。相反,VMM为每个来宾域创建自己的页表树,并使用这些数据结构分发内存。好处是,可以控制对页表树的管理信息的访问。如果代码没有适当的特权,它将无法执行任何操作。

Xen提供的虚拟化技术都利用了这种访问控制,无论使用了半虚拟化还是硬件虚拟化(也称为完整虚拟化)。来宾域为每个进程构造其页表树,其方式对于参数虚拟化和硬件虚拟化而言非常相似。每当访客OS修改其页表时,都会调用VMM。然后,VMM使用来宾域中的更新信息来更新其自己的影子页表。这些是硬件实际使用的页表。显然,此过程非常昂贵:对页面表树的每次修改都需要调用VMM。如果没有虚拟化,对内存映射的更改并不便宜,但现在它们变得更加昂贵。

考虑到从来宾OS到VMM以及自身的更改已经非常昂贵,因此额外的费用可能确实很大。这就是为什么处理器开始具有其他功能以避免创建影子页表的原因。这不仅好于速度方面的考虑,而且还可以减少VMM的内存消耗。英特尔具有扩展页表(EPT),而AMD称其为嵌套页表(NPT)。基本上,这两种技术都使来宾OS的页表产生虚拟物理地址。然后必须使用每个域的EPT / NPT树将这些地址进一步转换为实际的物理地址。这将允许以几乎非虚拟化情况的速度进行内存处理,因为已删除了大多数用于内存处理的VMM条目。

附加地址转换步骤的结果也存储在TLB中。这意味着TLB不存储虚拟物理地址,而是存储完整的查找结果。已经解释了AMD的Pacifica扩展引入了ASID,以避免在每个条目上进行TLB刷新。在处理器扩展的初始发行版中,ASID的位数为1。这足以区分VMM和来宾OS。英特尔具有用于相同目的的虚拟处理器ID(VPID),但其中有更多。但是VPID对于每个来宾域都是固定的,因此不能用于标记单独的进程,也不能避免在该级别进行TLB刷新。

每次地址空间修改所需的工作量是虚拟化OS的一个问题。但是,基于VMM的虚拟化还存在另一个固有的问题:无法围绕两层内存处理。但是内存处理很困难(尤其是考虑到诸如NUMA之类的复杂性时,请参见第5节)。Xen使用单独的VMM的方法使最佳处理(或什至是好的处理)变得困难,因为必须在VMM中复制内存管理实现的所有复杂性,包括发现内存区域等“琐碎”的事情。操作系统具有完善和优化的实现;一个人真的想避免重复它们。

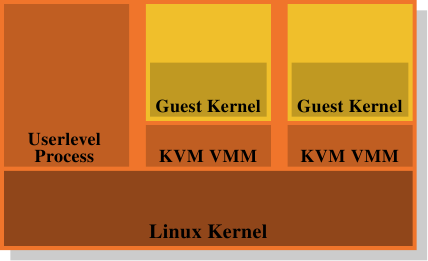

图4.5:KVM虚拟化模型

这就是为什么将VMM / Dom0模型作为结论如此诱人的原因。图4.5显示了KVM Linux内核扩展如何尝试解决该问题。没有单独的VMM直接在硬件上运行并控制所有guest虚拟机。相反,普通的Linux内核将接管此功能。这意味着Linux内核中完整而复杂的内存处理功能用于管理系统的内存。来宾域在创建者称为“来宾模式”的情况下与正常的用户级过程一起运行。虚拟化功能(部分或完全虚拟化)由另一个用户级别的流程KVM VMM控制。这只是另一个使用内核实现的特殊KVM设备控制来宾域的过程。

与使用Xen模型的单独VMM相比,该模型的优势在于,即使使用来宾OS时仍有两个内存处理程序在工作,但仅需要一个实现(在Linux内核中)。不必在另一段代码(例如Xen VMM)中复制相同的功能。这导致更少的工作,更少的错误,并且可能减少两个内存处理程序接触的摩擦,因为Linux guest虚拟机中的内存处理程序做出的假设与在裸机上运行的外部Linux内核中的内存处理程序相同。

总体而言,程序员必须意识到,使用虚拟化后,内存操作的成本甚至比没有虚拟化时还要高。任何减少这项工作的优化将在虚拟化环境中带来更大的回报。随着时间的流逝,处理器设计人员将通过EPT和NPT之类的技术越来越减少这种差异,但是它永远不会消失。

内存第4部分:NUMA支持

5 NUMA支持

在第2节中,我们看到,在某些计算机上,对物理内存特定区域的访问成本取决于访问的来源。此类硬件需要操作系统和应用程序特别注意。我们将从NUMA硬件的一些细节开始,然后我们将介绍Linux内核为NUMA提供的一些支持。

5.1 NUMA硬件

不统一的存储体系结构变得越来越普遍。在NUMA的最简单形式中,处理器可以具有本地内存(请参见图2.3),该内存比其他处理器本地的内存便宜。这种类型的NUMA系统的成本差异不高,即NUMA系数很低。

NUMA尤其是在大型机器中也使用。我们已经描述了让许多处理器访问同一内存的问题。对于商用硬件,所有处理器都将共享同一北桥(目前忽略AMD Opteron NUMA节点,它们有自己的问题)。这使得北桥成为一个严重的瓶颈,因为所有内存流量都通过北桥进行 路由。大型计算机当然可以使用自定义硬件代替北桥,但是,除非所用的存储芯片具有多个端口(即可以从多个总线使用它们),否则仍然存在瓶颈。多端口RAM的构建和支持非常复杂且昂贵,因此,几乎从未使用过。

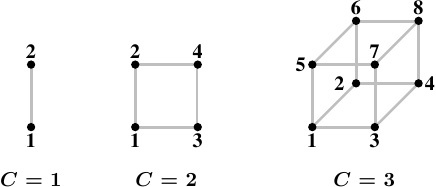

复杂性的下一步是AMD使用的模型,其中互连机制(在AMD的情况下为超传输,他们从Digital获得许可的技术)可为未直接连接到RAM的处理器提供访问权限。除非人们想要任意增加直径(即,任意两个节点之间的最大距离),否则可以以这种方式形成的结构的尺寸受到限制。

图5.1:超立方体

超级多维数据集是节点的有效拓扑,它可以将节点数限制为2 C,其中C是每个节点具有的互连接口数。对于拥有2 n个CPU的所有系统,超立方体的直径最小。图5.1显示了前三个超立方体。每个超立方体的直径C为绝对最小值。AMD第一代Opteron处理器每个处理器具有三个超传输链接。至少一个处理器必须具有连接到一个链路的南桥,这意味着当前可以直接和有效地实现C = 2的超立方体。宣布下一代具有四个链接,此时C = 3 超立方体将是可能的。

但是,这并不意味着不能支持更大的处理器累积量。有些公司已经开发了交叉开关,可以使用更大的处理器集(例如,Newisys的Horus)。但是这些交叉开关增加了NUMA因子,并且在一定数量的处理器上不再有效。

下一步意味着连接CPU组并为所有CPU实现一个共享内存。所有这些系统都需要专门的硬件,绝不是商品系统。这样的设计存在多个复杂程度。仍然非常接近商用机器的系统是IBM x445和类似机器。可以购买带有x86和x86-64处理器的普通4U,8路机器。然后,可以将其中两台计算机(有时最多四台)连接起来,作为具有共享内存的单台计算机工作。所使用的互连引入了重要的NUMA因素,操作系统以及应用程序都必须考虑这一因素。

另一方面,像SGI的Altix这样的机器是专门为互连而设计的。SGI的NUMAlink互连结构非常快且延迟低。这两个都是高性能计算(HPC)的要求,尤其是在使用消息传递接口(MPI)时。缺点当然是,这种复杂性和专业性非常昂贵。它们使NUMA因子相当低,但由于这些计算机可以具有的CPU数量(数千个)和互连能力有限,因此NUMA因子实际上是动态的,根据工作负载可以达到不可接受的水平。

更常用的解决方案是使用高速网络连接商用机器集群。但是,这些不是NUMA机器。它们不实现共享地址空间,因此不属于此处讨论的任何类别。

5.2对NUMA的操作系统支持

为了支持NUMA计算机,操作系统必须考虑内存的分布式性质。例如,如果某个进程在给定的处理器上运行,则分配给该进程的地址空间的物理RAM应该来自本地内存。否则,每个指令都必须访问远程存储器以获取代码和数据。需要考虑的特殊情况仅在NUMA机器中存在。DSO的文本段通常在机器的物理RAM中仅存在一次。但是,如果所有CPU上的进程和线程都使用DSO(例如,基本运行时库,如libc),这意味着除少数处理器外,所有其他处理器都必须具有远程访问权限。理想情况下,操作系统会将此类DSO“镜像”到每个处理器的物理RAM中并使用本地副本。这是一种优化,而不是要求,通常很难实现。它可能不受支持或仅受限制。

为避免使情况变得更糟,操作系统不应将进程或线程从一个节点迁移到另一个节点。操作系统应该已经尝试避免在普通的多处理器计算机上迁移进程,因为从一个处理器迁移到另一个处理器意味着缓存内容丢失。如果负载分配需要从处理器迁移进程或线程,则OS通常可以选择具有足够容量的任意新处理器。在NUMA环境中,新处理器的选择受到更多限制。新选择的处理器对进程正在使用的内存的访问成本不应比旧处理器高。这限制了目标列表。如果没有符合该标准的免费处理器,则操作系统别无选择,只能迁移到内存访问成本更高的处理器。

在这种情况下,有两种可能的解决方法。首先,我们可以希望情况是暂时的,并且可以将过程迁移回更适合的处理器。另外,操作系统还可以将进程的内存迁移到更接近新使用的处理器的物理页面。这是相当昂贵的操作。可能必须复制大量内存,尽管不一定要一步一步。在这种情况下,至少必须短暂停止该过程,以便正确迁移对旧页面的修改。为了使页面迁移高效,快速,还列出了其他要求。简而言之,除非确实必要,否则操作系统应避免使用它。

通常,不能假定NUMA机器上的所有进程都使用相同数量的内存,这样,随着处理器之间进程的分布,内存使用也将平均分布。实际上,除非在计算机上运行的应用程序非常具体(在HPC世界中很常见,但在外部不是),否则内存使用将非常不平等。一些应用程序将使用大量的内存,而其他应用程序几乎不会使用。如果始终向发出请求的处理器本地分配内存,则迟早会导致问题。系统最终将耗尽运行大型进程的节点的本地内存。

为了应对这些严重问题,默认情况下,内存不是专门在本地节点上分配的。要利用系统的所有内存,默认策略是分拆内存。这样可以保证平等使用系统的所有内存。副作用是,由于平均而言,对所使用的所有内存的访问成本不会改变,因此可以在处理器之间自由迁移进程。对于较小的NUMA因数,条带化是可以接受的,但仍不是最佳选择(请参见5.4节中的数据)。

这是一种悲观化,有助于系统避免严重问题并使其在正常操作下更可预测。但是,在某些情况下,它确实会降低整体系统性能。这就是Linux允许每个进程选择内存分配规则的原因。流程可以为其自身及其子级选择不同的策略。我们将在第6节中介绍可用于此的接口。

5.3发布信息

内核通过sys伪文件系统(sysfs)发布有关以下处理器缓存的信息

/ sys / devices / system / cpu / cpu * / cache

在6.2.1节中,我们将看到可用于查询各种缓存大小的接口。这里重要的是缓存的拓扑。上面的目录包含子目录(名为index *),这些子目录列出了有关CPU拥有的各种缓存的信息。 就拓扑而言,文件类型,level和shared_cpu_map是这些目录中的重要文件。对于Intel Core 2 QX6700,信息如表5.1所示。

类型 水平 shared_cpu_map cpu0 索引0 数据 1个 00000001 索引1 指令 1个 00000001 索引2 统一 2 00000003 cpu1 索引0 数据 1个 00000002 索引1 指令 1个 00000002 索引2 统一 2 00000003 cpu2 索引0 数据 1个 00000004 索引1 指令 1个 00000004 索引2 统一 2 0000000c cpu3 索引0 数据 1个 00000008 索引1 指令 1个 00000008 索引2 统一 2 0000000c 表5.1:Core 2 CPU缓存的sysfs信息

该数据的含义如下:

- 每个核心{关于cpu0到cpu3 是核心的知识来自另一个地方,我们将在后面简要说明。}具有三个缓存:L1i,L1d,L2。

- L1d和L1i高速缓存不与任何人共享-每个核心都有自己的高速缓存集。这由shared_cpu_map中的位图仅具有一个设置位来指示。

- 共享cpu0和cpu1上的L2缓存,以及cpu2和cpu3上的L2 。

如果CPU具有更多的缓存级别,则将有更多的index * 目录。

对于四插槽双核皓龙计算机,缓存信息如下表5.2所示:

类型 水平 shared_cpu_map cpu0 索引0 数据 1个 00000001 索引1 指令 1个 00000001 索引2 统一 2 00000001 cpu1 索引0 数据 1个 00000002 索引1 指令 1个 00000002 索引2 统一 2 00000002 cpu2 索引0 数据 1个 00000004 索引1 指令 1个 00000004 索引2 统一 2 00000004 cpu3 索引0 数据 1个 00000008 索引1 指令 1个 00000008 索引2 统一 2 00000008 cpu4 索引0 数据 1个 00000010 索引1 指令 1个 00000010 索引2 统一 2 00000010 cpu5 索引0 数据 1个 00000020 索引1 指令 1个 00000020 索引2 统一 2 00000020 cpu6 索引0 数据 1个 00000040 索引1 指令 1个 00000040 索引2 统一 2 00000040 cpu7 索引0 数据 1个 00000080 索引1 指令 1个 00000080 索引2 统一 2 00000080 表5.2:Opteron CPU缓存的sysfs信息

可以看出,这些处理器还具有三个缓存:L1i,L1d,L2。没有一个内核共享任何级别的缓存。该系统有趣的部分是处理器拓扑。没有这些附加信息,就无法理解缓存数据。该SYS文件系统暴露在下面的文件信息

/ sys / devices / system / cpu / cpu * /拓扑

表5.3显示了此层次结构中SMP Opteron机器的有趣文件。

physical_

package_idcore_id core_

兄弟姐妹thread_

兄弟姐妹cpu0 0 0 00000003 00000001 cpu1 1个 00000003 00000002 cpu2 1个 0 0000000c 00000004 cpu3 1个 0000000c 00000008 cpu4 2 0 00000030 00000010 cpu5 1个 00000030 00000020 cpu6 3 0 000000c0 00000040 cpu7 1个 000000c0 00000080 表5.3:Opteron CPU拓扑的sysfs信息

将表5.2和表5.3放在一起,我们可以看到没有CPU具有超线程(thread_siblings 位图设置了一位),系统实际上有四个处理器(physical_package_id 0到3),每个处理器有两个核,并且没有一个内核共享任何缓存。这恰好与早期的Opteron相对应。

到目前为止提供的数据中完全缺少的是有关此计算机上NUMA性质的信息。任何SMP Opteron机器都是NUMA机器。对于此数据,我们必须查看NUMA计算机上存在的sys文件系统的另一部分,即下面的层次结构

/ sys / devices / system / node

该目录包含系统上每个NUMA节点的子目录。在特定于节点的目录中,有许多文件。表5.4中显示了前两个表中描述的Opteron机器的重要文件及其内容。

cpumap 距离 节点0 00000003 10 20 20 20 节点1 0000000c 20 10 20 20 节点2 00000030 20 20 10 20 节点3 000000c0 20 20 20 10 表5.4:Opteron节点的sysfs信息

此信息将其余所有内容联系在一起;现在,我们对机器的架构有了完整的了解。我们已经知道该机器具有四个处理器。从node *目录中cpumap文件中的 值中设置的位可以看出,每个处理器都构成自己的节点。这些目录中的距离文件包含一组值,每个节点一个,代表各个节点上的内存访问成本。在此示例中,所有本地内存访问的成本均为10,对任何其他节点的所有远程访问的成本均为20。{顺便说一句,这是不正确的。ACPI信息显然是错误的,因为尽管所使用的处理器具有三个相关的HyperTransport链接,但至少一个处理器必须连接到南桥。因此,至少一对节点必须具有更大的距离。}这意味着,即使处理器被组织为二维超立方体(请参见图5.1),未直接连接的处理器之间的访问也不是那么昂贵。成本的相对值应该可用作访问时间实际差异的估计。所有这些信息的准确性是另一个问题。

5.4远程访问成本

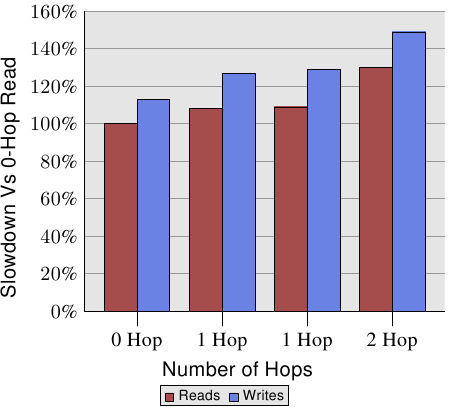

距离是相关的。AMD在[amdccnuma]中记录了四插槽计算机的NUMA成本。对于写操作,数字如图5.3所示。

图5.3:具有多个节点的读/写性能

写比读慢,这不足为奇。有趣的部分是1跳和2跳情况的成本。实际上,这两种1跳案例的费用略有不同。有关详细信息,请参见[amdccnuma]。我们需要从该图表记住的事实是,两跳读取和写入的速度分别比0跳读取慢30%和49%。2跳写比0跳写慢32%,比1跳写慢17%。处理器和内存节点的相对位置可能会有很大的不同。AMD的下一代处理器将具有每个处理器四个相干的HyperTransport链接。在这种情况下,四插槽机器的直径将为一。对于八个插槽,由于具有八个节点的超立方体的直径为三,因此同样的问题也会报复。

所有这些信息都是可用的,但是使用起来很麻烦。在6.5节中,我们将看到一个有助于更轻松地访问和使用此信息的界面。

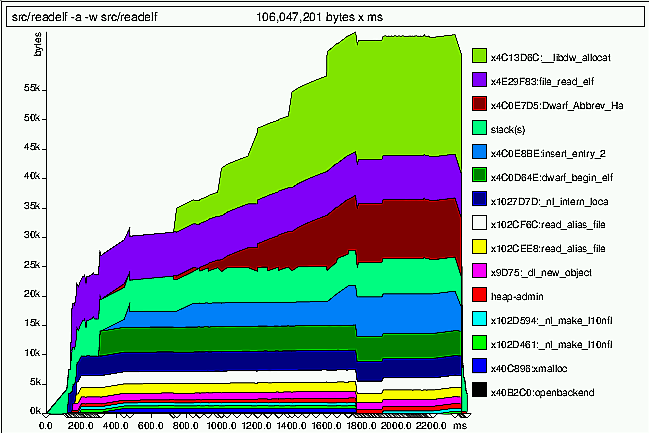

系统提供的最后一条信息是流程本身的状态。可以确定内存映射文件,写时复制(COW)页面和匿名内存如何在系统中的节点上分布。{写时复制是一种在OS实现中经常使用的方法,当一个内存页首先有一个用户,然后必须复制以允许独立用户时。在许多情况下,根本不需要复制,或者根本不需要复制,在这种情况下,仅当任何一个用户修改了内存时才复制。操作系统拦截写操作,复制内存页,然后允许写指令继续进行。}每个进程都有一个文件/ proc / PID / numa_maps,其中PID 是进程的ID,如图5.2所示。

00400000默认文件= / bin / cat映射= 3 N3 = 3 00504000默认文件= / bin / cat anon = 1脏= 1映射= 2 N3 = 2 00506000默认堆anon = 3脏= 3活动= 0 N3 = 3 38a9000000默认文件= / lib64 / ld-2.4.so映射= 22 mapmax = 47 N1 = 22 38a9119000默认文件= / lib64 / ld-2.4.so anon = 1脏= 1 N3 = 1 38a911a000默认文件= / lib64 / ld-2.4.so anon = 1脏= 1 N3 = 1 38a9200000默认文件= / lib64 / libc-2.4.so映射= 53 mapmax = 52 N1 = 51 N2 = 2 38a933f000默认文件= / lib64 / libc-2.4.so 38a943f000默认文件= / lib64 / libc-2.4.so anon = 1脏= 1映射= 3 mapmax = 32 N1 = 2 N3 = 1 38a9443000默认文件= / lib64 / libc-2.4.so anon = 1脏= 1 N3 = 1 38a9444000默认anon = 4脏= 4活动= 0 N3 = 4 2b2bbcdce000默认anon = 1脏= 1 N3 = 1 2b2bbcde4000默认anon = 2脏= 2 N3 = 2 2b2bbcde6000默认文件= / usr / lib / locale / locale-archive映射= 11 mapmax = 8 N0 = 11 7fffedcc7000默认堆栈anon = 2脏= 2 N3 = 2图5.2:/ proc / PID / numa_maps的内容

文件中的重要信息是N0到N3的值,它们表示为节点0到3上的内存区域分配的页数。可以很好地猜测该程序是在节点3的核心上执行的。本身和脏页分配在该节点上。只读映射(例如ld-2.4.so和 libc-2.4.so的第一个映射)以及共享文件的locale-archive被分配在其他节点上。

如图5.3所示,对于1跳和2跳读取,跨节点的读取性能分别下降了9%和30%。为了执行,需要进行此类读取,如果丢失了L2高速缓存,则每个高速缓存行都会产生这些额外的费用。如果内存远离处理器,则针对大型工作负载(超出缓存大小)测得的所有成本都必须增加9%/ 30%。

图5.4:在远程存储器上操作

要查看现实世界中的影响,我们可以像第3.5.1节中所述测量带宽,但是这次将内存放在距离一跳的远程节点上。与使用本地内存的数据相比,该测试的结果如图5.4所示。数字在两个方向上都有一些大的尖峰,这是测量多线程代码的问题导致的,可以忽略。此图中的重要信息是读取操作始终慢20%。这比图5.3中的9%慢得多,后者很可能不是不间断的读/写操作的数字,并且可能是指较旧的处理器版本。只有AMD知道。

对于适合缓存的工作集大小,写入和复制操作的性能也会降低20%。对于超过缓存大小的工作集,写入性能不会比本地节点上的操作明显降低。互连的速度足够快以跟上内存的速度。主要因素是等待主内存所花费的时间。

内存第5部分:程序员可以做什么

6程序员可以做什么

在前面几节中的描述之后,很明显,程序员有很多很多机会积极或消极地影响程序的性能。这仅适用于与内存相关的操作。我们将从最底层的物理RAM访问和L1高速缓存开始,直至影响操作系统的功能(包括影响内存处理的操作系统功能),从头开始涵盖所有机会。

6.1绕过缓存

当产生数据并且不再(立即)再次使用数据时,内存存储操作首先读取完整的缓存行,然后修改缓存的数据这一事实对性能有害。此操作将数据从高速缓存中推出,这可能需要再次使用,以支持即将不再使用的数据。这对于大型数据结构(例如矩阵)尤其如此,这些数据结构先被填充然后在以后使用。在填充矩阵的最后一个元素之前,绝对大小会将第一个元素逐出,使写入的缓存无效。

对于这种情况和类似情况,处理器为非临时写操作提供支持 。在这种情况下,非时间意味着数据将不会很快被重用,因此没有理由对其进行缓存。这些非临时写操作不会先读取高速缓存行,然后再对其进行修改。而是将新内容直接写入内存。

这听起来可能很昂贵,但不一定如此。处理器将尝试使用写合并(请参阅第3.3.3节)填充整个缓存行。如果此操作成功,则根本不需要内存读取操作。对于x86和x86-64体系结构,gcc提供了许多内在函数:

#include <emmintrin.h> void _mm_stream_si32(int * p,int a); void _mm_stream_si128(int * p,__m128i a); 无效_mm_stream_pd(double * p,__m128d a); #include <xmmintrin.h> 无效_mm_stream_pi(__ m64 * p,__m64 a); void _mm_stream_ps(float * p,__m128 a); #include <ammintrin.h> 无效_mm_stream_sd(double * p,__m128d a); void _mm_stream_ss(float * p,__m128 a);

如果这些指令一次处理大量数据,它们的使用效率最高。数据从内存中加载,经过一个或多个步骤进行处理,然后写回到内存中。数据“流”通过处理器,因此是内部函数的名称。

内存地址必须分别对齐8或16个字节。在使用多媒体扩展名的代码中,可以用这些非临时版本替换普通的_mm_store_ *内部函数。在9.1节中的矩阵乘法代码中,我们不这样做,因为写入的值会在很短的时间内被重用。这是使用流指令无用的示例。有关此代码的更多信息,请参见第6.2.1节。

处理器的写合并缓冲区只能将对缓存行的部分写请求保持这么长时间。通常有必要发出所有一条一条一条地修改一条高速缓存行的所有指令,以使写入合并实际上可以进行。如何执行此操作的示例如下:

#include <emmintrin.h> 无效的setbytes(char * p,int c) { __m128i i = _mm_set_epi8(c,c,c,c, c,c,c,c, c,c,c,c, c,c,c,c); _mm_stream_si128((__ m128i *)&p [0],i); _mm_stream_si128((__ m128i *)&p [16],i); _mm_stream_si128((__ m128i *)&p [32],i); _mm_stream_si128((__ m128i *)&p [48],i); }

假设指针p正确对齐,则对该函数的调用会将所寻址的缓存行的所有字节设置为c。写合并逻辑将看到生成的四个movntdq 指令,并且仅在执行完最后一条指令后才向内存发出写命令。总而言之,此代码序列不仅避免了在写入之前读取缓存行,而且还避免了用很快可能不需要的数据污染缓存。在某些情况下,这可以带来巨大的好处。使用此技术的日常代码的一个示例是C运行时中的 memset函数,对于大型块,应使用类似于上面的代码序列。

一些体系结构提供专门的解决方案。PowerPC体系结构定义了dcbz指令,该指令可用于清除整个缓存行。该指令实际上并未绕过高速缓存,因为已为结果分配了高速缓存行,但是没有从内存中读取任何数据。它比非临时存储指令有更多限制,因为高速缓存行只能设置为全零,并且会污染高速缓存(如果数据是非临时的),但是不需要写合并逻辑来实现。结果。

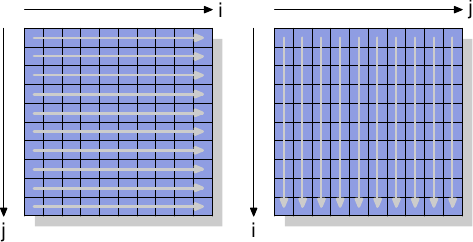

为了查看非时间指令的实际效果,我们将看一个新的测试,该测试用于测量以二维数组组织的矩阵的写入。编译器将矩阵布置在内存中,以便最左边的(第一个)索引寻址具有所有元素顺序排列在内存中的行。右(第二)索引处理一行中的元素。测试程序以两种方式遍历矩阵:首先通过增加内部循环中的列数,然后通过增加内部循环中的行索引。这意味着我们得到了如图6.1所示的行为。

图6.1:矩阵访问模式

我们测量初始化3000×3000矩阵所需的时间。要查看内存的行为,我们使用不使用缓存的存储指令。在IA-32处理器上,“非时间提示”用于此目的。为了进行比较,我们还测量了普通商店的运营情况。结果见表6.1。

内环增量 行 柱 正常 0.048秒 0.127秒 非临时性 0.048秒 0.160秒 表6.1:时序矩阵初始化

对于确实使用高速缓存的普通写入,我们看到了预期的结果:如果顺序使用内存,则将获得更好的结果,与几乎随机访问相比,整个操作为0.048s,转换为大约750MB / s这需要0.127s(约280MB / s)。矩阵足够大,以至于缓存实际上是无效的。

我们在此主要感兴趣的部分是绕过缓存的写入。令人惊讶的是,这里的顺序访问与使用缓存的情况下一样快。出现这种现象的原因是处理器正在执行如上所述的写合并。此外,放宽了非临时写入的内存排序规则:程序需要显式插入内存屏障(x86和x86-64处理器的防护指令)。这意味着处理器拥有更大的自由写回数据,从而尽可能地使用可用带宽。

在内部循环中按列访问时,情况有所不同。结果比缓存访问的情况要慢得多(0.16s,约225MB / s)。在这里我们可以看到不可能进行写合并,并且每个存储单元都必须单独寻址。这就需要不断地在RAM芯片中选择具有所有相关延迟的新行。结果比缓存的运行结果差25%。

在读取方面,直到最近,除了使用非临时访问(NTA)预取指令的弱提示之外,处理器都缺乏支持。没有等同于读取的写合并,这对于不可缓存的内存(例如内存映射的I / O)尤其不利。英特尔通过SSE4.1扩展引入了NTA负载。它们使用少量的流式负载缓冲区来实现。每个缓冲区包含一个缓存行。第一个movntdqa给定缓存行的指令会将一条缓存行加载到缓冲区中,可能会替换另一条缓存行。后续的16字节对齐访问同一高速缓存行将以很小的成本从加载缓冲区进行服务。除非有其他原因,否则高速缓存行将不会加载到高速缓存中,从而可以加载大量内存而不会污染高速缓存。编译器为此指令提供了一个内在函数:

#include <smmintrin.h> __m128i _mm_stream_load_si128(__m128i * p);

此内在函数应多次使用,并以16字节块的地址作为参数传递,直到读取每个高速缓存行。只有这样才能启动下一个缓存行。由于有一些流读取缓冲区,因此有可能一次从两个内存位置读取数据。

我们应该从该实验中删除的是,现代CPU可以很好地优化未缓存的写访问和(最近)读访问,只要它们是顺序的即可。处理仅使用一次的大型数据结构时,此知识会非常有用。其次,缓存可以帮助掩盖部分但不是全部的随机存储器访问成本。由于实现了RAM访问,本示例中的随机访问速度降低了70%。在实现更改之前,应尽可能避免随机访问。

在有关预取的部分中,我们将再次查看非时间标志。

6.2缓存访问

程序员在缓存方面可以做出的最重要的改进是那些会影响1级缓存的改进。在包含其他级别之前,我们将首先讨论它。显然,对1级缓存的所有优化也会影响其他缓存。所有内存访问的主题都是相同的:提高局部性(空间和时间)并对齐代码和数据。

6.2.1优化1级数据缓存访问

在3.3节中,我们已经看到有效使用L1d缓存可以提高性能的程度。在本节中,我们将显示哪些代码更改可以帮助提高性能。在上一节的基础上,我们首先专注于顺序访问内存的优化。如第3.3节中的数字所示,当顺序访问存储器时,处理器会自动预取数据。

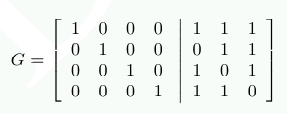

使用的示例代码是矩阵乘法。我们使用两个1000×1000 双 元素的正方形矩阵。对于那些忘记了数学的人,给定两个矩阵A和B的元素a ij和b ij且0≤i,j <N,则乘积为

简单的C实现可以如下所示:

对于(i = 0; i <N; ++ i) 对于(j = 0; j <N; ++ j) 对于(k = 0; k <N; ++ k) res [i] [j] + = mul1 [i] [k] * mul2 [k] [j];

两个输入矩阵是mul1和mul2。假定结果矩阵res初始化为全零。这是一个很好且简单的实现。但是很明显,我们确实具有图6.1中解释的问题。当 mul1被顺序访问时,内部循环使mul2的行数前进。这意味着mul1的处理方式类似于图6.1中的左矩阵,而mul2的处理方式类似于右侧矩阵。不好

有一种可能的补救措施,可以轻松尝试。由于矩阵中的每个元素都会被多次访问,因此在使用第二矩阵mul2之前,有必要重新排列(用数学术语来说是“转置”) 。

转置后(传统上用上标“ T”表示),我们现在依次遍历两个矩阵。就C代码而言,现在看起来像这样:

双tmp [N] [N]; 对于(i = 0; i <N; ++ i) 对于(j = 0; j <N; ++ j) tmp [i] [j] = mul2 [j] [i]; 对于(i = 0; i <N; ++ i) 对于(j = 0; j <N; ++ j) 对于(k = 0; k <N; ++ k) res [i] [j] + = mul1 [i] [k] * tmp [j] [k];

我们创建一个临时变量来包含转置矩阵。这需要占用更多的内存,但是希望可以收回此成本,因为每列1000次非顺序访问的成本更高(至少在现代硬件上如此)。是时候进行一些性能测试了。时钟速度为2666MHz的Intel Core 2的结果为(以时钟周期为单位):

原版的 转置 周期数 16,765,297,870 3,922,373,010 相对的 100% 23.4%

通过矩阵的简单转换,我们可以实现76.6%的加速!复制操作已完成。1000次非顺序访问确实很痛苦。

下一个问题是这是否是我们能做的最好的事情。无论如何,我们当然需要一种不需要其他副本的替代方法。我们并不总是拥有执行复制的能力:矩阵可能太大,或者可用内存太小。

寻找替代实施方案应首先仔细检查所涉及的数学和原始实施方案所执行的操作。简单的数学知识使我们可以看到,只要每个加数恰好出现一次,对结果矩阵的每个元素进行加法的顺序就无关紧要。{我们在这里忽略算术效应,这可能会改变上溢,下溢或舍入的发生。}这种理解使我们能够寻找对原始代码的内循环中执行的添加进行重新排序的解决方案。

现在让我们检查一下原始代码执行中的实际问题。mul2元素的访问顺序为:(0,0),(1,0),...,(N-1,0),(0,1),(1,1),...。元素(0,0)和(0,1)位于同一高速缓存行中,但是,当内部循环完成一轮时,此高速缓存行早已被逐出。对于此示例,对于三个矩阵中的每个矩阵,内部循环的每一轮都需要1000个缓存行(对于Core 2处理器,需要64个字节)。这加起来比可用的L1d的32k要多得多。

但是,如果在执行内部循环时我们一起处理中间循环的两次迭代该怎么办?在这种情况下,我们使用高速缓存行中的两个double值,这些值保证在L1d中。我们将L1d错过率降低了一半。这当然是一种改进,但是,根据缓存行的大小,它可能仍然不如我们所能得到的好。Core 2处理器的L1d缓存行大小为64字节。实际值可以使用查询

sysconf(_SC_LEVEL1_DCACHE_LINESIZE)

在运行时或从命令行使用getconf实用程序,以便可以为特定的缓存行大小编译程序。随着 的sizeof(双)为8,这意味着,充分利用高速缓存行,我们应该展开环路中间的8倍。继续这种思想,同样要有效地使用res矩阵,即同时写入8个结果,我们也应该将外部循环展开8次。我们在这里假定大小为64的高速缓存行,但是该代码在具有32字节高速缓存行的系统上也能很好地工作,因为两条高速缓存行也都被100%使用。通常,最好使用getconf 实用程序在编译时对高速缓存行大小进行硬编码,如下所示:

gcc -DCLS = $(getconf LEVEL1_DCACHE_LINESIZE)...

如果二进制文件是通用的,则应使用最大的缓存行大小。对于非常小的L1ds,这可能意味着并非所有数据都适合高速缓存,但是此类处理器无论如何都不适合高性能程序。我们得到的代码如下所示:

#定义SM(CLS / sizeof(双精度)) 对于(i = 0; i <N; i + = SM) 对于(j = 0; j <N; j + = SM) 对于(k = 0; k <N; k + = SM) 对于(i2 = 0,rres =&res [i] [j], rmul1 =&mul1 [i] [k]; i2 <SM; ++ i2,rres + = N,rmul1 + = N) 对于(k2 = 0,rmul2 =&mul2 [k] [j]; k2 <SM; ++ k2,rmul2 + = N) 对于(j2 = 0; j2 <SM; ++ j2) rres [j2] + = rmul1 [k2] * rmul2 [j2];

这看起来很吓人。在某种程度上,这是但仅因为它包含了一些技巧。最明显的变化是我们现在有六个嵌套循环。外循环以SM的间隔进行迭代(缓存行大小除以sizeof(double))。这将乘法分为几个较小的问题,可以用更多的缓存局部性来处理。内部循环遍历外部循环的缺失索引。再有三个循环。这里唯一棘手的部分是k2和j2循环的顺序不同。这样做是因为在实际计算中,只有一个表达式取决于k2,而两个表达式取决于j2。

剩下的复杂性是由于gcc在优化数组索引方面不是很聪明。引入额外的变量rres,rmul1和 rmul2可以通过将公共表达式尽可能远地从内部循环中拉出来优化代码。C和C ++语言的默认别名规则不能帮助编译器做出这些决定(除非使用了限制,所有指针访问都是潜在的别名来源)。这就是为什么Fortran仍然是数字编程的首选语言:它使编写快速代码更加容易。{理论上,限制在1999年修订版中引入C语言的关键字应该可以解决该问题。但是,编译器尚未赶上。原因主要是存在太多不正确的代码,它们会误导编译器并导致其生成不正确的目标代码。}

表6.2列出了所有这些工作的回报方式。

原版的 转置 子矩阵 向量化 周期数 16,765,297,870 3,922,373,010 2,895,041,480 1,588,711,750 相对的 100% 23.4% 17.3% 9.47% 表6.2:矩阵乘法时序

通过避免复制,我们又获得了6.1%的性能。另外,我们不需要任何其他内存。只要结果矩阵也适合内存,输入矩阵就可以任意大。这是我们现已实现的一般解决方案的要求。

表6.2中还有一列未解释。如今,大多数现代处理器都对矢量化提供了特殊支持。这些特殊的指令通常被称为多媒体扩展名,它们允许同时处理2、4、8或更多值。这些通常是SIMD(单指令,多数据)操作,其他操作则对其进行了扩充,以获取正确格式的数据。英特尔处理器提供的SSE2指令可以处理两个 加倍一次操作中的值。指令参考手册列出了可访问这些SSE2指令的内在功能。如果使用了这些内在函数,则该程序将运行另外7.3%(相对于原始函数)的速度更快。结果是一个程序以原始代码的10%的时间运行。换算成人们可以识别的数字,我们从318 MFLOPS升至3.35 GFLOPS。由于这里我们只对内存效应感兴趣,因此程序代码被推送到9.1节中。

应该注意的是,在代码的最新版本中,mul2仍然存在一些缓存问题;预取仍然无法进行。但是,如果不对矩阵进行转置,这是无法解决的。也许高速缓存预取单元会变得更聪明以识别模式,那么就不需要进行其他更改。不过,在具有单线程代码的2.66 GHz处理器上的3.19 GFLOPS不错。

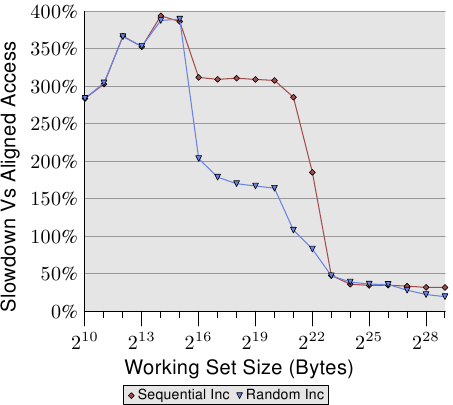

在矩阵乘法示例中,我们优化的是使用加载的缓存行。总是使用高速缓存行的所有字节。我们只是确保在撤消缓存行之前就已使用它们。这当然是特例。

具有填充一个或多个高速缓存行的数据结构更为常见,其中程序一次只使用几个成员。在图3.11中,我们已经看到如果只使用几个成员,则大型结构的效果。

图6.2:分布在多个缓存行中

图6.2显示了使用目前众所周知的程序执行的另一组基准测试的结果。这次添加了相同列表元素的两个值。在一种情况下,两个元素都位于同一缓存行中;在另一种情况下,一个元素位于列表元素的第一行缓存中,第二个元素位于最后一个缓存行中。该图显示了我们正在经历的放慢脚步。

毫不奇怪,如果工作集适合L1d,则在所有情况下都不会产生负面影响。一旦L1d不再足够,将在处理中使用两条高速缓存行而不是一条,来支付罚款。红线显示列表在内存中的顺序排列时的数据。我们看到了通常的两个步骤模式:L2高速缓存足够时大约17%的损失,而必须使用主存储器时大约27%的损失。

在随机存储器访问的情况下,相对数据看起来有些不同。适用于L2的工作集的速度降低了25%至35%。除此之外,它下降到大约10%。这不是因为惩罚变小,而是因为实际内存访问的开销成比例地增加。数据还表明,在某些情况下,元素之间的距离确实很重要。随机4 CL曲线显示出更高的惩罚,因为使用了第一和第四缓存行。

与缓存行相比,查看数据结构布局的一种简单方法是使用pahole程序(请参阅[dwarves])。该程序检查以二进制形式定义的数据结构。采取一个包含此定义的程序:

struct foo { 诠释 长填充[7]; int b; };

pahole在64位计算机上编译,其输出包含(除其他外)图6.3中所示的信息。

struct foo { 诠释 / * 0 4 * / / * XXX 4个字节的空洞,请尝试打包* / 长整数填充[7];/ * 8 56 * / / * ---缓存行1边界(64字节)--- * / int b; / * 64 4 * / }; / *大小:72,高速缓存行:2 * / / *总和成员:64,孔:1,总和孔:4 * / / *填充:4 * / / *最后一个缓存行:8个字节* /图6.3:Pahole Run的输出

这个输出告诉我们很多。首先,它表明数据结构使用了多个缓存行。该工具假定当前使用的处理器的缓存行大小,但是可以使用命令行参数覆盖此值。特别是在结构的大小刚好超过高速缓存行的限制并且分配了许多此类对象的情况下,寻找一种压缩该结构的方法是有意义的。也许某些元素可以具有较小的类型,或者某些字段实际上是可以使用单个位表示的标志。

在该示例的情况下,压缩很容易,并且程序提示了压缩。输出显示在第一个元素之后有四个字节的空洞。该孔是由结构和填充元素的对齐要求引起的。显而易见,元素b的大小为4个字节(在行的末尾由4表示),完全适合间隙。在这种情况下,结果是间隙不再存在,并且数据结构适合一条高速缓存行。Pahole工具本身可以执行此优化。如果-重新组织使用参数并在命令行末尾添加结构名称,该工具的输出是优化的结构和缓存行的使用。除了移动元素以填充间隙外,该工具还可以优化位场并将填充和孔合并。有关更多详细信息,请参见[矮人]。

当然,理想的情况是有一个足够大的孔供尾随元件使用。为了使此优化有用,需要将对象本身与高速缓存行对齐。我们稍作讨论。

通过pahole输出,还可以更轻松地确定是否必须重新排序元素,以便将一起使用的那些元素也存储在一起。使用pahole工具,可以轻松地确定哪些元素在同一高速缓存行中,以及何时必须重新组合元素才能实现此目的。这不是一个自动过程,但是该工具可以提供很多帮助。

各个结构元素的位置及其使用方式也很重要。正如我们在3.5.2节中所看到的那样,在高速缓存行中带有关键单词的代码的性能更差。这意味着程序员应始终遵循以下两个规则:

-

始终将最有可能成为关键字的结构元素移到结构开头。

-

当访问数据结构时,访问顺序不受情况的限制,请按在结构中定义元素的顺序访问元素。

对于小型结构,这意味着程序员应按可能访问元素的顺序排列元素。必须以灵活的方式处理此问题,以允许同时应用其他优化,例如填充孔。对于更大的数据结构,每个缓存行大小的块都应按照规则进行排列。

但是,如果对象本身未对齐,则不值得花费时间进行重新排序。对象的对齐方式由数据类型的对齐要求决定。每个基本类型都有其自己的对齐要求。对于结构化类型,其任何元素的最大对齐要求决定了结构的对齐方式。这几乎总是小于高速缓存行的大小。这意味着即使将结构的成员对齐以适合同一高速缓存行,分配的对象也可能没有与高速缓存行大小匹配的对齐方式。有两种方法可以确保对象具有设计结构布局时使用的对齐方式:

- 可以为对象分配明确的对齐要求。对于动态分配,对malloc的调用只会分配对齐方式与最苛刻的标准类型(通常为long double)相匹配的对象。不过,可以使用posix_memalign来请求更高的对齐方式。

#include <stdlib.h> int posix_memalign(void ** memptr, size_t对齐, size_t大小);

该函数在memptr指向的指针变量中存储指向新分配的内存的指针。内存块的 大小为字节大小,并在align- byte边界上对齐。

对于由编译器分配的对象(在.data,.bss等中以及在堆栈上),可以使用变量属性:

struct strtype变量 __attribute((aligned(64)));

在这种情况下,无论strtype 结构的对齐要求如何,变量都在64字节边界对齐。这适用于全局变量以及自动变量。

但是,此方法不适用于数组。除非每个数组元素的大小是对齐值的倍数,否则只有数组的第一个元素会对齐。这也意味着必须对每个变量进行适当的注释。posix_memalign的使用 也不是完全免费的,因为对齐要求通常会导致碎片和/或更高的内存消耗。

- 可以使用type属性来更改类型的对齐要求:

struct strtype { ...成员... } __attribute((aligned(64)));

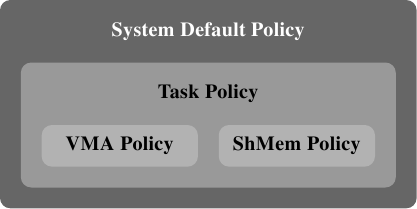

这将导致编译器以适当的对齐方式分配所有对象,包括数组。但是,程序员必须注意为动态分配的对象请求适当的对齐方式。在此 必须再次使用posix_memalign。使用gcc提供的alignof运算符很容易,并将值作为第二个参数传递给posix_memalign。