一、快时钟域到慢时钟域

当信号从快时钟域同步到慢时钟域时,有可能会导致信号的丢失,这时,我们很直接的想法是将脉冲信号拉宽之后再进行采样,主要原理就是就是在快时钟域下,将脉冲信号展宽,变成电平信号,再在慢时钟域下同步该电平信号,再用快时钟域同步慢时钟域下的脉冲信号,用该脉冲信号拉低在快时钟域下的脉冲信号。

1 // ********************************************************************************* 2 // Project Name : fast2low 3 // Email : 4 // Create Time : 2020/07/15 : 5 // Module Name : 6 // editor : 7 // Version : Rev1.0.0 8 // ********************************************************************************* 9 10 module fast2low( 11 input clka, // fast clk 12 input clkb, 13 input s_rst_n, 14 15 input pulse_a, 16 17 output pulse_outb, 18 output signal_outb 19 ); 20 21 reg signal_a ; 22 reg signal_b ; 23 24 reg signal_b_r1 ; 25 reg signal_b_r2 ; 26 27 reg signal_b_a1 ; 28 reg signal_b_a2 ; 29 30 always @(posedge clka or negedge s_rst_n) begin // 在时钟 clka 下,生成展宽信号signal_a 31 if(s_rst_n == 1'b0) 32 signal_a <= 1'b0; 33 else if(pulse_a == 1'b1) // 检测到输入信号 pulse_a_in被拉高,则拉高signal_a 34 signal_a <= 1'b1; 35 else if(signal_b_a2 == 1'b1) // 检测到 signal_b_a2被拉高,则拉低signal_a 36 signal_a <= 1'b0; 37 else 38 signal_a <= signal_a; 39 end 40 41 always @ (posedge clkb or negedge s_rst_n) begin // 在clkb下同步signal_a 42 if(s_rst_n == 1'b0) 43 signal_b <= 0; 44 else 45 signal_b <= signal_a; 46 end 47 48 always @ (posedge clkb or negedge s_rst_n) begin 49 if(s_rst_n == 1'b0) begin 50 signal_b_r1 <= 1'b0; 51 signal_b_r2 <= 1'b0; 52 end 53 else begin 54 signal_b_r1 <= signal_b; 55 signal_b_r2 <= signal_b_r1; 56 end 57 end 58 59 always @ (posedge clka or negedge s_rst_n) begin // 在时钟域clk_a下,采集signal_b_r1,用于反馈来拉低展宽信号signal_a 60 if(s_rst_n == 1'b0) begin 61 signal_b_a1 <= 1'b0; 62 signal_b_a2 <= 1'b0; 63 end 64 else begin 65 signal_b_a1 <= signal_b_r1; 66 signal_b_a2 <= signal_b_a1; 67 end 68 end 69 70 assign signal_outb = signal_b_r1; 71 assign pulse_outb = signal_b_r1 & (~signal_b_r2); 72 73 endmodule

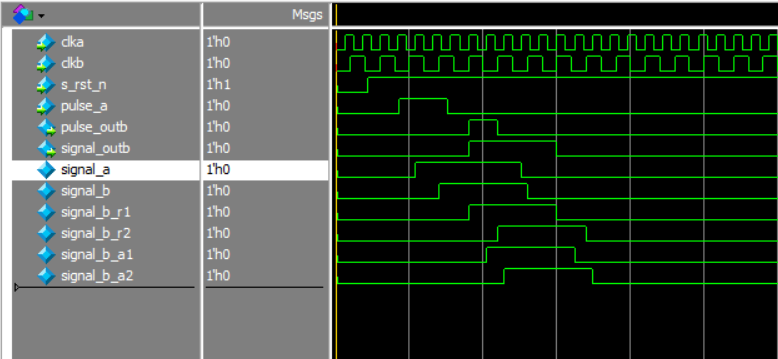

Modelsim仿真:

注:此部分代码来源于https://www.cnblogs.com/rouwawa/p/7501319.html

二、慢时钟域到快时钟域

1 // ********************************************************************************* 2 // Project Name : slow2fast 3 // Email : 4 // Create Time : 2020// : 5 // Module Name : slow2fast 6 // editor : Qing 7 // Version : Rev1.0.0 8 // ********************************************************************************* 9 10 module slow2fast( 11 input sclk , 12 input s_rst_n , 13 input pluse_in , 14 15 output pulse_out 16 ); 17 18 reg pluse_in_r1 ; 19 reg pluse_in_r2 ; 20 reg pluse_in_r3 ; 21 22 always @ (posedge sclk or negedge s_rst_n) begin 23 if(s_rst_n == 1'b0) begin 24 pluse_in_r1 <= 1'b0; 25 pluse_in_r2 <= 1'b0; 26 pluse_in_r3 <= 1'b0; 27 end 28 else begin 29 pluse_in_r1 <= pluse_in; 30 pluse_in_r2 <= pluse_in_r1; 31 pluse_in_r3 <= pluse_in_r2; 32 end 33 end 34 35 assign pulse_out = pluse_in_r3; 36 37 endmodule