Verilog 里面如果有符号数和无符号数做运算,会强制当做无符号数运算;

例如 c = a + b; 其中a和b都是四位数,c是五位。在计算时,verilog会将a和b都扩展到5位,然后再做加法,而如果a和b中有无符号数,则位宽扩展就按照无符号数来,也就是高位补0。所以如果a和b中既有无符号又有有符号,结果就不正确了。

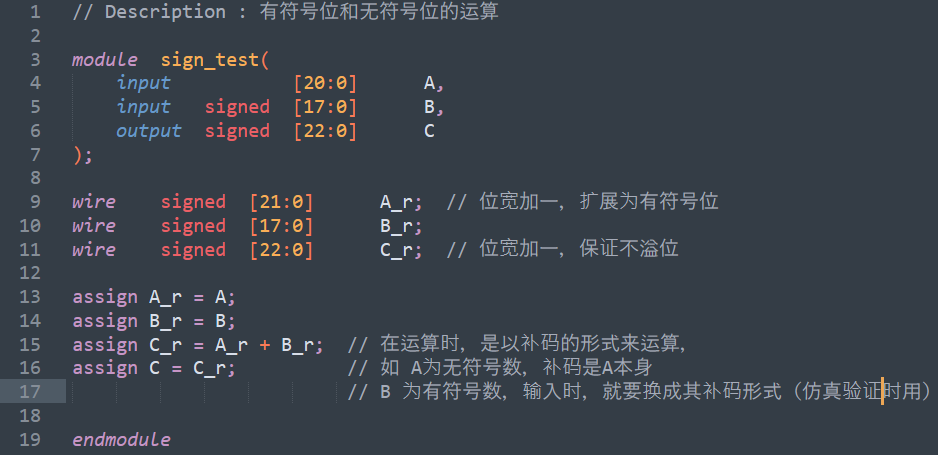

解决方法是用 signed来修饰。

如:请描述如下代码,实现加法:

C = A + B,A是21bit无符号数,B是18位有符号数,如何才能保证正确得到一个不溢出的有符号数C;

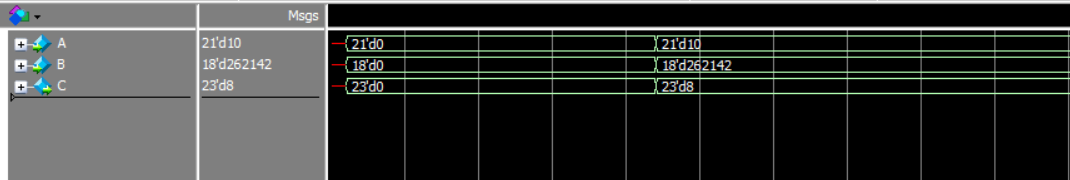

testbench:

Modelsim仿真结果:

参考: