20145321《信息安全系统设计基础》第6周总结2

教材内容总结

4.1内容 20145321《信息安全系统设计基础》第6周总结1

4.2 逻辑设计和硬件控制语言HCL

要实现一个数字系统需要三个主要的组成部分:

- 计算对位进行操作的函数的组合逻辑

- 存储位的存储器元素

- 控制存储器元素更新的时钟信号

1、逻辑门

- 逻辑门产生的输出,等于它们输入位值的某个布尔函数。

AND &&

OR ||

NOT !

逻辑门只对单个位的数进行操作,而不是整个字。- 逻辑门总是活动的,一旦一个门的输入变化,在短时间内,输出就会跟着变化。

2、组合电路和HCL布尔表达式

将逻辑门组合成一个网,构建计算块(组合电路)的限制

- 两个以上的逻辑门的输出不能连接在一起,否则可能使线上信号矛盾,导致一个不合法的电压或电路故障。

- 这个网必须是无环的,否则会导致网络计算有歧义。

3、字级的组合电路和HCL整数表达式

-执行字级计算的组合电路根据输入字的各个位,用逻辑门来计算输出字的每个位。

-所有字级的信号都声明为int,不指定字的大小。

-画字级电路时,中等粗度的线来表示携带字的每个位的线路,用虚线来表示布尔信号结果。

-多路复用函数用情况表达式来描述。

-选择表达式可以是任意的布尔表达式,可以有任意多的情况。

-组合逻辑电路可以设计成在字级数据上执行许多不同类型的操作。

5、存储器和时钟

-时序电路的两类存储器设备

- 时钟寄存器(寄存器):储存单个位或字,用时钟信号控制寄存器加载输入值。

- 随机访问储存器(储存器):储存多个字,用地址选择该读/写哪个字。

-硬件和机器级编程中的寄存器有细微差别,分为称为“硬件寄存器”和“程序寄存器”。

-处理器还包括另外一个只读存储器,用来读指令。

-在大多数实际系统中,这两个存储器被合并为一个具有双端口的存储器:一个用来读指令,一个用来读或写数据。

4.3 Y86的顺序实现

1、将处理组织成阶段

六个基本阶段

- 取指 从存储器读取指令字节,地址为程序计数器PC的值

- 译码 从寄存器读入最多两个操作数,得到valA或valB

- 执行 算术/逻辑单元要么执行指令指明的操作,计算存储器引用的有效地址,要么增加或减少栈指针。得到的值为valE。

- 访存 将数据写入存储器,或从存储器中读出数据,读出的值为valM。

- 写回 最多可以写两个结果到寄存器文件

- 更新PC 将PC设为下一条指令的地址

2、SEQ硬件结构

- 取指:将程序计数器寄存器作为地址,指令存储器读取指令的字节。PC增加器计算valP,即增加了的程序计数器。

- 译码:寄存器文件有两个读端口A和B,从这两个端口同时读寄存器的值valA和valB。

- 执行:根据指令类型将算数/逻辑单元(ALU)用于不同的目的。条件码寄存器有三个条件码位,ALU负责计算条件码的新值,当执行跳转指令时会根据条件码和跳转类型来计算分支信号Cnd。

- 访存:数据存储器读出或写入一个存储器字。指令和数据存储器访问的是相同的存储器位置,但用于不同的目的。

- 写回:寄存器文件有两个写端口,E用来写ALU计算出来的值,M用来写从数据存储器中读出来的值。

3、SEQ的时序

- SEQ的实现包括组合逻辑和两种存储器设备

-时钟寄存器 程序计数器和条件码寄存器

-随机访问存储器 寄存器文件、指令存储器和数据存储器- 组合逻辑不需要任何时序或控制

- 由于指令存储器只用来读指令,我们可以将这个单元看成是组合逻辑

-

剩下四个(程序计数器、条件码寄存器、数据存储器和寄存器文件)需要对他们的时序进行明确的控制。

条件码寄存器 只在执行整数运算指令时装载

数据存储器 只在执行rmmovl、pushl或call时写入

寄存器文件 两个写端口允许每个时钟周期更新两个程序寄存器。(特殊寄存器ID 0xF表明此端口不应执行写操作)

-

组织计算原则:处理器从来不需要为了完成一条指令的执行而去读由该指令更新了的状态。

- 用时钟来控制状态元素的更新,值通过组合逻辑传播。

4、SEQ阶段的实现

- 取指阶段:包括指令存储器单元。

- S译码和写回阶段:都需要访问寄存器文件。寄存器文件有四个端口,它支持同时进行两个读和两个写;每个端口都一个地址连接和数据连接。

- 执行阶段:包括算术/逻辑单元(ALU)。这个单元根据alufun信号的设置,对输入aluA和aluB执行ADD,SUB,AND,XOR运算。ALU的输出就是valE信号。还包括条件码寄存器。每次运行时,ALU都会产生三个与条件码相关的信号——零,符号,溢出。用set_cc来控制是否应该更新条件码寄存器。

- 访存阶段:两个控制块产生存储器地址和存储器输入数据的值;另外两个块产生控制信号表明应该执行读操作还是写操作。当执行读操作时数据存储器产生值valM。

- 更新PC阶段:SEQ中最后一个阶段会产生程序计数器的新值,依据指令的类型和是否要选择分支,新的PC可能是valC、valM、valP。

实验楼实验

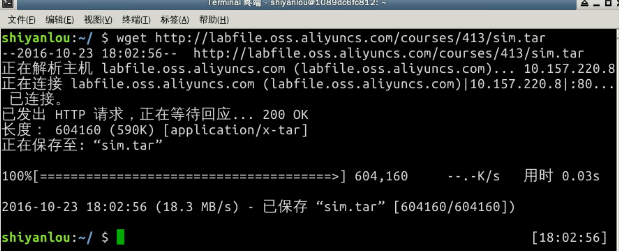

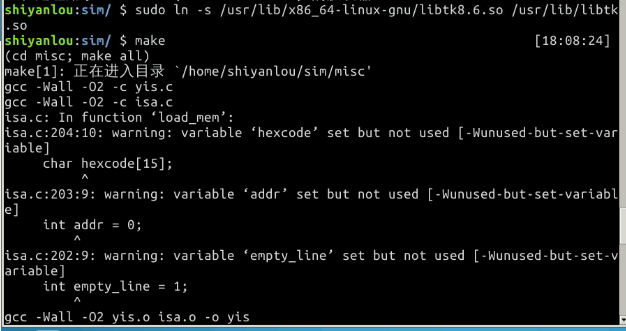

构建YIS环境:

YIS测试:

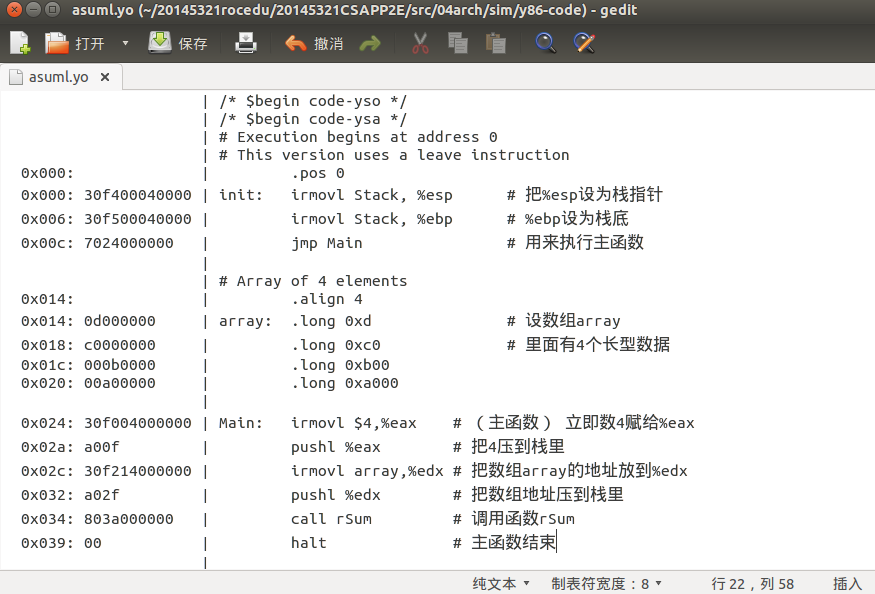

课本第239页上的代码,打印出来:

分析asuml.yo:

代码托管

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | |

|---|---|---|---|

| 目标 | 3500行 | 30篇 | 300小时 |

| 第一周 | 50/50 | 1/2 | 10/10 |

| 第二周 | 120/170 | 1/3 | 20/30 |

| 第三周 | 130/300 | 1/4 | 20/50 |

| 第五周 | 130/430 | 2/6 | 25/75 |

| 第六周 | 50/480 | 2/8 | 25/100 |