1. FPGA主要应用在并行处理资源的应用,视频与图像处理,无线通信的中频调制解调器。

嵌入式乘法器可以配置成一个 18 × 18 乘法器,或者配置成两个 9 × 9 乘法器。对于那些大于18 × 18 的乘法运算 ,Quartus® II 软件会将多个嵌入式乘法器模块级联在一起。虽然没有乘法器数据位宽的限制,但数据位宽越大,乘法运算就会越慢。除了 Cyclone IV 器件中的嵌入式乘法器,通过将 M9K 存储器模块用作查找表 (LUT) 可以实现软乘法器。疑问是4输入查找表的,就是一个表,4个输入固定,那么输出 就是固定的。那么这个表是怎么写进去的。

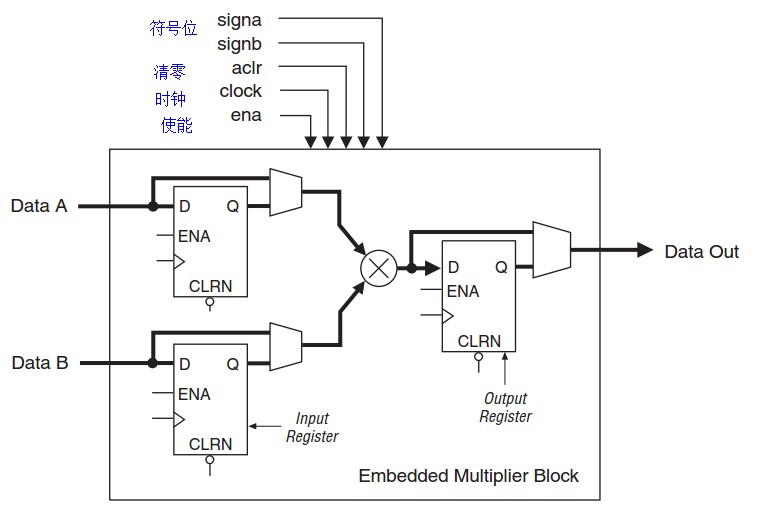

2. 每个嵌入式乘法器均由以下几个单元组成: 乘法器级,输入与输出寄存器,输入与输出接口。

根据乘法器的操作模式,您可以将每个乘法器输入信号连接到输入寄存器,或直接以 9 bit 或 18 bit 的形式连接到内部乘法器。您可以单独地设置乘法器的每个输入是否使用输入寄存器。例如, 将乘法器Data A信号连接到输入寄存器,并且将Data B信号直接连接到内部乘法器。

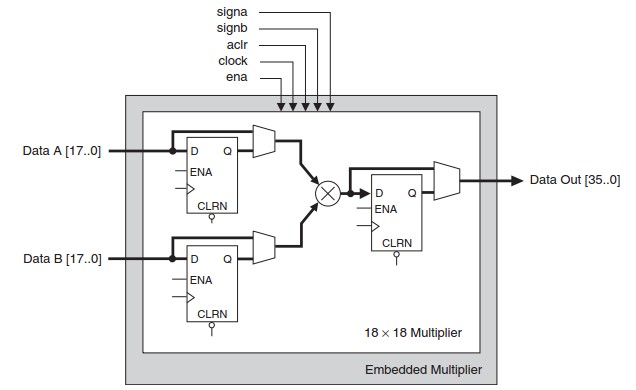

嵌入式乘法器模块的乘法器级支持 9 × 9 或者 18 × 18 乘法器,并支持这些配置之间的其它乘法器。根据乘法器的数据宽度或者操作模式,单一嵌入式乘法器能够同时执行一个或者两个乘法运算。

乘法器的每一个操作数都是一个唯一的有符号或者无符号数。signa与signb信号控制乘法器的输入,并决定值是有符号的还是无符号的。如果signa信号为高电平,则Data A操作数是一个有符号数值。反之,Data A操作数便是一个无符号数值。

3. 根据不同的应用需要,有两种的乘法器工作模式的一种:一个 18 × 18 乘法器,最多两个 9 × 9 独立的乘法器。通过使用 Cyclone IV 器件的嵌入式乘法器,可以实现乘法加法器和乘法累加器功能,这一功能的乘法器部分由嵌入式乘法器来实现,而加法器或者累加器功能则在逻辑单元 (LE) 中实现。

4. 一个 18 × 18 乘法器

5. 最多两个 9 × 9 独立的乘法器