上一节大致给出了descriptor的结构,这篇细致分析各个field:

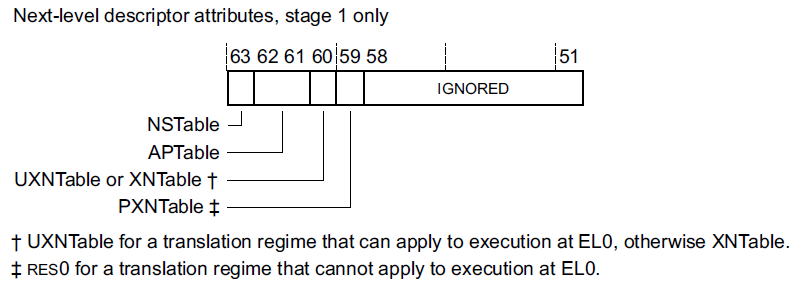

1) Table Descriptor:stage2中不包含任何的attribute的field,每个level中的descriptor高位作为下一个level的attr配置。

NSTable,bit[63], 定义subsequent lookup的secure state

APTable,bit[62:61],

UXNTable,bit[60],

PXNTable,bit[59],

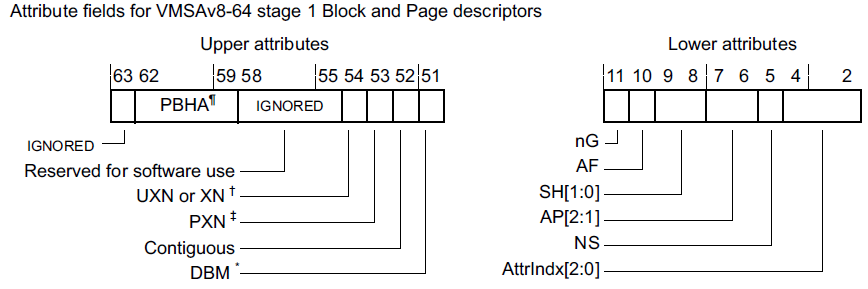

2) Block and Page descriptor:stage1,stage2都可以设置,每个memory attr分为upper block和lower block

Stage1:

Upper:

PBHA,bit[62:59],用来支持ARMv8.2-TTPBHA,

XN、UXN,bit[54],

PXN,bit[53],

Contiguous,bit[52],根据颗粒的大小,表示一定数量的相邻的table,被选中。

DBM,Dirty Bit Modifier,bit[51]

Lower:

AF,bit[10],Access flag

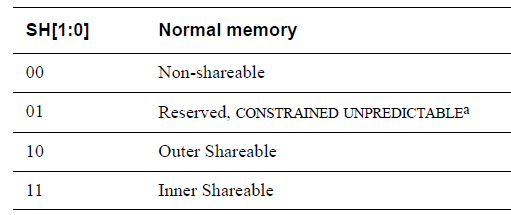

SH,bit[9:8],Shareability field

AP,bit[7:6],Data Access Permission

NS,bit[5],non-secure bit

Attrindex,bit[4:2],Stage1 memory attributes index, for MAIR_ELx

Stage2:

新的field包括:

S2AP,bit[7:6],Stage2 Data Access Permission

MemAttr,bit[5:2],Stage2 memory attributes,

接下来分为access permission和memory attributes来分析field。

Access Permission,控制data access和instruction fetch。

Pstate,在ARMv8.2中,是一个描述process state的寄存器,包括

1) condition flags---------N(negative),Z(zero),C(carry),V(overflow)

2) execution state--------EL(current except level),SP(Stack Pointer)

3) exception mask bit

4) access control bit----PAN(privilege access never),UAO(User Access Override)

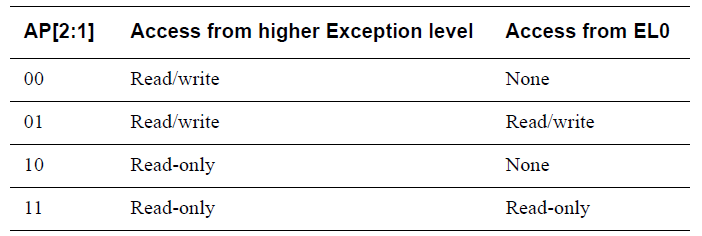

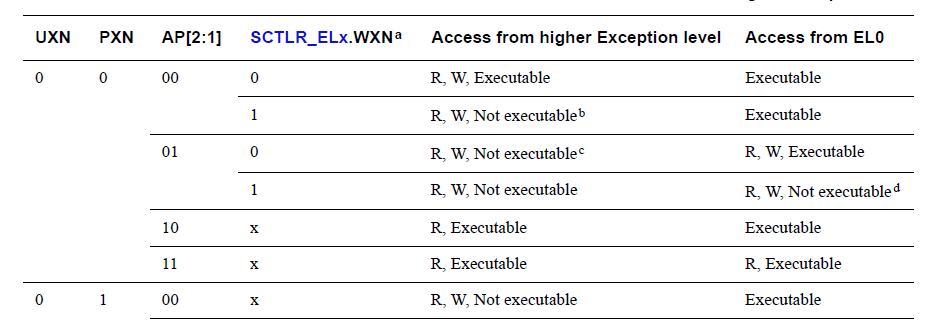

Stage1中的AP[2:1],

1) AP[2],在read-only和write-read之间选择;

2) AP[1],在EL0和更高的exception level中选择;(none表示mmu报错)

S2AP,在non-secure的EL0、EL1中,

AP和S2AP都设置时,都会起作用。

TCR_ELn寄存器中的APTable[1:0],

总结,关于execution 的 access

。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。。

AF(access flag),是软件的应用,表明目前该page是否被访问过,优化在OS memory control中的实现。

还有dirty state bit,也是做软件优化使用的,具体看armv8 doc

Bit[58:55],不论是block descripter还是table descripter,中都会预留,为OS使用。可以存放page是否dirty等信息。

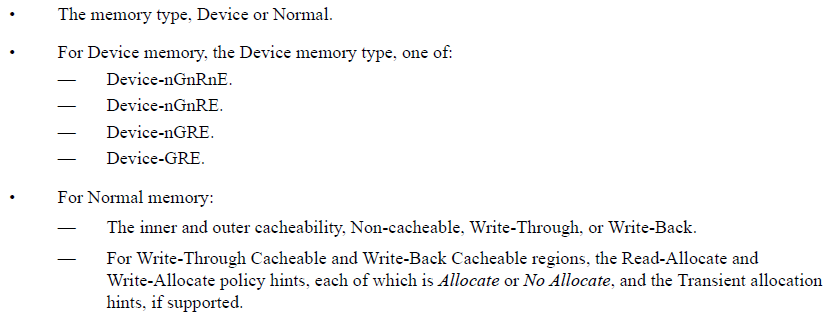

memory region atribute,只针对block和page类型的descriptor

stage1中,AttrIndx[2:0],选定某个MAIR_ELn,实现memory attri的配置;

SH[1:0]对于normal memory,定义Shareability;

stage2中的MemAttr,4bit实现类似MARI的配置、

SH[1:0]对于normal memory,实现shareability的配置。

stage1和stage2都配置时,都会起作用,优先级以及覆盖情况,详见armv8 doc

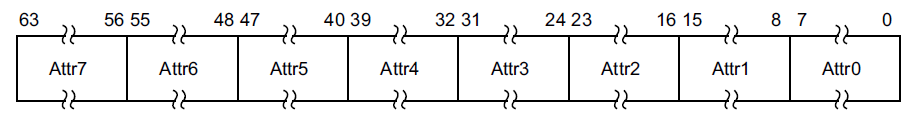

MAIR_ELn64位寄存器,一共有三个,分为EL1,EL2,EL3,64bit被分为8个byte,每个byte内部编码指定attribute。