Timing path:从register clock/input port开始,经过一些combinational logic,终止在register data/output port。

PT以path grouping为单位来分析和报告timing。

DC,每个path group可以指定一个weight,来尽力做design optimizaiton,但是这个weight在PT中并没有用。

每个create clock命令都会生成一个对应的path group。

PT中还有自己的default group:clock_gating_default**:path以combinational element为终点。

async_default*:path以async的preset和clear为终点。

*default*:剩下的所有clock,如以output为终点的clock。

也可以自己定义group_path:group_path -name out1bus -to [get_ports OUT_1*] 然后可以报告该path group的timing。

report_timing命令中的属性:

Number of paths:-nworst 显示每个end point最worst的N条path,-max_paths 显示整个group的worst path的个数

Types of paths:-path_type full -delay_type max

Amount of detail

Startpoints,endpoint

-path_type full_clock/full_clock_expanded 显示完整的data path和clock path

full 显示完整data path

short 只显示一条data path的startpoint和endpoint

-transition_time 报告路径的transition time

-capacitance 报告路径的capacitance

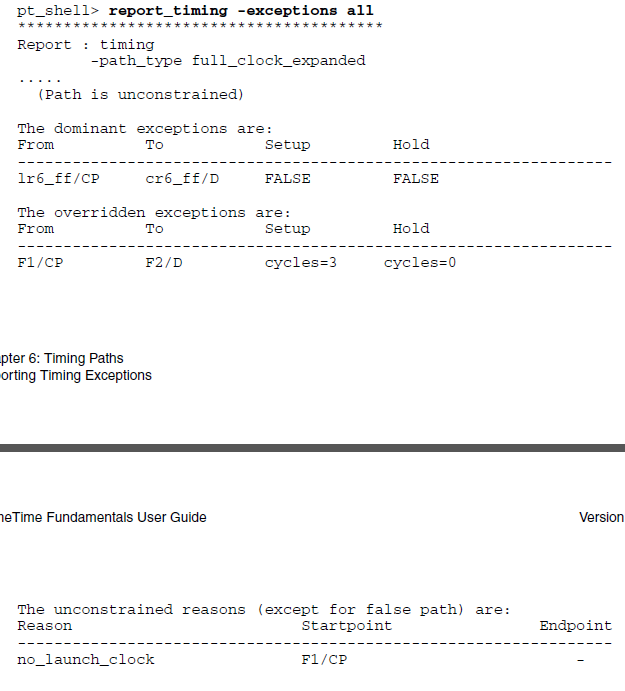

对于exception timing的rpt:

1)-exceptions dominant 报告路径中的exception constrained

2)-exceptions overridden 报告路径中被覆盖的exception constrained

3)-exceptions all 报告所有的exception path,包括unconstrained startpoint 和unconstrained endpoint

exceptions path的三种属性:方便进行filter

dominant_exception timing path的类型:false path, min_delay, max_delay, multicycle_path

endpoint_unconstrained_reason:no_capture_clock, dangling_end_point(floating point no timing constraints), danin_of_disable(disable timing arc)

startpoint_unconstrained_reason:no_launch_clock,dangling_start_point,fanout_of_disable

filter_collection $path {defined(dominant_exception)}

filter_collection $path {undefined(dominant_exception)}

get_timing_path更好的删选timing path

set x [get_timing_paths -from A -through B -to C]

report_timing $x -exceptions all

Path Sepecification Methods

-from $startpoint

-to $endpoint

-through

report_timing -from [get_clocks ...] -though $startpoint

report_timing -through $endpoint -to [get_clocks ...]

report_timing -through {B1 B2}

更加精细的方式:

-rise_from/-rise_to

-fall_from/-fall_through...

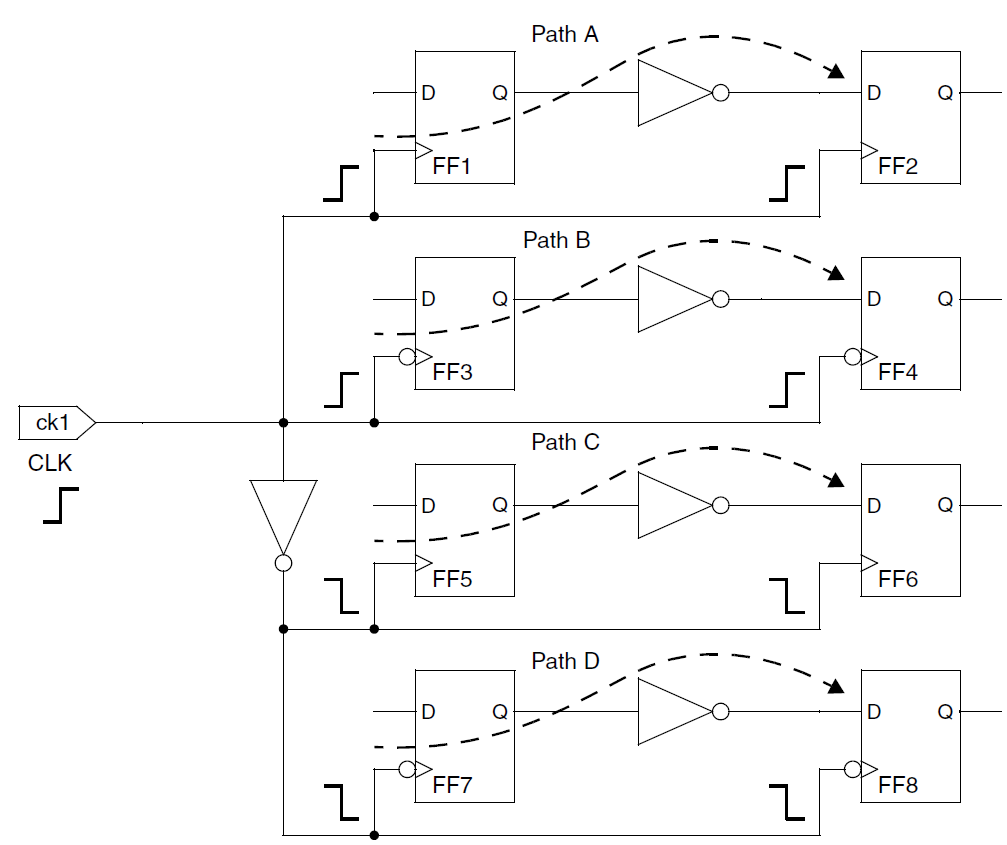

set_false_path -to [get_clocks CLK] :取以CLK为终点的timing path,data端的FF的clock是CLK

path:a,b,c,d有效

set_false_path -rise_from [get_clocks CLK] :以CLK为起点,且data端以clock的rising edge来触发

path:a,d有效

report_timing -rise_from [get_clock clk] -nworst 100

对于delay的report:

report_delay_calculation -from BLK1/A -to BLK1/z