前言:wire,assign,reg本来就是verilog中很容易搞混的东西,我就在下面说说我的理解。

一直都没有搞懂verilog里面的wire的作用,一直都没怎么用到,所以也就是混着混着过着。最近在做自己毕业设计,要用到Verilog,所以又把这些东西捡起来,今年在写一段程序时,在两个模块之间连线的时候出现了问题,在网上找到一个程序,仔细研究了下顶层,终于把这个东西看明白了。故贴出来和大家分享,也是个人理解,刚刚上手,欢迎大家交流。

大家先看看下面这段代码:

1 module top

2 {

3 //////////////////// Clock Input ////////////////////

4 clk_50, // 50 MHz

5 //////////////////// Reset ////////////////////

6 reset,

7 //////////////////// en ////////////////////

8 en,

9 //////////////////// selecet ////////////////////

10 wave1,

11 wave2,

12 wave3,

13 }

14

15

16 input clk_50;

17 input reset;

18 output en;

19 output [7:0] fword; //frequancy

20 output wave1; //zheng

21 output wave2; //sanjiao

22 output wave3; //juchibo

23

24 wire sine_en;

25 wire tri_en;

26 wire too_en;

27

28 nios u0

29 {

30 .clk(clk_50),

31 .reset_n(reset),

32 .out_port_from_the_en(en),

33 .out_port_from_the_fword(fword),

34 .out_port_from_the_pio_1(sine_en),

35 .out_port_from_the_pio_2(tri_en),

36 .out_port_from_the_pio_3(too_en)

37 }

38

39 test_sine u1

40 {

41 .clk(clk_50),

42 .reset(reset),

43 .en(sine_en)

44 }

45 endmodule

2 {

3 //////////////////// Clock Input ////////////////////

4 clk_50, // 50 MHz

5 //////////////////// Reset ////////////////////

6 reset,

7 //////////////////// en ////////////////////

8 en,

9 //////////////////// selecet ////////////////////

10 wave1,

11 wave2,

12 wave3,

13 }

14

15

16 input clk_50;

17 input reset;

18 output en;

19 output [7:0] fword; //frequancy

20 output wave1; //zheng

21 output wave2; //sanjiao

22 output wave3; //juchibo

23

24 wire sine_en;

25 wire tri_en;

26 wire too_en;

27

28 nios u0

29 {

30 .clk(clk_50),

31 .reset_n(reset),

32 .out_port_from_the_en(en),

33 .out_port_from_the_fword(fword),

34 .out_port_from_the_pio_1(sine_en),

35 .out_port_from_the_pio_2(tri_en),

36 .out_port_from_the_pio_3(too_en)

37 }

38

39 test_sine u1

40 {

41 .clk(clk_50),

42 .reset(reset),

43 .en(sine_en)

44 }

45 endmodule

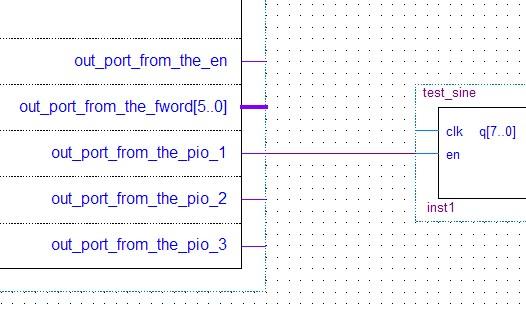

还有这张图片,这是元件在QuartusII中被做成symbol后的图片

对照程序看,这里就比较明白了。

程序24行 wire sine_en;

34行 .out_port_from_the_pio_1(sine_en),

43行 .en(sine_en)

这三句句就是图中那根连接out_port_from_pio_1和en的之间的连线。24行定义这条导线,在34行调用这导线的一端,在43行调用导线的另一端,这样就把一根线连了起来。

下面还有assign的赋值大致有两种:

一种是直接赋值,assign DRAM_DQ = 16'hffff;

这样就相当于给DRAM_DQ这个16位的数据赋值为0xFFFF。这样就和单片机C语言中的全局量赋值一个道理。

还有一种是类型转换。 如:assign I2C_SCLK = I2C_SCLKm;

这句就相当于是把I2C_SCLK和I2C_SCLKm等同起来;I2C_SCLK定义的是output,而I2C_SCLKm则是wire,这样就好像C语言的类型转换吧。

说着说着感觉有点乱了。。。我去在搞搞明白。明天一定把这东西完成。