一. 有意为之

Verilog是个大杂烩,这是有意而为之。

Verilog IEEE Std(1364-2005)的摘要中写道:

提取一下:

Verilog HDL的意在:for use in all phases of the creation of electronic systems.

Verilog HDL既是人读的,又是机读的。

Verilog HDL支持:

- the development,

- verification,

- synthesis,

- and testing of hardware designs;

- the communication of hardware design data;

- and the maintenance, modification, and procurement of hardware.

顺带对文档的使用者也提出了要求:

- the implementors of tools supporting the language;

- advanced users of the language.

意思是如果你不是资深玩家就别看这规范了,先修炼基本功。

二. 可综合

Verilog HDL志向远大,支持硬件设计的全流程。所以Verilog为每一个阶段都提供了一个功能子集。虽然都基于Verilog基本语法,但是用途却不尽相同。

比如developing of hardware design亦即hardware modeling的子集与verification的子集不同。hardware modeling的代码写出来是要综合成物理硬件的,而verification的代码只是用来做验证,并不需要硬件对应。所以验证的子集相较建模的子集就更加灵活,只需要EDA支持即可。

这也是可综合的意思。

换句话说,如果使用Verilog HDL hardware modeling的子集进行建模,则不需要太多考虑可综合问题(非绝对)。

实际使用中可能还是要考虑,因为EDA支持的建模子集是Verilog的建模子集的子集。

三. 建模的抽象层次

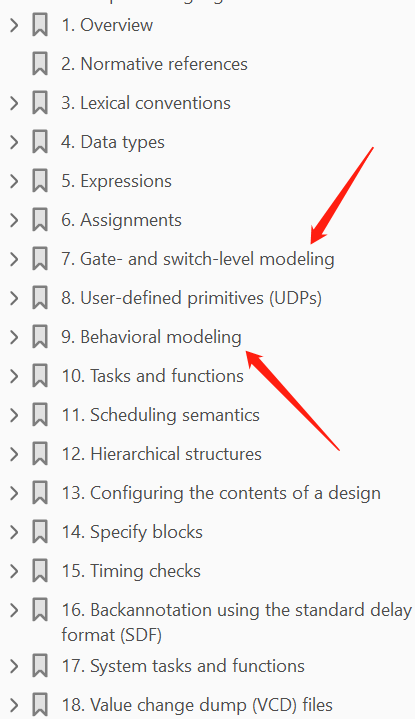

Verilog对建模的支持在两个大的抽象层次:门开关层(GSL)和寄存器传输层(RTL)。

还有数据流、结构建模和行为建模的区分。

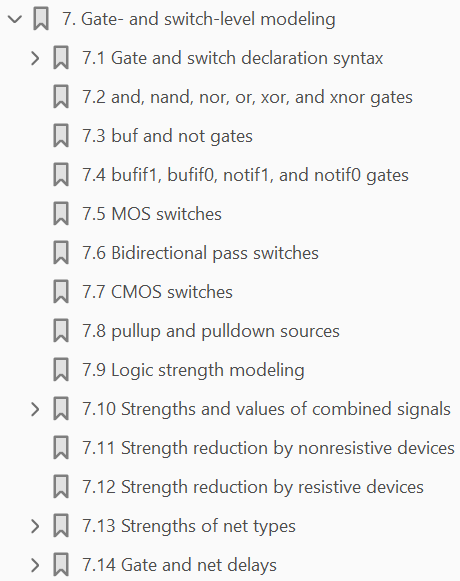

四. GSL

门和开关层(GSL)是最低层次亦即最接近硬件层次的抽象层次。这一层使用四值逻辑,也可以对信号强度和delay进行建模。

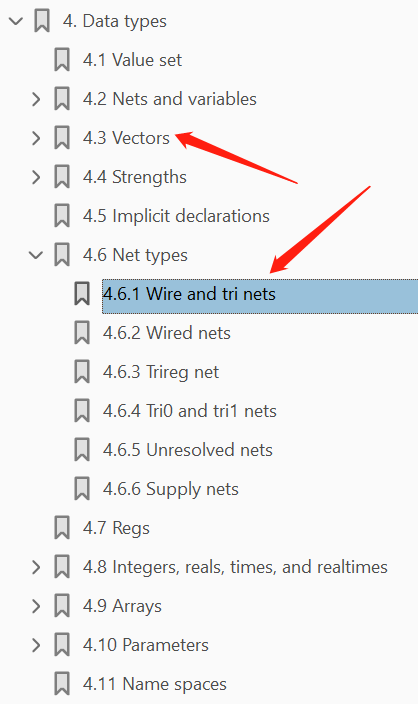

严格意义上讲,GSL建模能使用的数据类型只有wire,一根线或者一排线。能使用的节点是各种switches和gates。

五. RTL

因为线只能传输,而不能暂存,所以只能实现比较简单的功能。没有历史记忆则只能重复历史逻辑,不停重复历史逻辑则无法顺利完成功能,至少是及其低效的。

寄存器提供了暂存的功能,也为更复杂功能建模提供了可能。RTL:Register Transfer Level,基于寄存器进行值传递的抽象层次和建模层次。

严格意义上讲,RTL建模无需使用wire,全部使用reg类型即可。reg类型可以理解为一个可以暂存值的抽象的Data Type. 如果不需要存值,则综合时直接使用wire直接连通即可。

不过,实际使用中,为了准确,多wire和reg混用,毕竟这也是建模时为数不多的工具之一,也提升建模人员的控制力。

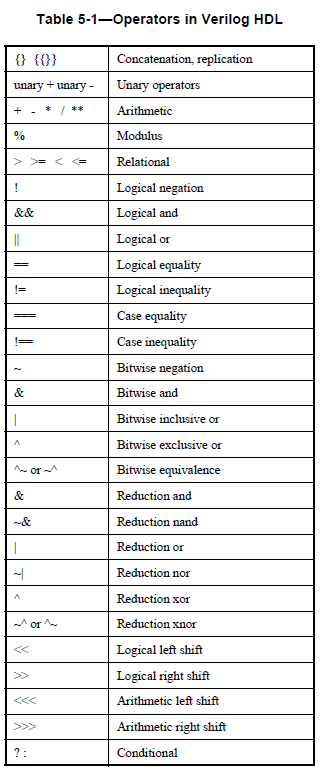

这一层可以使用很多操作符(operator):

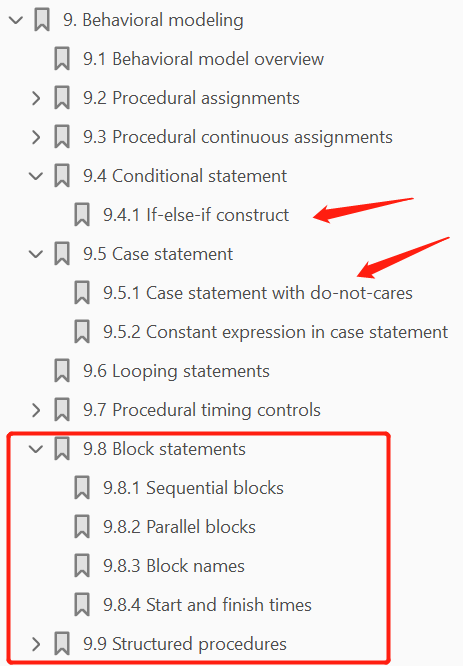

支持行为建模和使用结构化的形式组织模型的各个部分:

PS. Loop statements不是用来建模的。

六. 更高层次

更高层次的建模,如事务层、算法层、系统层,Verilog没有提供支持。

七. 总结

这里主要体现的是把Verilog划分成不同的子集的想法。

Verilog HDL支持其他阶段hardware design的子集,我暂时不掌握,见谅。

Verilog作为Language的各个子集的划分,需要advanced user才能掌握。这是一个缺点。

而基于现有语言的建模库(Library)则不存在这个问题,因为不同的阶段使用不同的库,分的比较清楚。