参考来源

https://china.xilinx.com/video/hardware/i-and-o-planning-overview.html

前言

我Win10系统上的Xilinx Platform Studio打不开,无奈之下换用Vivado。这篇粗略地介绍Vivado创建FPGA工程的流程

使用Vivado

新建工程

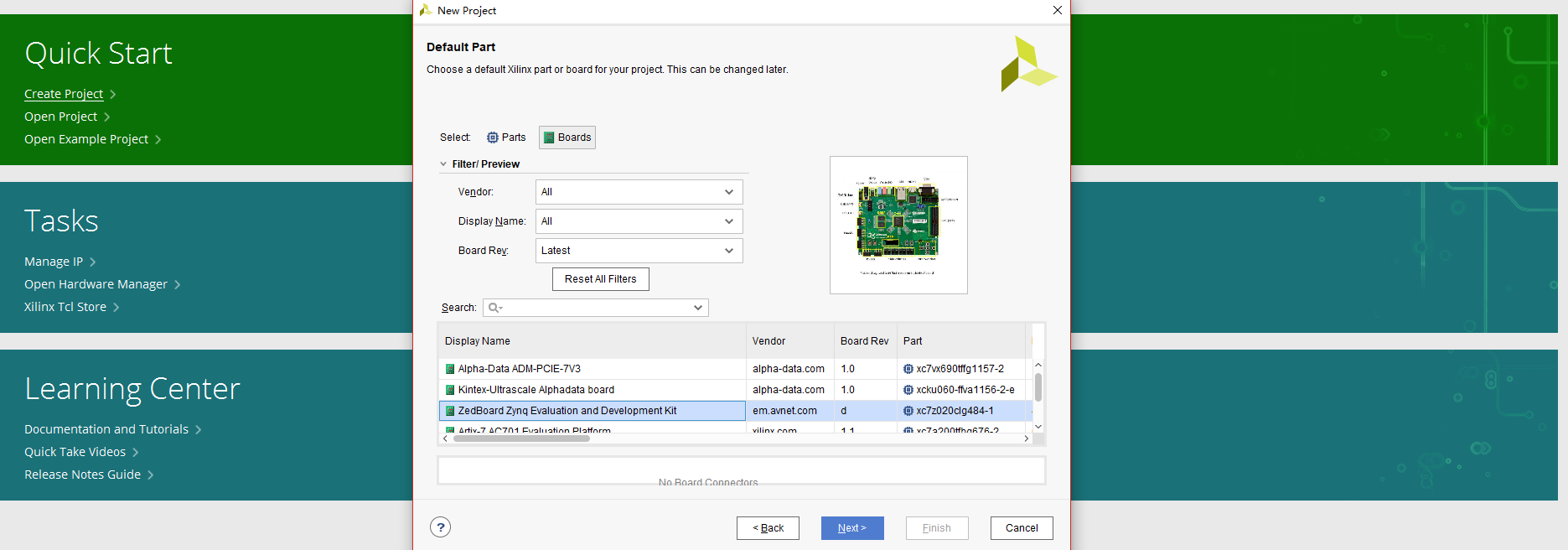

打开vivado,点New Project然后Create a New Vivado Project点next再填写工程名、工程路径点next

在Project Type选择 RTL 工程,单击 NEXT

选择板子,我的是Zedboard,然后next-finish

设计输入

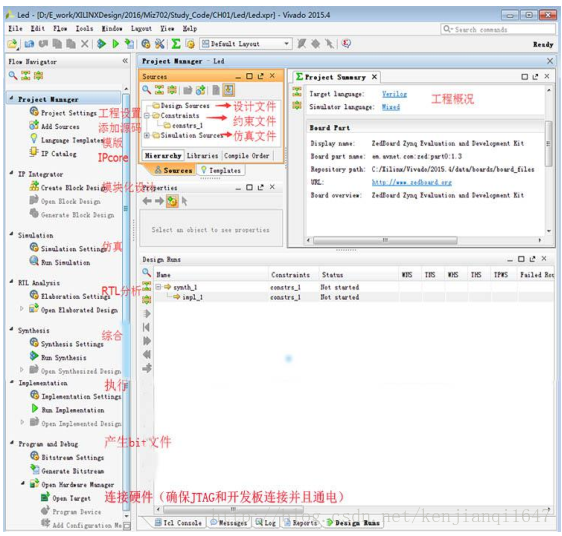

界面如下,图片来源https://blog.csdn.net/kenjianqi1647/article/details/79199657

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

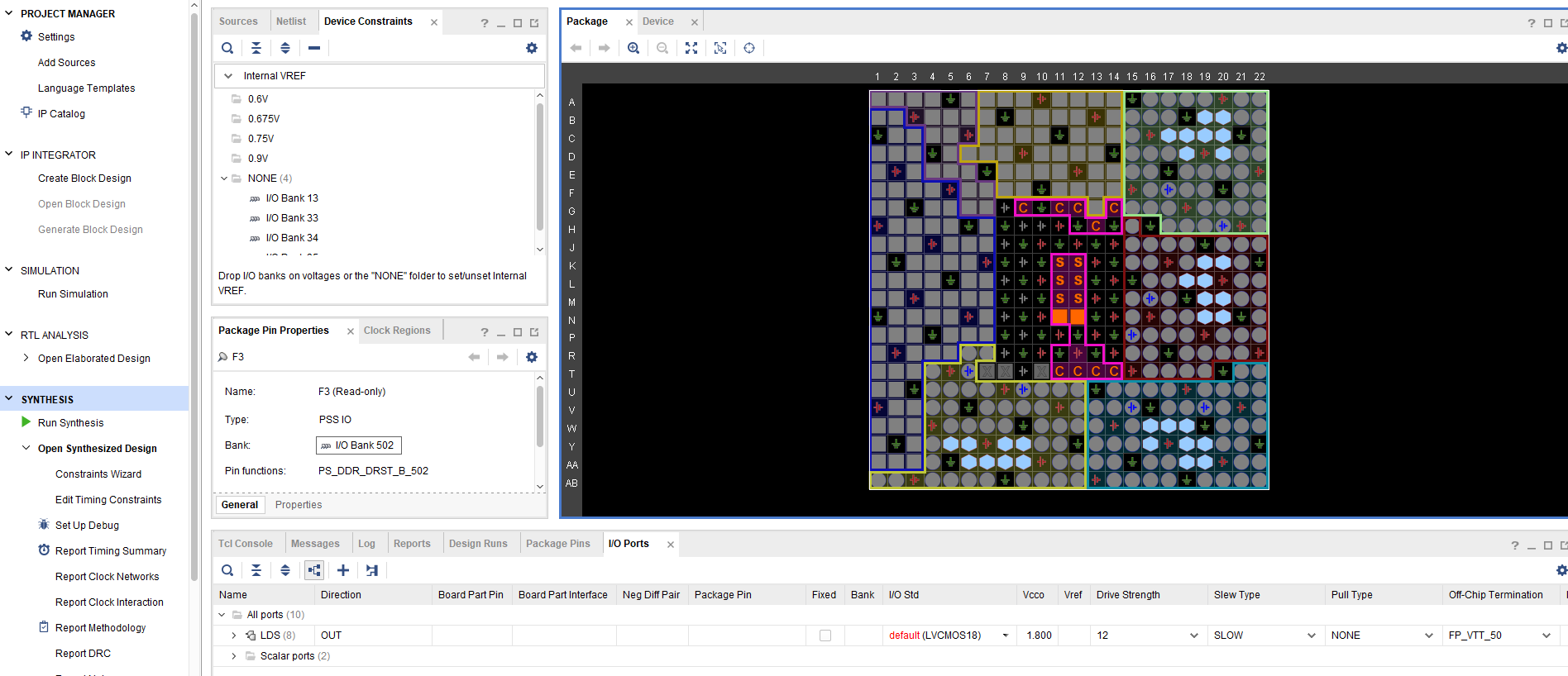

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

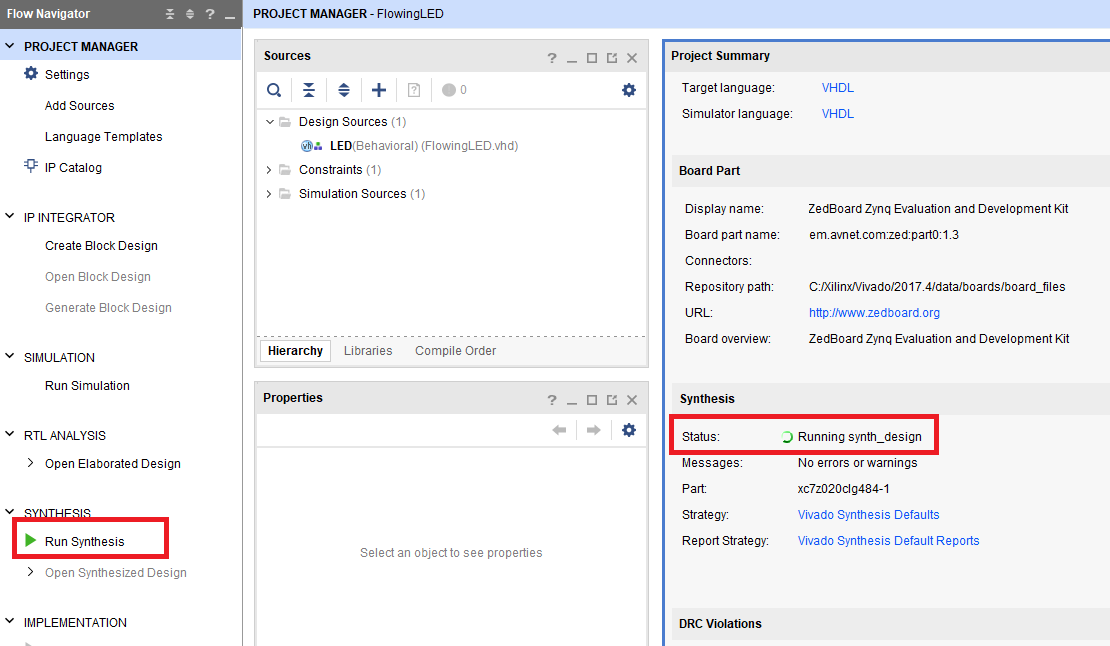

设计综合

设计综合过程会完成语法检查,编译,映射等步骤

点击Run Synthesis,可以在Project Summary 查看状态

综合完毕后

点击open synthesized design打开synthesized design,此时点击菜单栏的window-I/O ports 即可规划管脚。点击菜单栏Layout-I/O planning打开Package

设计实现

点击Run Implementation,完成后点击Generate Bitstream,生成比特文件

下载执行

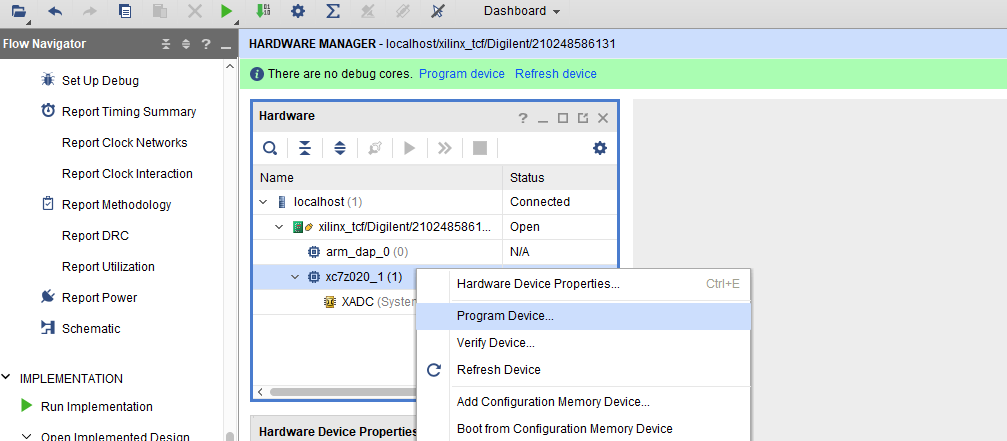

将开发板通电并连接到电脑,点击Hardware Manager ,在fpga芯片上右键program,

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

使用ISE

流程:创建工程、设计输入、引脚约束、设计综合、设计实现、生成比特文件、下载执行

开发工具

ISE

硬件连接

Zedboard 的8个LED共阴极,置高电平点亮

100MHz时钟源接入GCLK引脚

BTNU按钮按下时是高电平,可用于高电平复位

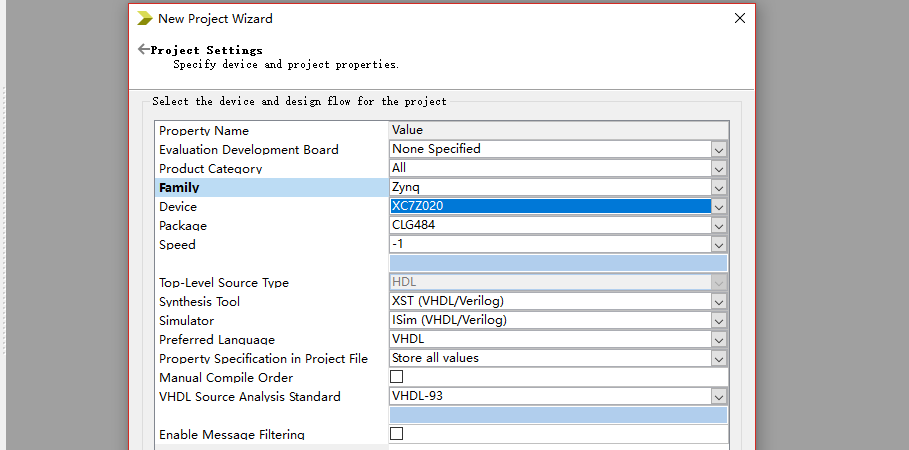

器件属性配置

代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Flowing LED

-- 先分频再移位

entity LED is

port(

GCLK,BTNU:in std_logic;

LDS:out std_logic_vector(7 downto 0)

);

end LED;

architecture Behavioral of LED is

-- 计数

signal count:std_logic_vector(25 downto 0);

signal clk_temp:std_logic;

signal LDS_temp:std_logic_vector(7 downto 0):="00000001";

begin

process(GCLK,BTNU)

--分频系数

variable N :std_logic_vector(25 downto 0):="10111110101111000010000000";

begin

if BTNU='1' then

count<="00000000000000000000000001";

clk_temp<='1';

elsif (GCLK'EVENT and GCLK='1')then

if (count=N)then

count<="00000000000000000000000001";

clk_temp<='1';

else

count<=count+1;

clk_temp<='0';

end if;

end if;

end process;

--得到的clk_temp为2Hz,占空比1/50000000

process(clk_temp,BTNU)

begin

if BTNU='1' then

LDS_temp<="00000001";

elsif (clk_temp'EVENT and clk_temp='1')then

LDS_temp(0)<=LDS_temp(7);

LDS_temp(7 downto 1)<=LDS_temp(6 downto 0);

end if;

end process;

LDS<=LDS_temp;

end Behavioral;

引脚约束

NET "BTNU" IOSTANDARD = LVCMOS18;

NET "GCLK" IOSTANDARD = LVCMOS33;

NET "BTNU" LOC = T18;

NET "GCLK" LOC = Y9;

NET "LDS[7]" LOC = U14;

NET "LDS[6]" LOC = U19;

NET "LDS[5]" LOC = W22;

NET "LDS[4]" LOC = V22;

NET "LDS[3]" LOC = U21;

NET "LDS[2]" LOC = U22;

NET "LDS[0]" LOC = T22;

NET "LDS[1]" LOC = T21;

# PlanAhead Generated IO constraints

NET "LDS[7]" IOSTANDARD = LVCMOS33;

NET "LDS[6]" IOSTANDARD = LVCMOS33;

NET "LDS[5]" IOSTANDARD = LVCMOS33;

NET "LDS[4]" IOSTANDARD = LVCMOS33;

NET "LDS[3]" IOSTANDARD = LVCMOS33;

NET "LDS[2]" IOSTANDARD = LVCMOS33;

NET "LDS[1]" IOSTANDARD = LVCMOS33;

NET "LDS[0]" IOSTANDARD = LVCMOS33;

现象

8个LED从右到左流水点亮,如果按BTNU从LED0开始重新流水点亮

关于逻辑部分

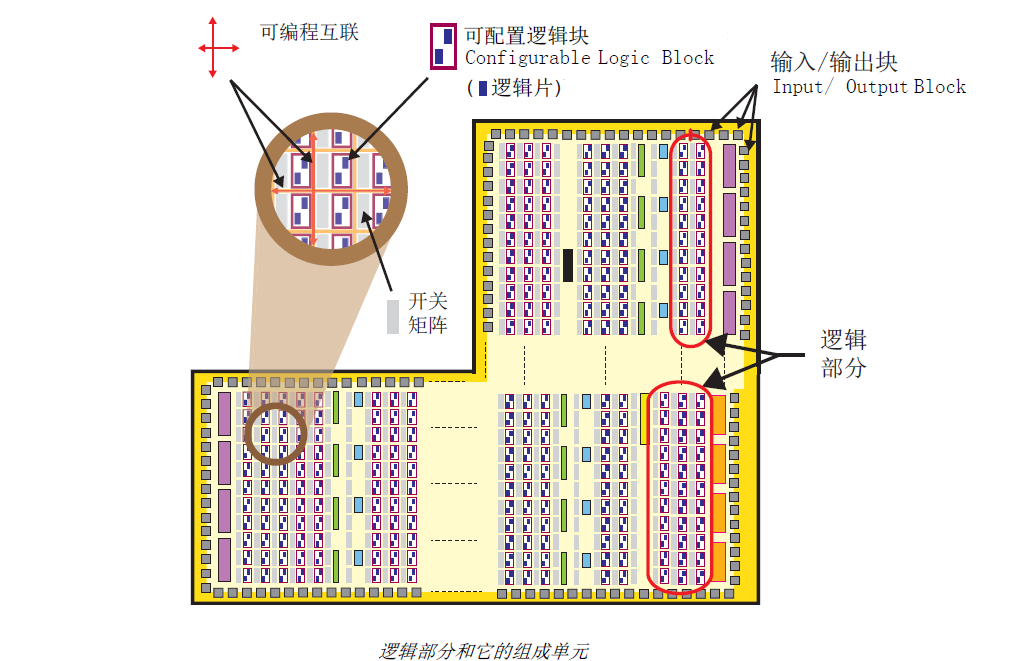

通用FPGA逻辑部分如下所示

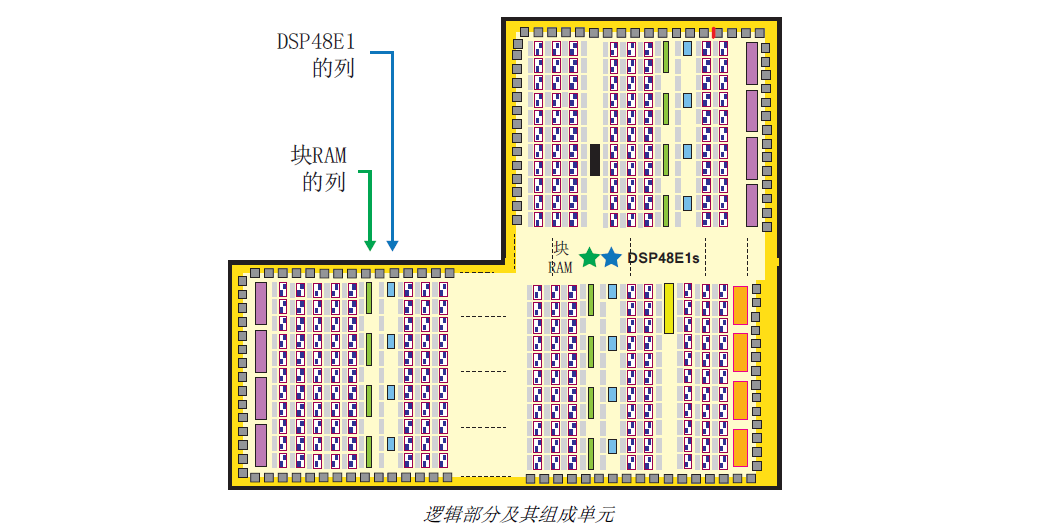

zynq的PL部分的特殊资源包括满足密集存储的块RAM和用于高速算术的DSP48E1。当然逻辑资源也可以用来搭建RAM,但是块RAM是经过优化的,使用很小的物理空间就可以存储大量数据;逻辑资源的查找表(LUT)也可以用来算术运算,但是会占用很多逻辑资源,DSP48E1是专用于长字长信号的高速算术运算的逻辑块。

其他硬IP部件

- GTX收发器实现与独立的外部芯片的连接,支持PCI Express和SATA等接口

- XDAC块,两个独立的12位ADC,采样速率达到1Msps,使用PS控制

- 独立的时钟

- JTAG实现配置和调试