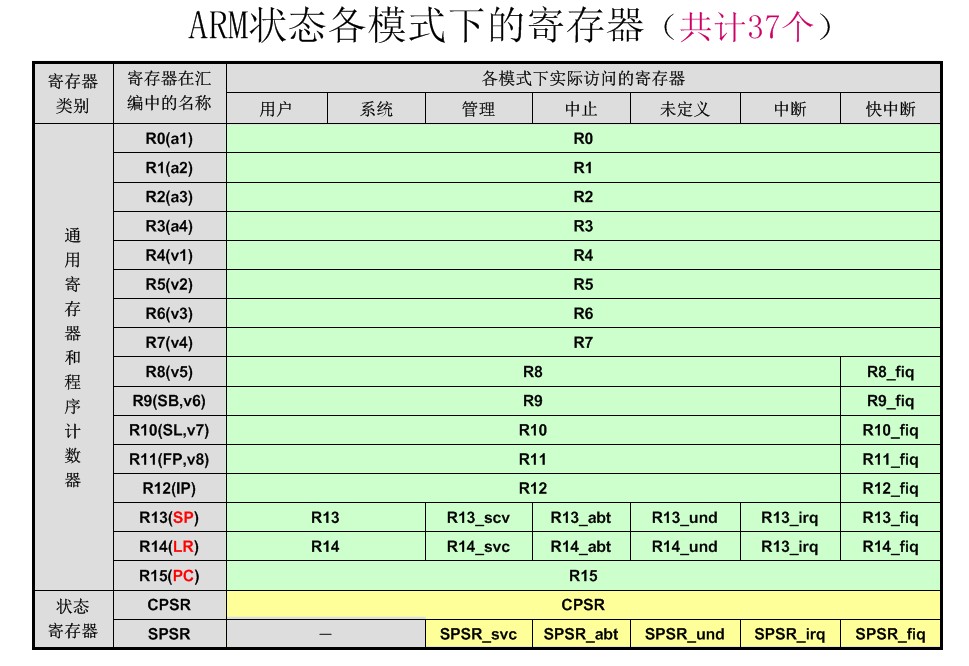

ARM7内核寄存器分布

ARM7TDMI-S内核共37个寄存器。

R0—R7,通用寄存器,共8个。

R8—R12,除快中断有自己寄存器(Rx_fiq),其他模式共用,共10个。

R13,栈指针寄存器。用户、系统共用外,其他模式有独立寄存器,共6个。

R14,连接寄存器。当程序跳转(BL)、异常模式时,用于保存当前PC值。同上,共6个。

R15,程序计数寄存器,所有模式共用,1个。

CPSR,程序状态寄存器,同上,1个。

SPSR,程序状态保存寄存器,用户、系统模式没有。其他模式各自独立。进入异常模式时,用于保存用户、系统模式的CPSR。共5个。

以上为ARM7内核中的37个寄存器。

CPSR位分布

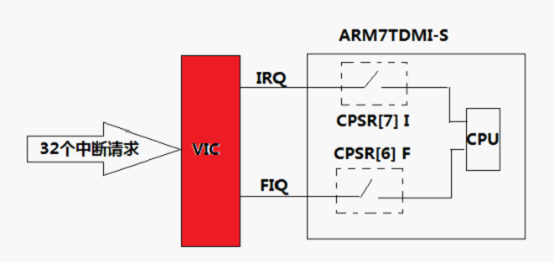

ARM7,LPC2000系列,中断向量控制器。

ARM内核本身只有FRQ和IRQ,2条中断输入信号线。为了扩展中断源,ARM7采用中断向量控制器管理中断源,从而扩展出来了32个中断请求输入。中断向量控制器属于内核外设!

CPU的IRQ和FIQ中断由CPSR的6、7位控制,1禁止,0使能。

中断分类,FIQ、向量IRQ、非向量IRQ,优先级依次降低。

①FIQ一般只分配一个,不建议分配两个以上。

②向量IRQ最多可分配16个相爱难过来那个IRQ中断。

③非向量IRQ中断只有一个。

基于VIC的每一个中断都有一个VIC通道号。LPC2000系列不足32个中断。

|

模块 |

标志 |

VIC通道号 |

|

WTD |

看门狗 |

0 |

|

—— |

(保留给软件) |

1 |

|

ARM内核 |

EmbeddedICE,Rx |

2 |

|

ARM内核 |

EmbeddedICE,Tx |

3 |

|

Timer0 |

匹配、捕获 |

4 |

|

Timer1 |

匹配、捕获 |

5 |

|

UART0 |

|

6 |

|

UART1 |

|

7 |

|

PWM0 |

|

8 |

|

I²C0 |

SI(状态改变) |

9 |

|

SPI0 |

|

10 |

|

SPI1 |

|

11 |

|

PLL |

PLL锁定(PLOCK) |

12 |

|

RTC |

计数器增加 |

13 |

|

系统控制 |

EINT0 |

14 |

|

EINT1 |

15 |

|

|

EINT2 |

16 |

|

|

EINT3 |

17 |

|

|

A/D0 |

|

18 |

|

I²C1 |

SI(状态改变) |

19 |

|

BOD |

掉电检测 |

20 |

VIC用若干寄存器配置管理32个中断源

一,VIC控制配置寄存器

中断选择寄存器 VICIntSelect

中断使能寄存器 VICIntEnable

中断使能清零寄存器 VICIntEnclr

三个寄存器的32位对应相应32中断源,实现32个中断的配置。

VICIntSelect 相应位置 1 相应中断分配 FIQ中断,置 0 分配 IRQ中断

VICIntEnable 相应位置 1 使能分配的相应的中断,置 0 无效

VICIntEnClr 相应位置 1 禁止分配的相应的中断,置 0 无效

二,VIC地址寄存器

向量地址寄存器 VICVectAddr 保存向量IRQ中断地址

默认向量地址寄存器 VICDefVectAddr 保存非向量IRQ中断地址

向量地址寄存器0—15 VICVectAddr X 保存向量IRQ中断地址

向量控制寄存器0—15 VICVectCntl X

VICVectCntl X相应位描述

|

位 |

31:6 |

5 |

4:0 |

|

功能 |

保留 |

向量IRQ使能 |

分配给该向量IRQ通道的中断请求或软件中断的编号 |

VICVectCntl X bit5 置1使能中断,置0并不会禁止中断本身,中断只是变为分享量的形式。ARM7硬件不支持中断嵌套。

向量IRQ通道有0—15共16个,优先级依次降低。

VICVectCntl X 4:0 bit 存放 中断通道号(基于VIC的编号0—32),中断编号放入较高向量IRQ通道控制寄存器,该中断就是向量IRQ中断中优先级较高的!

例如:VICVectCntl0 = 0x20 | 4; 定时器0分配为向量IRQ通道0

三,状态寄存器

IRQ状态寄存器 VICIRQStatus 读取得到分配并使能为IRQ的中断状态

FIQ状态寄存器 VICFIQStatus 读取得到分配并使能为FIQ的中断状态

所有中断状态寄存器 VICRawIntr 读取得到所有中断状态

以上寄存器位分配,对应VIC通道号

读取,某位是 1 则代表该中断激活。