Modelsim,可以选型SE和XE两个版本。Modelsim XE可以直接被ISE调用,而Modelsim SE需要手动添加仿真库。但SE版和OEM版在功能和性能方面有较大差别,比如对于大家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSim XE为例,对于代码少于40000行的设计,ModelSim SE 比ModelSim XE要快10倍;对于代码超过40000行的设计,ModelSim SE要比ModelSim XE快近40倍。所以我还是选择了Modelsim SE,为此google了一下,找到了一个手动添加仿真库的方法,并轻松完成配置。详细步骤如下,有需要的兄弟们可以参考一下。

为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。所谓的标准库就是modelsim运行后,会自动加载的库。不过这方面我还不是很肯定。因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:

vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v

其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。这些就是我们要的库了。

第四步:按照上面的方法,编译另外两个库。所需要键入的命令分别如下:

vlog -work unisim_ver d:/Xilinx/verilog/src/unisims/*.v

vlog -work xilinxcorelib_ver d:/Xilinx/verilog/src/XilinxCoreLib/*.v

如果你想要编译的是VHDL的库,你需要建立的库分别是simprim,unisim和xilinxcorelib。这三个库所需要的modelsim指令分别如下:

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vcomponents.vhd

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_Vpackage.vhd

vcom –work simprim d:Xilinx/VHDL/src/simprims/simprim_VITAL.vhd

在ModelSim中添加Xilinx仿真库

说明:

l ModelSim一定要安装在不带空格的目录下,即不要安装在“Program Files”目录下。如作者是安装在D:softwaresModelsim目录下。

l ISE软件也最好安装在不带空格的目录下。

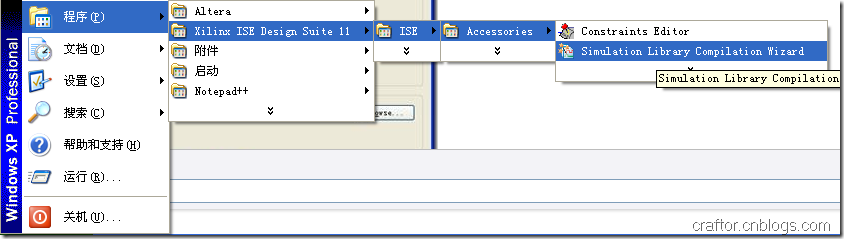

1、找到开始菜单->程序->Xilinx ISE Design Suite 11 -> ISE -> Accessories -> Simulation Library Compilation Wizard.

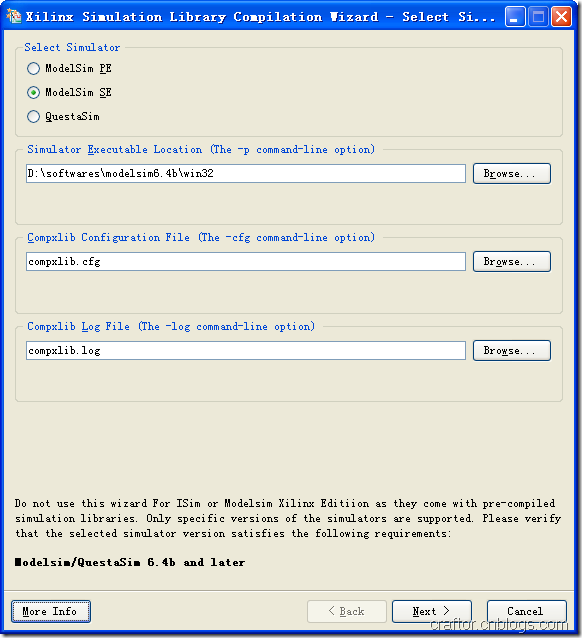

2、选定ModelSim的版本,以及指定ModelSim的安装路径。

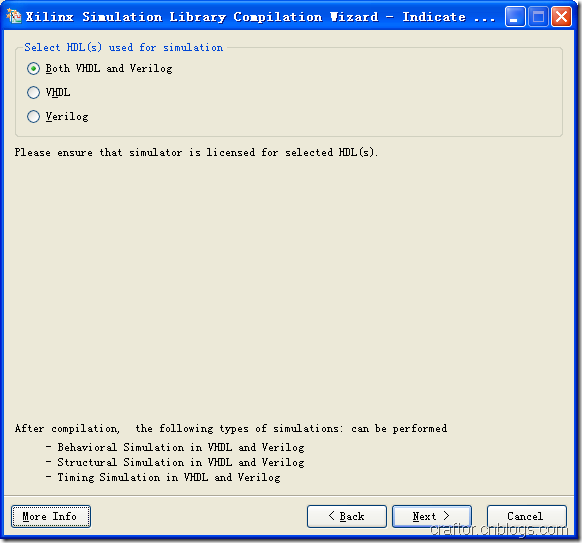

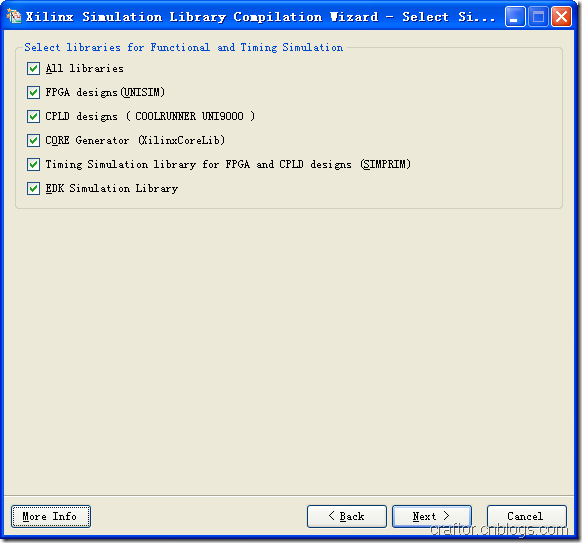

3、选择Both VHDL and Verilog。

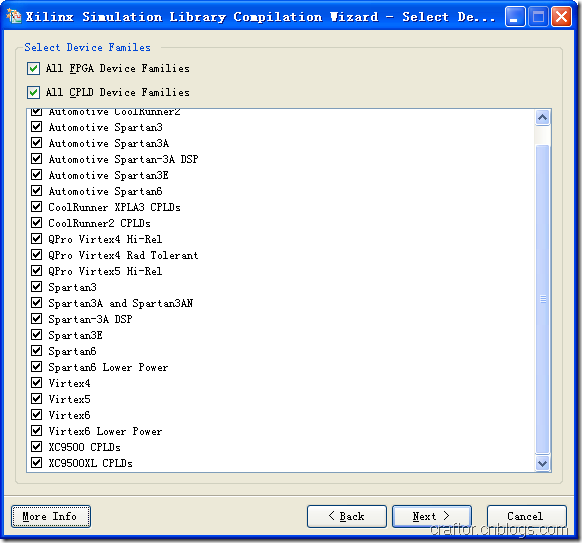

4、选择支持哪些系列的芯片,看自己需要增减。

5、默认选全上即可。

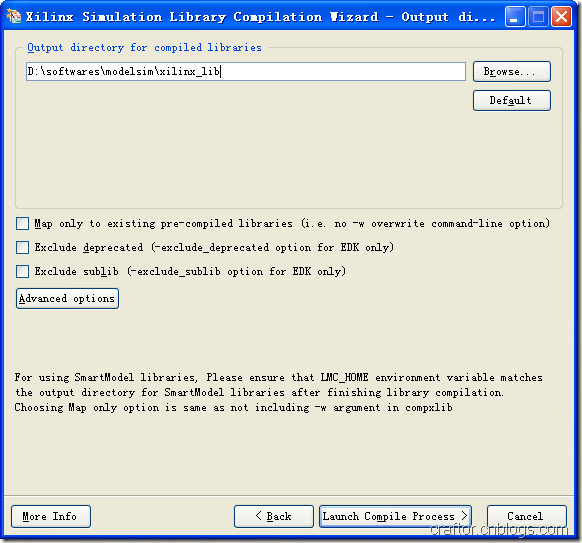

6、指定编译完后的库存放位置,这里作者在modelsim安装目录下新建了xilinx_lib的文件夹,并指定到这里。(注意不要指向带空格的路径)

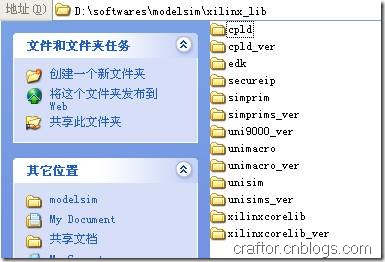

7、运行 Lauch Compile Process,即开始编译库文件,需要几十分钟。编译完成后应该在xilinx_lib目录下多出如下文件夹:

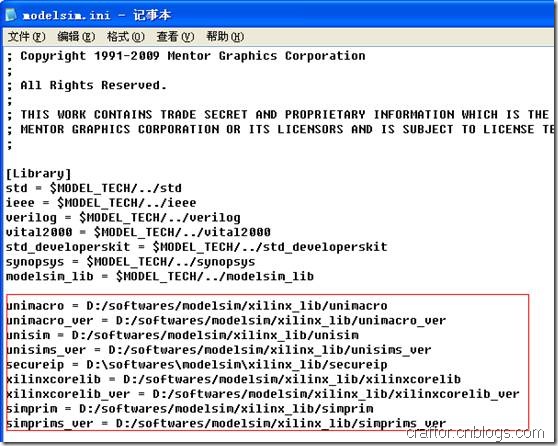

8、右键打开modelsim目录下的modelsim.ini文件,先将其“只读”属性去掉。然后用记事本打开。在[Library]下面添加如下代码,即之前编译好的Xilinx库的路径。

unimacro = D:/softwares/modelsim/xilinx_lib/unimacro

unimacro_ver = D:/softwares/modelsim/xilinx_lib/unimacro_ver

unisim = D:/softwares/modelsim/xilinx_lib/unisim

unisims_ver = D:/softwares/modelsim/xilinx_lib/unisims_ver

secureip = D:softwaresmodelsimxilinx_lib/secureip

xilinxcorelib = D:/softwares/modelsim/xilinx_lib/xilinxcorelib

xilinxcorelib_ver = D:/softwares/modelsim/xilinx_lib/xilinxcorelib_ver

simprim = D:/softwares/modelsim/xilinx_lib/simprim

simprims_ver = D:/softwares/modelsim/xilinx_lib/simprims_ver

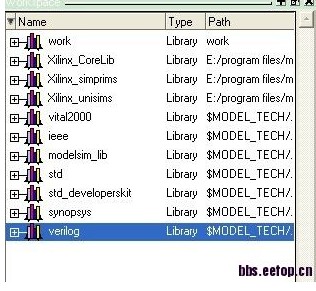

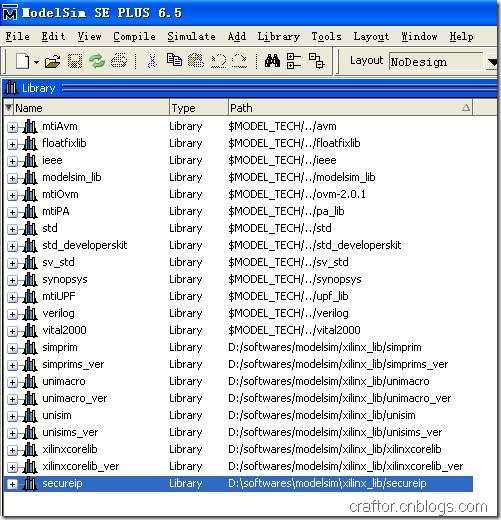

9、再次打开ModelSim,即可以看到Xilinx的库已经默认出现在了库列表里。以后仿真Xilinx的IP核时,就不用每次都添加库了。