材料

- STM32F407VET6

- 20M晶振

目标

- 配置成80M系统主频(这里进行了降频,由于项目需要,一般是配置成168M的)

步骤

-

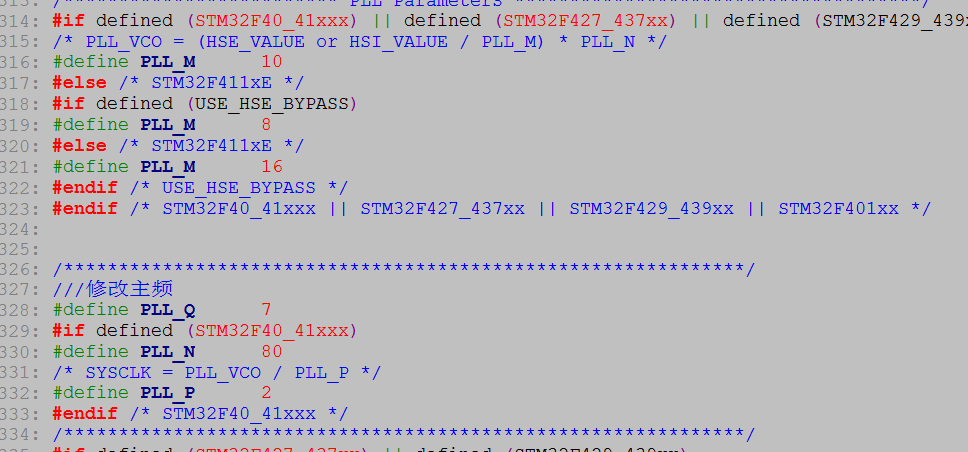

修改system_stm32f4xx.c文件,PLL_M=10,PLL_N=80,PLL_P=2

-

修改Stm32f4xx.h文件,将HSE_VALUE改成晶振频率20000000

参考315,331行

PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N

SYSCLK = PLL_VCO / PLL_P

这里我们 HSE_VALUE=20M(晶振频率),PLL_M=10,PLL_N=80,PLL_P=2,代入上面公式可以计算得SYSCLK=80M

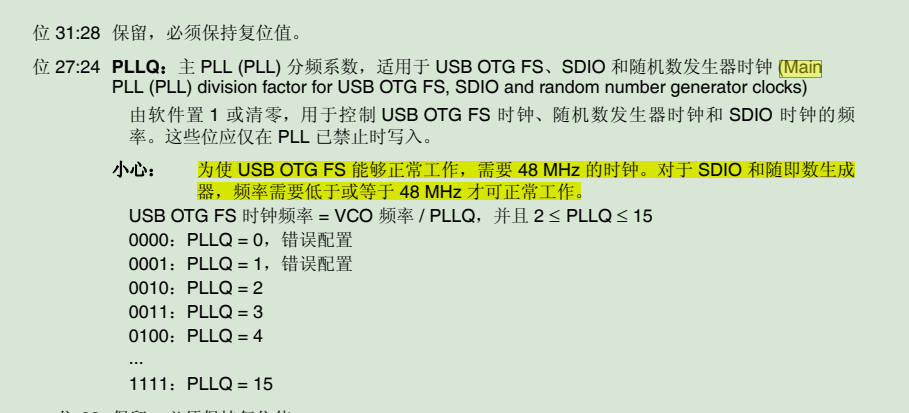

再记录一下PLL_Q,他是用来配置USB OTG FS, SDIO and RNG Clock时钟的,公式为USB OTG FS, SDIO and RNG Clock = PLL_VCO / PLLQ,因为我这个项目不用这几个外设,所以我就保持了默认7,如果要使用这几个外设,那么一定要注意,USB OTG FS的时钟频率手册明确说明了是需要配置成48M的

拿一个8M外部晶振,主频168M的工程举个栗子,他的配置如下

PLL_M=8,PLL_N=336,PLL_P=2,PLL_Q=7 USB OTG FS, SDIO and RNG Clock = 8/8*336/7 = 48M