verilog RTL code example

以下是学习verilog语法的例子

module divider(// synchronous logic block

input clk_in,

output clk_out,

input rst_n,

// combinational logic block

input a,

output b);

reg period;

reg [7:0] clk_cnt;

wire [7:0] cnt;

wire c;

reg b_out;

assign cnt = {1'b1, clk_cnt[6:0]};

assign c = clk_cnt == 7 ? 1'b1 : 1'b0;

always @(posedge clk_in or negedge rst_n)

begin : clkcnt_gen

if(!rst_n)

clk_cnt <= 0;

else if(clk_cnt == 7)

clk_cnt <= 0;

else

clk_cnt <= clk_cnt + 1;

end

always @(posedge clk_in or negedge rst_n)

begin : period_gen

if(!rst_n)

period <= 0;

else if(clk_cnt <= 3)

period <= 1;

else

period <= 0;

end

assign clk_out = period;

always @(*)

begin

b_out = ~a;

end

assign b = b_out;

endmodule

verilog testbench 编写

`timescale 1ns/1ns

module tb;

reg clk_in;

reg rst_n;

wire clk_out;

reg a_in;

wire b_out;

initial

begin

clk_in = 0;

repeat (20) #10 clk_in = ~clk_in;

end

initial

begin

rst_n = 0;

#10;

rst_n = 1;

end

initial

begin

a_in = 0;

#10 a_in = 1;

#10 a_in = 0;

end

divider D1(

.clk_in(clk_in),

.clk_out(clk_out),

.rst_n(rst_n),

.a(a_in),

.b(b_out)

);

endmodule

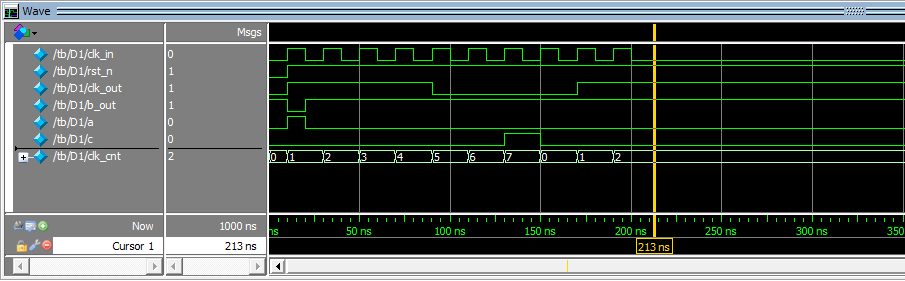

waveform 展示