一、血缘

AMBA: Advanced Microcontroller Bus Architecture 高级处理器总线架构

AHB: Advanced High-performance Bus 高级高性能总线

ASB: Advanced System Bus 高级系统总线

APB: Advanced Peripheral Bus 高级外围总线

AXI: Advanced eXtendable Interface 高级可拓展接口

二、APB状态图

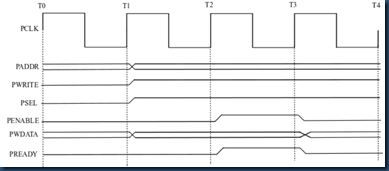

三、读写操作时序图

(1)写

T1: Idle; T2: Setup; T3: Enable/Access.

T1: PSEL=0, PENABLE=0;

T2: PSEL=1, PENABLE=0; PADDR/PWDATA ready; PWRITE=1;

T3: PSEL=1, PENABLE=1; PREADY=1; 如果T3之后没有数据传输需求,状态应回到Idle;否则跳到Setup,此时 PREADY 信号从高跳到低。

注:网上的描述不明确。 相关操作还是需要看协议。

PREADY是来自Slave的信号,用于指示Slave在何时能完成传输。

由图可见,其实在T2时刻,所需数据已经准备好,此时是否已经可以把数据采走呢?答案是肯定的。事实上,由于PENABLE为0时PREADY可以是任意值,一些接口可以一直把PREADY拉高、同时在2个周期内完成传输,如此仍然会与APB兼容。

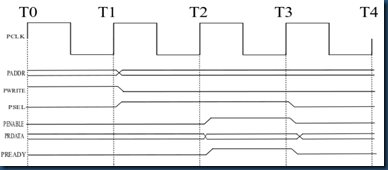

(2)读