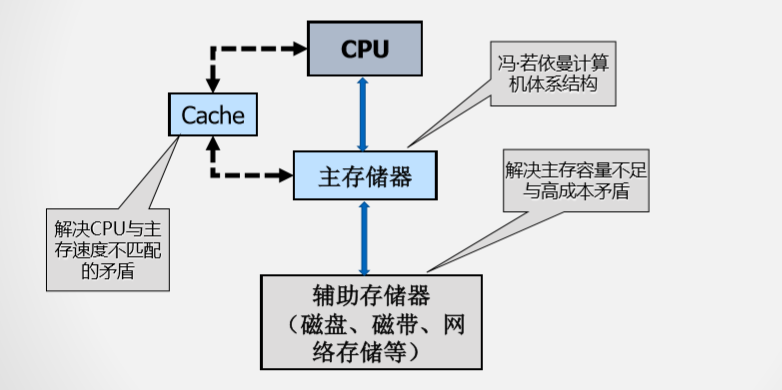

1、基本存储体系

cpu负责程序控制

主存负责存储程序

1)输入设备将程序与数据写入内存

2)cpu取指令

3)cpu执行指令期间读数据

4)cpu写回运算结果

5)输出设备输出结果

2、主存速度慢的原因

1)主存增速与cpu增速不同步

2)指令执行期间多次访问存储器

3、主存容量不足的原因

1)存在制约主存容量的技术因素,由cpu、主板等相关技术指标确定。

2)应用对主存的需求不断扩大

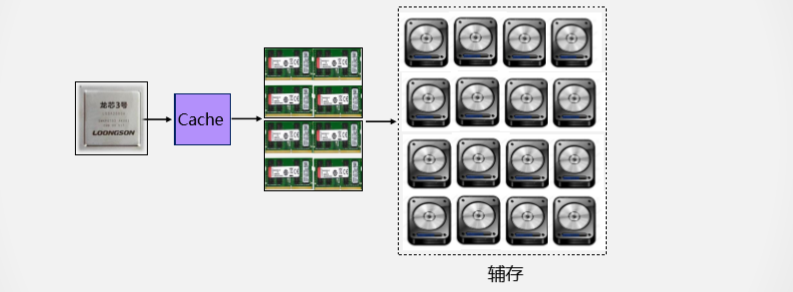

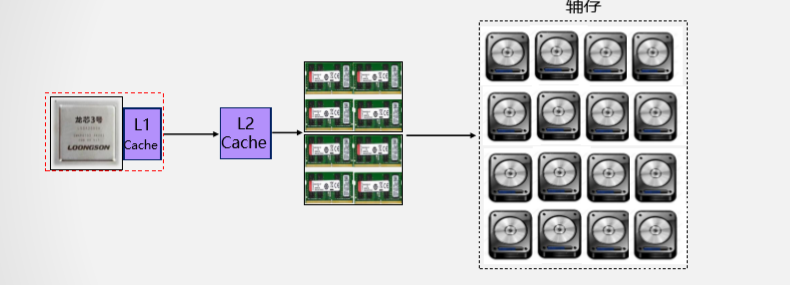

4、存储体系的层次化结构

cpu访问到的存储体系具有Cache的速度,辅存的容量和价格

L1 Cache集成在cpu中,分数据Cache和指令Cache

早期L2 Cache在主板上或与cpu集成在同一电路板上。随着工艺的提高L2 Cache被集成在cpu内核中,部分数据Cache和指令Cache。

哈佛结构是一种将指令储存和数据储存分开的存储器结构,可支持:数据和指令并行储存、指令预取,提高处理器的执行效率;另外,指令和数据可有不同的数据宽度,

5、存储体系层次化结构的理论基础

局部性原理

*时间局部性

现在被访问的信息2在不久的将来还将再次被访问

时间局部性的程序结构体现:循环结构

*空间局部性

现在访问信息2 ,下一次访问2附近的信息

空间局部性的程序结构体现:顺序结构