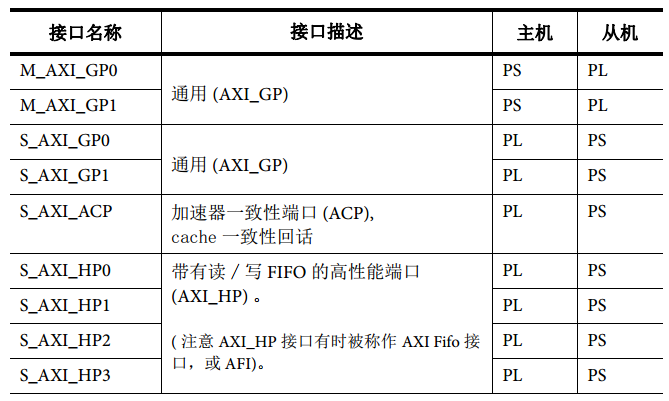

PS-PL之间的AXI 接口分为三种:

• 通用 AXI(General Purpose AXI) — 一条 32 位数据总线,适合 PL 和 PS 之间的中低速通信。接口是透传的不带缓冲。总共有四个通用接口:两个 PS 做主机,另两个 PL 做主机。

• 加速器一致性端口(Accelerator Coherency Port) — 在 PL 和 APU 内的 SCU之间的单个异步连接,总线宽度为 64 位。这个端口用来实现 APU cache 和 PL的单元之间的一致性。PL 是做主机的。

• 高性能端口(High Performance Ports) — 四个高性能 AXI 接口,带有 FIFO缓冲来提供 “ 批量 ” 读写操作,并支持 PL 和 PS 中的存储器单元的高速率通信。数据宽度是 32 或 64 位,在所有四个接口中 PL 都是做主机的。

即:

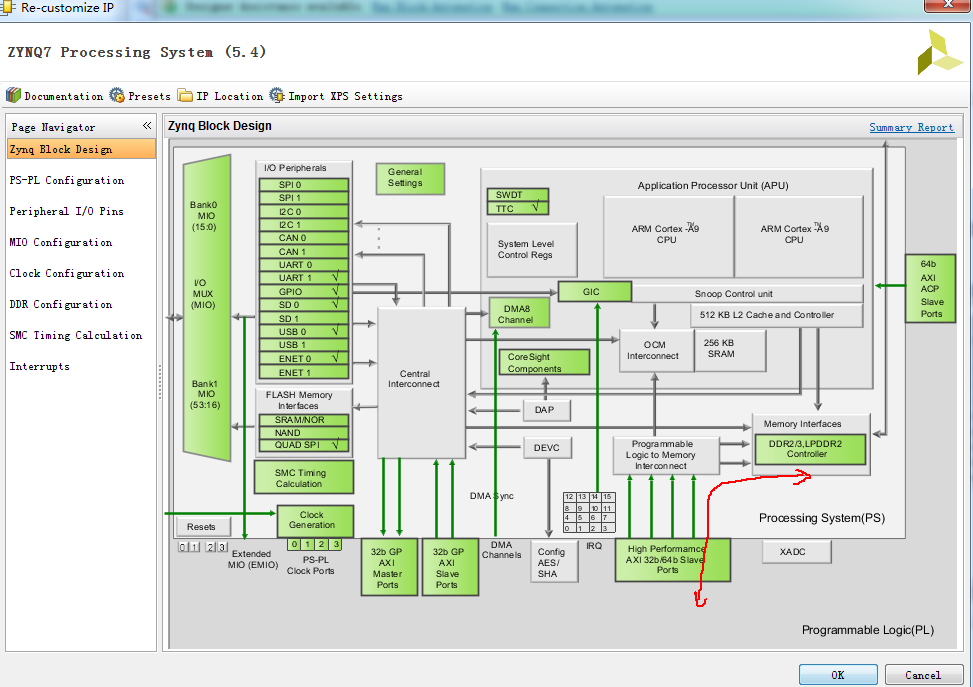

从VIVADO的配置中,我们可以看出DDR控制器是通过四个AXI HP连接到PL端的。

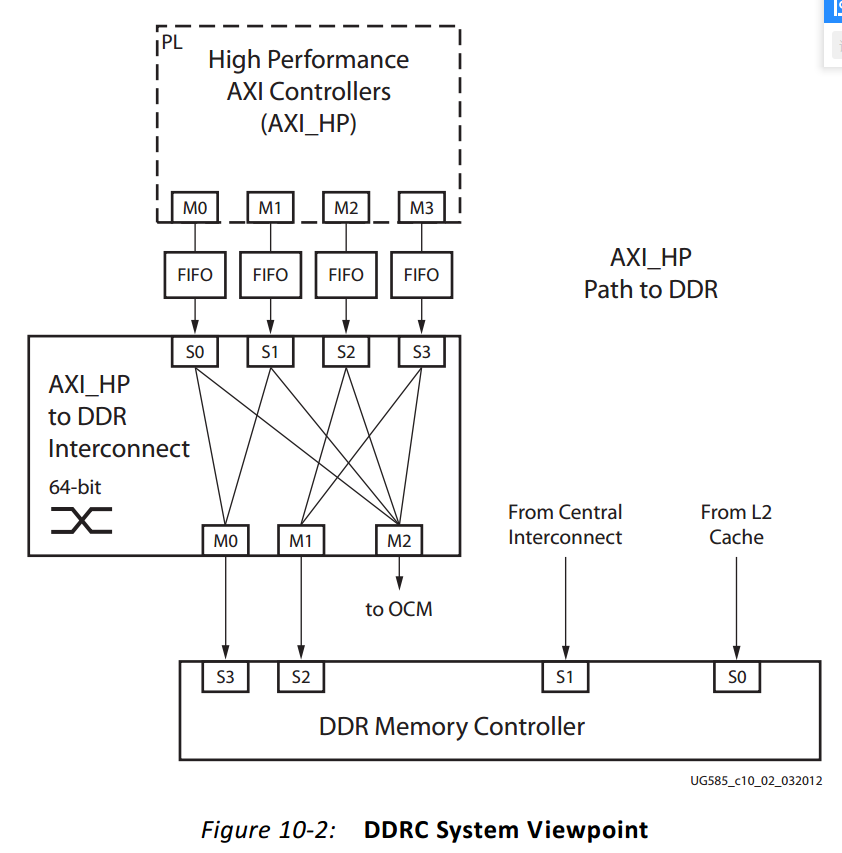

再去查阅UG585,里面有一段话是这么说的:

The four AXI_HP interfaces are multiplexed down, in pairs, and are connected to ports 2 and 3 as

shown in Figure 10-2. These ports are commonly configured for high bandwidth traffic. The path

from these four interfaces to the DDR include two ports on the DDR memory port arbiter. The

interconnect switch arbitrates back-and-forth between each of the two ports. Read and write

channels operate separately.

大致意思就是说四路HP总线通过M2连接到了片上存储器(貌似是256KB的SRAM,这个与我们现在要做的工作无关,在这里提一嘴是因为后来涉及到对DDR寻址的时候,有一部分地址是连到了这个OCM的,这一部分地址对我们暂时没用,需要避开),另外这四路总线的0和1又通过M0连到了DDR的S3端口,2和3通过M1连到了DDR的S2端口。一般推荐的方法是,同时使用HP0和HP2(或者HP1和HP3),总之就是要使用分离的通道来操作DDR,以获取较高的性能。

从上图我们也可以看到,每个 AXI_HP 接口里都有用做读写通信的 FIFO 缓冲器。在某些 Xilinx 文档中,AXI_HP接口也被叫做 AXI FIFO 接口 (AFI),来表明它们的缓冲能力。AXI_HP 接口的特性包括:

• 32 或 64 位数据主机接口,每个端口可以独立编程。

• 对于未对齐的 32 位传输,可以自动扩展传输尺寸从 32 位到 64 位。

• 写命令的可编程的阈值。

• 对于所有的 PL-PS 接口的异步时钟频率跨域。

• 读写 FIFO。

• 命令和通信数据 FIFO 填充程度计数是 PL 可见的。