`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Engineer: connor jiao // Create Date: 14:02 2020/6/10 // Design Name: // Module Name: // Function : //请基于f = 100Hz的Clock设计一个数字时钟,用Verilog实现以下功能 //1、产生时、分、秒的计时 //2、可通过3个按键来设置时、分、秒值 // Revision 0.01 - File Created // Additional Comments: ////////////////////////////////////////////////////////////////////////////////// module clock( input clk , input rst_n , input hour_set, input [4:0] hour_set_value , input minute_set, input [5:0] minute_set_value , input second_set , input [5:0] second_set_value , output [5:0] second_out , output [5:0] minute_out , output [4:0] hour_out ); reg [5:0] second_reg ; reg [5:0] minute_reg ; reg [4:0] hour_reg ; always@(posedge clk or negedge rst_n ) begin if(!rst_n) begin second_reg <= 0 ; end else if(second_set) second_reg <= second_set_value ; else if(second_reg == 59) second_reg <= 0; else second_reg <= second_reg +1 ; end always@(posedge clk or negedge rst_n ) begin if(!rst_n) begin minute_reg <= 0 ; end else if(minute_set) minute_reg <= minute_set_value ; else if(minute_reg == 59 && second_reg == 59) minute_reg <= 0; else if(second_reg == 59) minute_reg <= minute_reg +1 ; end always@(posedge clk or negedge rst_n ) begin if(!rst_n) begin hour_reg <= 0 ; end else if(hour_set) hour_reg <= hour_set_value ; else if(hour_reg == 23 && minute_reg == 59 && second_reg == 59) hour_reg <= 0; else if(minute_reg == 59 && second_reg == 59 ) hour_reg <= hour_reg +1 ; end assign second_out = second_reg ; assign minute_out = minute_reg; assign hour_out = hour_reg; endmodule

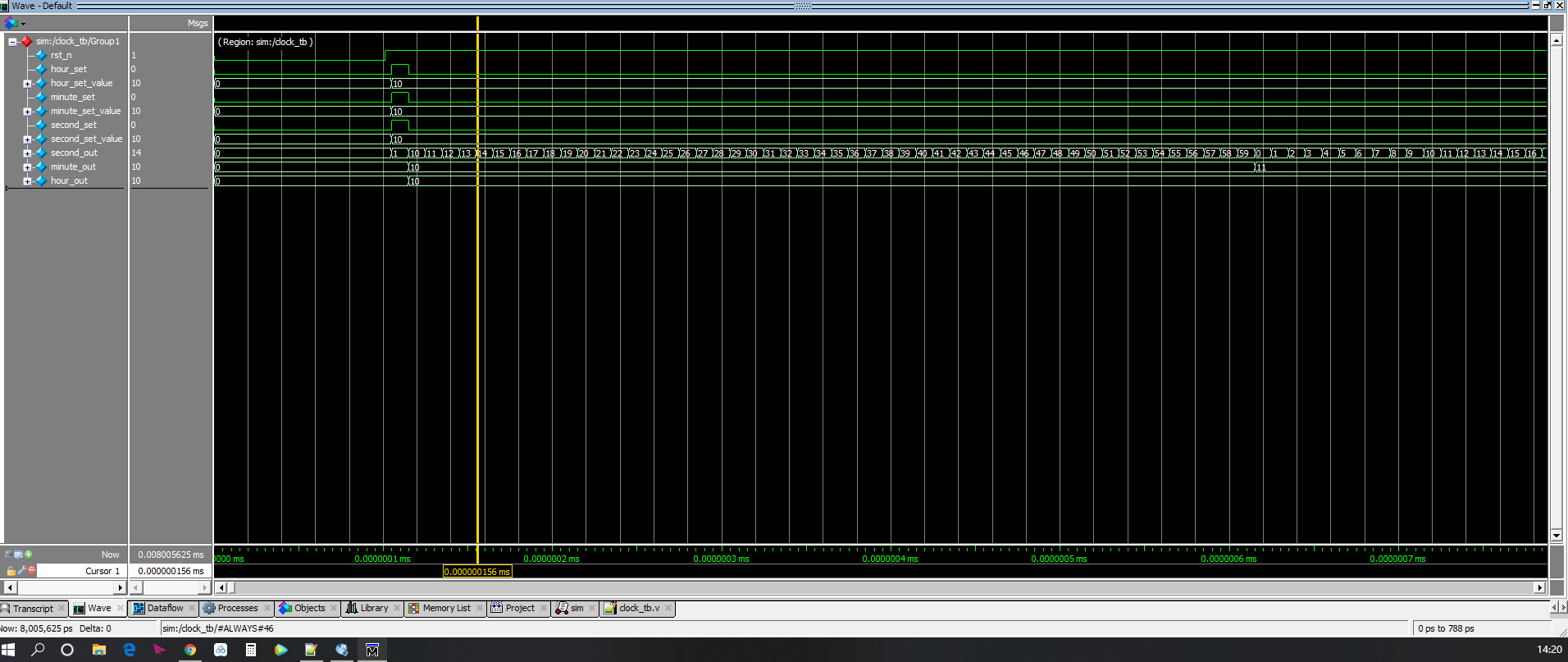

module clock_tb ; reg clk ; reg rst_n ; reg hour_set ; reg [4:0] hour_set_value ; reg minute_set ; reg [5:0]minute_set_value ; reg second_set ; reg [5:0]second_set_value ; wire [5:0] second_out ; wire [5:0] minute_out ; wire [4:0] hour_out ; initial begin clk = 0 ; rst_n = 0 ; hour_set = 0 ; hour_set_value = 0; minute_set = 0 ; minute_set_value = 0; second_set = 0 ; second_set_value = 0; #101 rst_n = 1 ; @(posedge clk ) begin hour_set = 1 ; hour_set_value= 10 ; minute_set = 1 ; minute_set_value = 10 ; second_set= 1 ; second_set_value = 10 ; end @(posedge clk ) begin hour_set = 0; //hour_set_value= 0 ; minute_set = 0 ; //minute_set_value = 0 ; second_set= 0 ; //second_set_value = 0 ; end end always #5 clk =~clk ; clock clock( .clk(clk) , .rst_n(rst_n) , .hour_set(hour_set) , .hour_set_value(hour_set_value) , .minute_set(minute_set), .minute_set_value(minute_set_value) , .second_set(second_set), .second_set_value(second_set_value) , .second_out(second_out) , .minute_out(minute_out) , .hour_out(hour_out) ); endmodule