本文转自:自己的微信公众号《集成电路设计及EDA教程》

前面的推文讲解了在Narrow Channel里面加Checkerboard形式的Hard Placement Blockage来解决里面出现的IR-drop问题。

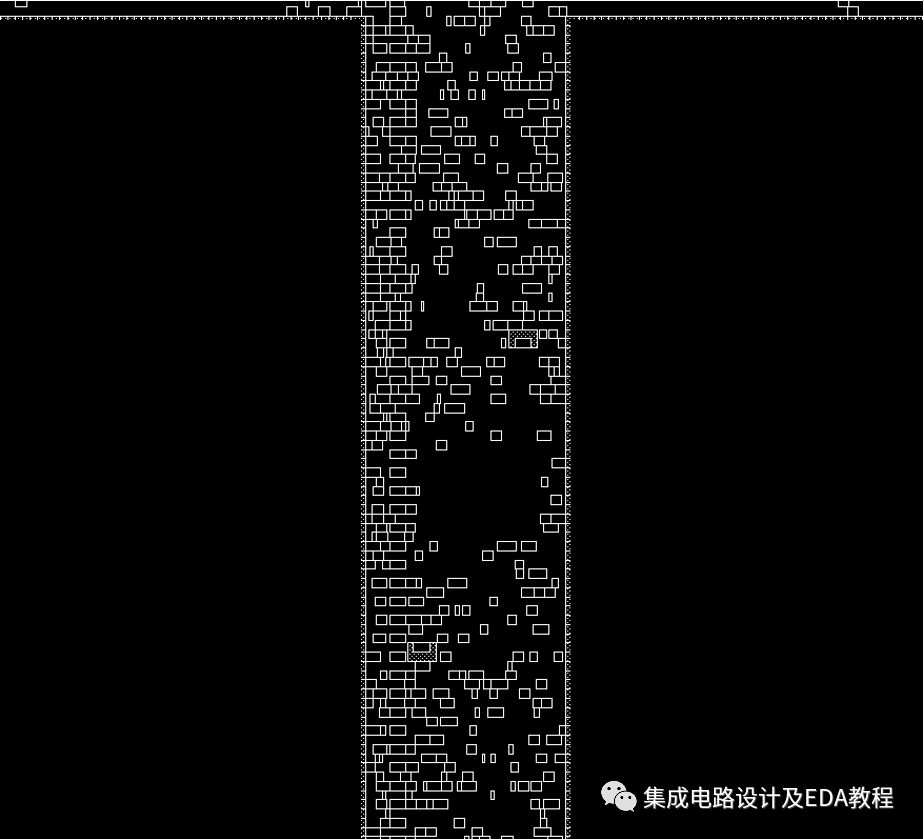

而这种加Checkerboard的方法比较麻烦,另外由于是棋盘式的摆放方案,因此在某些区域还是有可能有Cell堆在一起。下面是Narrow Channel里面加入Checkerboard形式的Hard Placement Blockage之后它们的分布情况:

下面是CTS之后Cell在Channel里面的摆放情况:

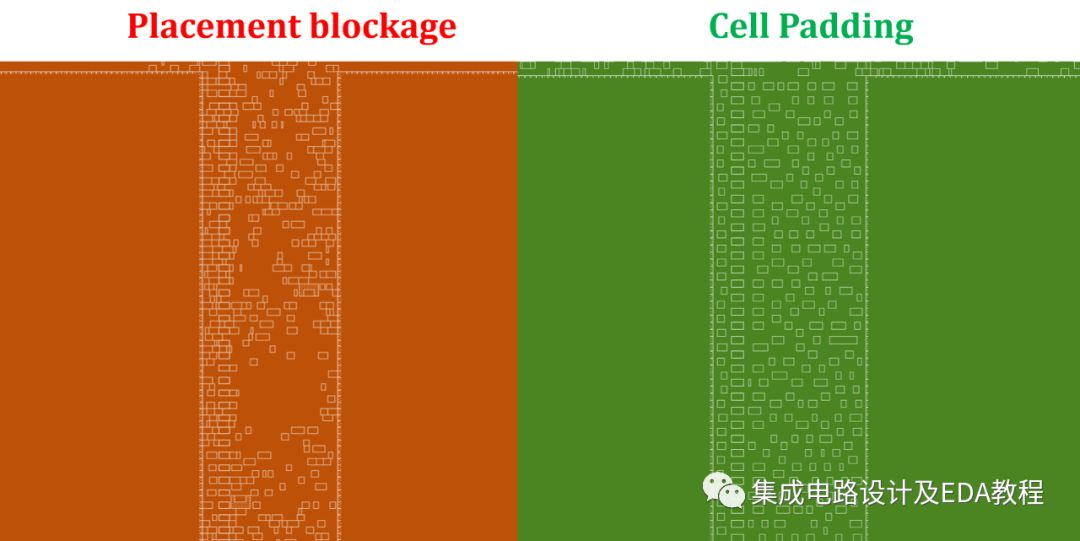

可以明显的看到,其实Cell摆放的不是特别的均匀,还是有局部团在一起,局部特别空的情况,因此可以大胆猜测,这个Channel里面发生IR-drop的概率还是相对较高的(相对于下面的cell padding方案)。

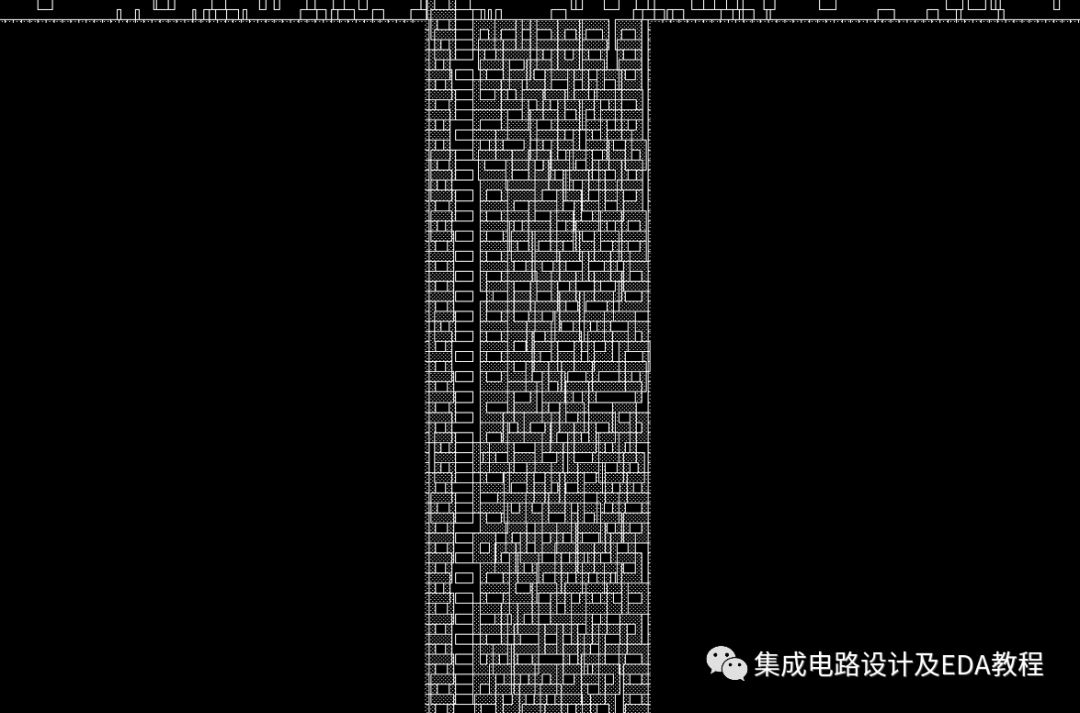

我们可以用脚本抓取Narrow Channel里面的所有Cell,然后给它们加上Cell Padding/Keepout margin。由于Place、CTS、Post-CTS阶段都会添加一些Cell,因此我们最好在每个阶段都给里面的Cell加上Padding,如果Legalize不下的话工具会将其legalize到Channel的外边。下面是该Channel里面给所有Cell加上Padding之后的显示Padding的效果:

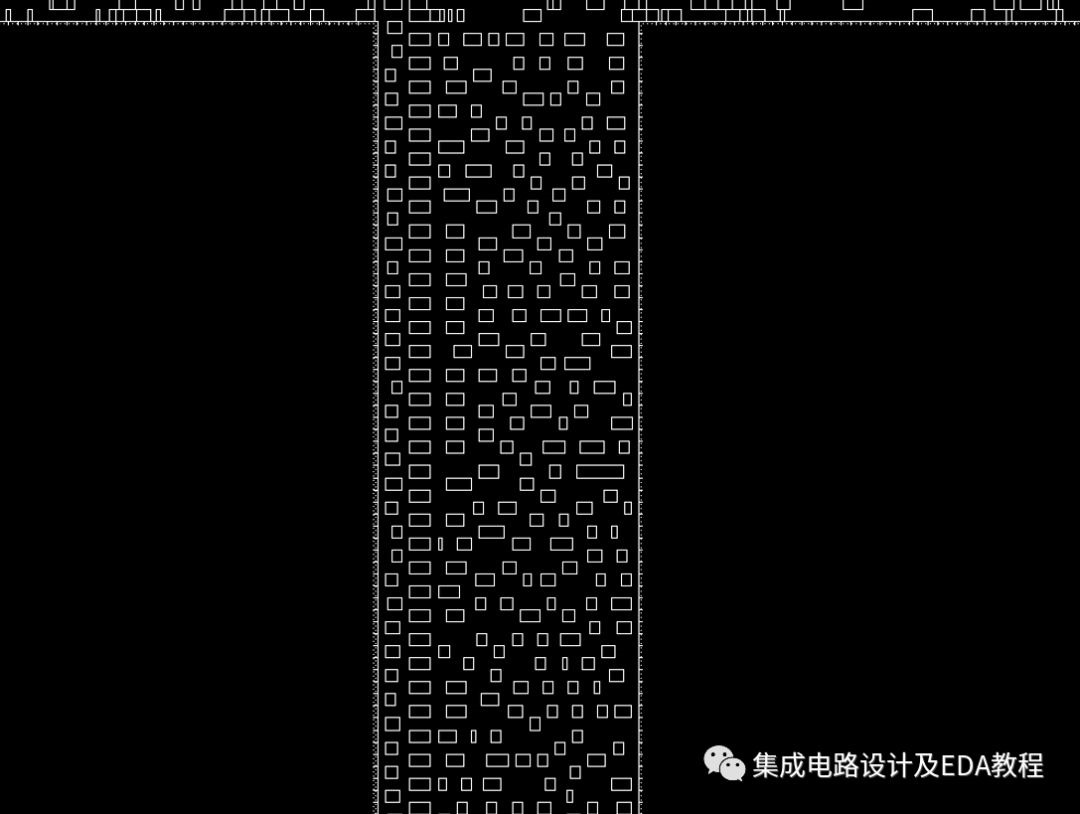

把padding关掉之后的Cell摆放效果:

可见Cell摆放的非常均匀,为了便于大家观察,我将两幅图放在一起对比一下:

相关推文

IR-drop问题的分析与修复(含脚本分享)(一):Partition boundary cells clustering

IR-drop问题的分析与修复(二):odd pg in Narrow

Channel

IR-drop问题的分析与修复(三):add checkerboard

placement blockage in Narrow